前次看了一下关于乘法器的Verilog代码,有几个当地一向很利诱,信任许多初学者看这段代码必定跟我最初相同,看得一头雾水,在网上也有一些网友发问,说这段代码欠好了解,今日小墨同学就和咱们一同来看一下这段代码,我会亲安闲草稿纸上演算,尽量把进程写的具体些,让更多的人了解乘法器的规划思路。

下面是一段16位乘法器的代码,咱们能够先阅读一下,之后我再做具体解说

module mux16(

clk,rst_n,

start,ain,bin,yout,done

);

input clk; //芯片的时钟信号。

input rst_n; //低电平复位、清零信号。界说为0表明芯片复位;界说为1表明复位信号无效。

input start; //芯片使能信号。界说为0表明信号无效;界说为1表明芯片读入输入管脚得乘数和被乘数,并将乘积复位清零。

input[15:0] ain; //输入a(被乘数),其数据位宽为16bit.

input[15:0] bin; //输入b(乘数),其数据位宽为16bit.

output[31:0] yout; //乘积输出,其数据位宽为32bit.

output done; //芯片输出标志信号。界说为1表明乘法运算完结.

reg[15:0] areg; //乘数a寄存器

reg[15:0] breg; //乘数b寄存器

reg[31:0] yout_r; //乘积寄存器

reg done_r;

reg[4:0] i; //移位次数寄存器

//————————————————

//数据位操控

always @(posedge clk or negedge rst_n)

if(!rst_n) i <= 5’d0;

else if(start && i < 5’d17) i <= i+1’b1;

else if(!start) i <= 5’d0;

//————————————————

//乘法运算完结标志信号发生

always @(posedge clk or negedge rst_n)

if(!rst_n) done_r <= 1’b0;

else if(i == 5’d16) done_r <= 1’b1; //乘法运算完结标志

else if(i == 5’d17) done_r <= 1’b0; //标志位吊销

assign done = done_r;

//————————————————

//专用寄存器进行移位累加运算

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

areg <= 16’h0000;

breg <= 16’h0000;

yout_r <= 32’h00000000;

end

else if(start) begin //发动运算

if(i == 5’d0) begin //锁存乘数、被乘数

areg <= ain;

breg <= bin;

end

else if(i > 5’d0 && i < 5’d16) begin

if(areg[i-1]) yout_r = {1’b0,yout[30:15]+breg,yout_r[14:1]}; //累加并移位

else yout_r <= yout_r>>1; //移位不累加

end

else if(i == 5’d16 && areg[15]) yout_r[31:16] <= yout_r[31:16]+breg; //累加不移位

end

end

assign yout = yout_r;

endmodule

下面是小墨同学对这段代码的了解

要了解这段代码,首先要弄了解几个点。

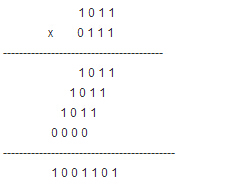

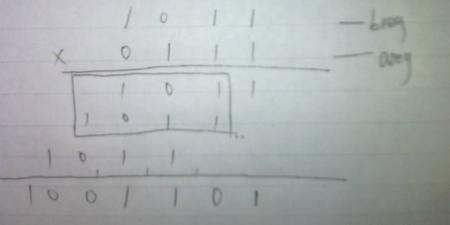

1、咱们一般写的十进制的乘法竖式,相同适用于二进制。下面咱们就以这个算式为例:1011 x 0111 =0100_1101。

2、两个16位的数相乘,结果是32位的,没有32位要在高位补零。

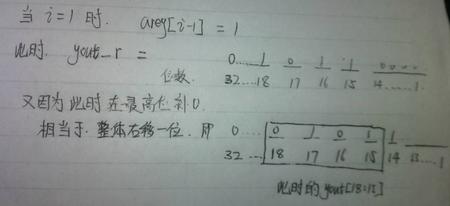

3、核算两个16位的数相乘需求移位15次。例如:

前三次核算是移位的,最终一次没有移位

4、两个16位的数相加,结果是17位的,不行17位最高位补零。 例如句子yout[30:15]+breg,结果是17位的。

知道了这些,咱们就开端看代码了

1、接口部分注释写的很清楚,这儿就不提了

2、数据位操控部分

always @(posedge clk or negedge rst_n)

if(!rst_n) i <= 5’d0;

else if(start && i < 5’d17) i <= i+1’b1;

else if(!start) i <= 5’d0;

当start为1时,芯片读入两个数,此刻开端计数,计数16次,乘法运算开端

3、乘法运算完结标志信号发生

always @(posedge clk or negedge rst_n)

if(!rst_n) done_r <= 1’b0;

else if(i == 5’d16) done_r <= 1’b1; //乘法运算完结标志

else if(i == 5’d17) done_r <= 1’b0; //标志位吊销

assign done = done_r;

这部分也很好了解

4、专用寄存器进行移位累加运算

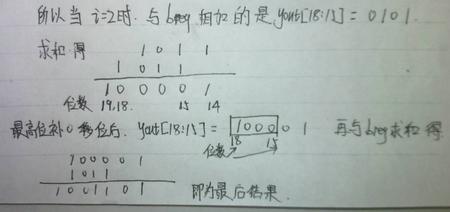

这儿为了简略,就用15到18位替代15到30位

以上部分是最主要的核算部分,其他当地相对来说还比较简略,例如当乘数某一位为0时,不必累加,直接右移,当i计数到16时,此刻就不必再移位了,能够直接用位数表明,直接累加即可。

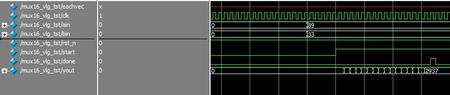

下面是仿真图