摘要 经过对单通道数字射频 存储器的原理和结构剖析,总结了单通道数字射频

存储器的原理和结构剖析,总结了单通道数字射频 存储器的优缺陷,并依据单通道数字射频

存储器的优缺陷,并依据单通道数字射频 存储结构,引进DSP模块规划了一种基带搅扰源,完结了对宽带信号的处理。

存储结构,引进DSP模块规划了一种基带搅扰源,完结了对宽带信号的处理。

关键词 数字射频 存储器;基带搅扰源;数字信号处理

存储器;基带搅扰源;数字信号处理

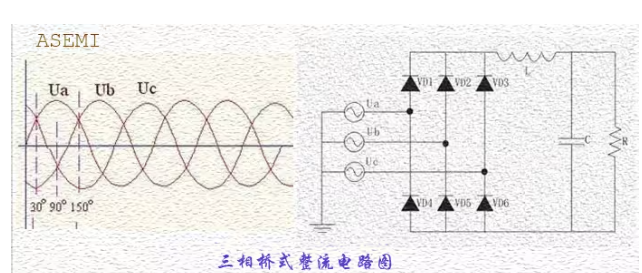

现代新式雷达遍及选用匹配接纳和相参信号处理技能,因而具有优异的方针检测、辨认和盯梢才能,一起具有杰出抗搅扰功用。运用传统噪声搅扰信号对相参雷达进行搅扰,因为搅扰信号不相参,能量使用率低、搅扰作用差,迫使噪声搅扰机过度前进发射功率,为体系工程完结带来困扰。因而,需求研讨相参搅扰技能以应对新体系雷达。

数字射频 存储器(Digital Radio Frequency Memory,DRFM)使用高速模数转化器材、高速数字逻辑器材进行采样、存储、处理雷达信号,能够发生相参搅扰信号。DRFM技能已成为现代搅扰技能的中心。

存储器(Digital Radio Frequency Memory,DRFM)使用高速模数转化器材、高速数字逻辑器材进行采样、存储、处理雷达信号,能够发生相参搅扰信号。DRFM技能已成为现代搅扰技能的中心。

1 单通道起伏量化DRFM的结构及特色

起伏量化是指使用ADC对输入信号起伏进行采样、量化、编码处理,得到数字信号。重构时,数字信号经DAC后输出模仿信号。起伏量化的采样频率和量化位数决议了重构信号的保真度。

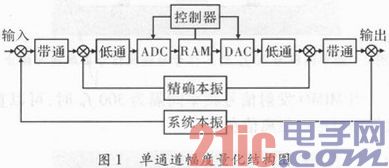

单通道起伏量化DRFM由一路ADC电路组成,其结构如图1所示。作业流程为:输入的射频信号与体系本振进行混频,经带通滤波下变频为中频信号;中频信号与准确本振混频、滤波后,得到基带模仿信号;ADC在采样时钟操控下,完结模数转化,输出数字信号存储到RAM中;在转发进程中,读出数据经DAC、低通滤波后,重构为基带模仿信号;此信号与体系本振混频后,上变频为射频搅扰信号。

假定下变频后输出信号的频率规模为[f0-△B/2,f0+△B/2],为按捺上变频和下变频的高次交调,其中心频率f0与带宽△B之间须满意

2(f0-△B/2)>f0+△B/2 (1)

即

f0>3△B/2 (2)

依据采样理论,采样时钟的频率应满意

fc>2(f0+△B/2)=2f0+△B>4△B (3)

由式(3)可知,单通道起伏量化的采样率应该大于输入信号带宽的4倍。因而单通道起伏量化即使有结构简略、不存在通道幅相不一致问题的长处,但因为ADC器材的约束,存在体系瞬时带宽较小,难以处理宽带信号的缺陷。

2 依据单通道DRFM的搅扰源规划

为处理宽带信号处理问题而发生的正交双通道DRFM存在幅相要求严厉、调试困难的特色,为规划者添加了作业量。跟着技能的前进,现在ADC器材的功用有了大幅前进,为选用单通道DRFM处理宽带信号供给了或许。

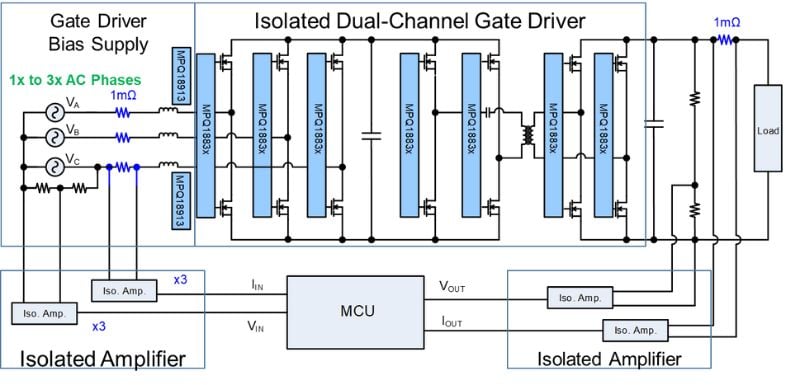

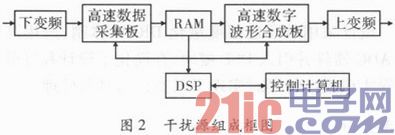

基带搅扰源首要完结对基带信号的收集存储、处理剖析与基带搅扰信号的生成。包含上下变频模块、高速收集板、DSP数字信号处理板、操控核算机和高速数字波形组成器等部分。其组成框图如图2所示。

2.1 高速数据收集板

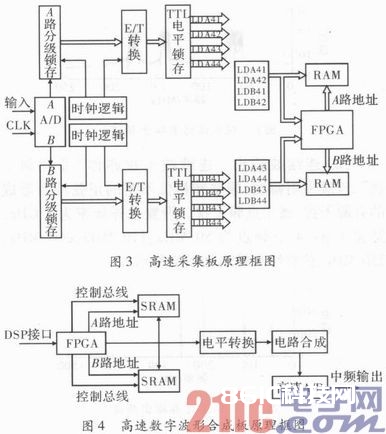

高速数据收集板首要完结模仿中频信号到数字信号的改换,它将中频信号进行量化处理,取得数字信号并存储。搅扰源的瞬时带宽要求为400 MHz,选用SPT公司的闪存A/D芯片SPT7760。SPT7760采样率为1 GHz,双路输出,每一路均有锁存时钟,每个端口的输出速度为500 MB·s-1。然后选用ADC输出分为8路的计划,将每一路的数据发生率降为125 MB·s-1,输出存储及处理。因为ADC的输出数据为ECL电平,而

后续的锁存器和缓存器为TTL电平,所以在降速之前选用M%&&&&&%RE公司的SY100系列,将ECL电平转化为TTL电平。

处理高速数据存储的办法一般是在高速数据输入和速度较低的大容量存储器之间参加高速FIFO。因为挑选的FPGA与存储器作业频率相同,同为200 MHz。FPGA只需发生同步操控信号在一个时钟周期内将TTL锁存数据存入存储器即可。一起FPGA还完结与DSP信号处理器的接口操控和数据转化等功用。

高速收集板的原理如图3所示。

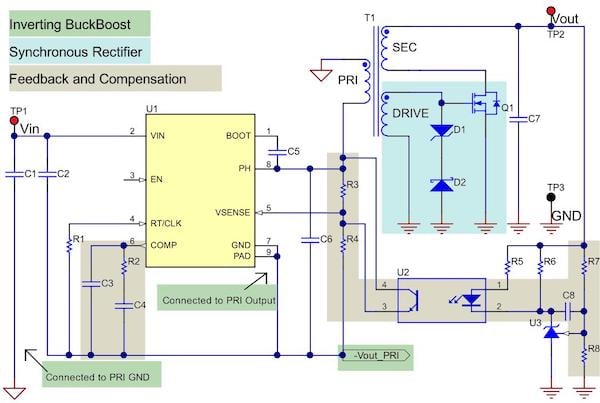

2.2 高速数字波形组成板

高速数字波形组成板本质是高速数字收集器的逆进程,它和高速数字收集器的差异在于它处理的信号是经过.DSP板剖析、核算后的搅扰信号,其原理框图如图4所示。规划选用Triquent公司的D/A芯片TQ6122。TQ6122是一款高速D/A转化器,转化速率为1GSa/s,具有8位数据位,功耗1.3 W。可广泛用于直接数字频率组成、高速恣意波形发生器、宽带视频信号生成等方面。

2.3 DSP处理板

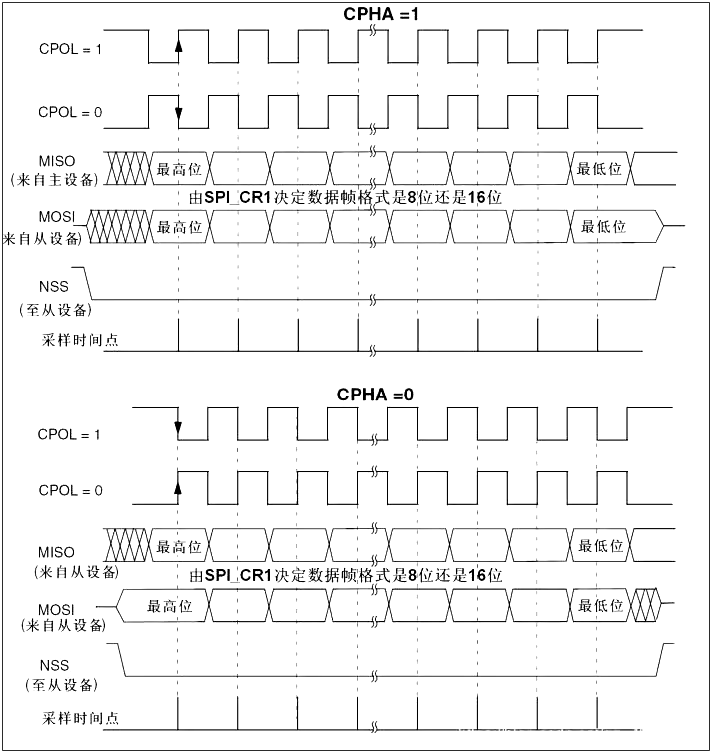

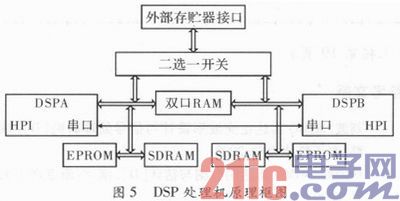

DSP信号处理机用于完结中频收集后信号处理、剖析以及搅扰款式的发生和部分体系操控的功用。中心处理器由两片TMS320C6701组成,两片处理器有独立的存贮器资源,也有彼此同享的存贮器资源,它们之间能够独立作业也能够彼此通讯和交流数据,通讯方法为串口通讯或经过双口RAM交流数据;DSP还供给数据总线、地址总线和读写信号等操控信号,并与外部高速数字波形组成器的数据接口或高速收集器的数据接口相接,以便交流数据和供给操控信号。DSP处理模块组成原理如图5所示。

3 规划仿真

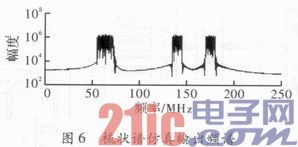

(1)梳状谱输出。梳状谱搅扰是针对多个信号或跳频信号进行的窄带噪声搅扰。在Matlab中选用3个独立的带限白噪声经滤波,带宽变为10 MHz、5 MHz、5 MHz后别离与65 MHz、140 MHz、175 MHz的本振混频后在输出,采样时刻设为1 ns,仿真成果输出如图6所示。

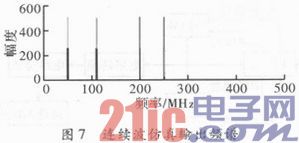

(2)接连波输出。接连波搅扰亦称“非调制搅扰”,接连发射起伏、频率和相位不变的正弦波所构成的有源搅扰,归于点频搅扰。设置采样频率为1 GHz,脉宽1μs,4个频点为50 MHz、110 MHz、200 MHz、250 MHz,仿真成果输出如图7所示。

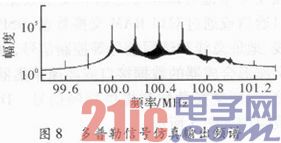

(3)多普勒信号输出。多普勒搅扰的原理是使用多普勒效应在接纳到的方针信号上添加或削减多普勒频移,构成拖速作用。依据多普勒频移添加或削减,在雷达屏幕上会呈现挨近或远离的移动虚伪方针。设置3个信号的多普勒频移为200 kHz、400 kHz、600 kHz,与本振100 MHz进行混频,仿真输出如图8所示。

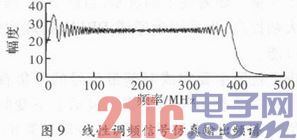

(4)线性调频信号输出。线形调频搅扰即扫频搅扰,在需求搅扰的频带里进行扫频,需求设置频率上下限,脉冲宽度。设置采样频率为1 GHz,脉宽1μs,带宽400 MHz,仿真输出成果如图9所示。

4 结束语

规划选用单通道起伏量化DRFM体系,选用高功用ADC器材并引进DSP模块,在简化了规划和降低了工程完结难度的一起完结了对宽带信号的处理。