体系往往需求信号传输,在信号传输中不期望共模信号,共模信号处理困难。某些规划把来自传感器输出的单端信号转化为全差分信号,然后,把此信号送到差分输出ADC下流。这样做的长处是在差分线上引起的最大噪声在两条线上是一起的(假定差分线是对称的)。

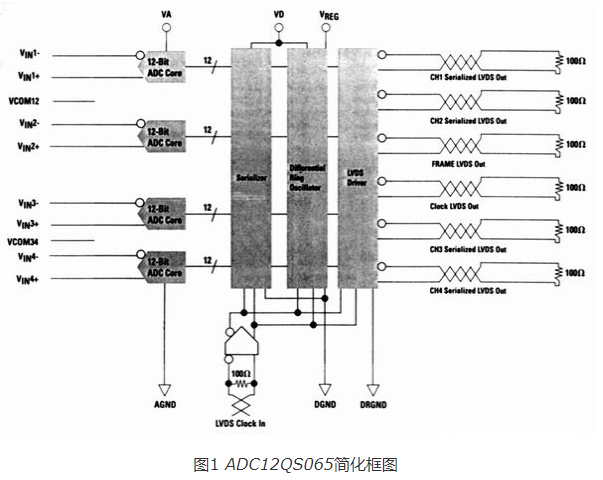

在输入信号转化数字数据之后,有必要传输它们到DSP或ASIC/FPGA进行处理。盛行的全差分输出信号传输是便利的。全差分的输出信号经过两条对称线给出和吸收电流。这种信号传输的一个比如是LVDS(低压差分信号)格局。ADC12QS065用LVDS来处理一切这些体系问题(图1)。

ADC12QS065在单片上包括4个12位ADC。每个ADC输入都接纳全差分信号。输入共模电压来源于共模输出参阅电压VCOM12和VCOM34,由ADC12QS065供给。ADC12QS065可选择全差分或单端时钟源。为了选用LVDS,时钟供给LVDS到CLKB,端接紧靠输入引脚。若期望单端CMOS时钟,则把CLKB接低态,而不需求端电阻器。

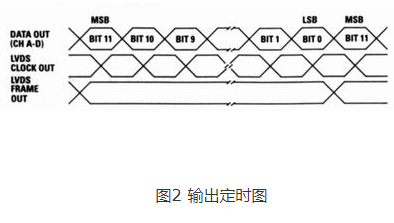

用差分环形振荡器串行化每个ADC的输出。输入时钟输入乘12,并转化到LVDS时钟输出,以使数据捕获。输入时钟率的LVDS FRAME信号也在输出发生来辨认取样数。

输出守时为FPGA供给简单的数据捕获。当取样数据准备好时,发送输出FRAME信号。在LVDS CLOCK OUT改变之后,呈现4个输出通道的每个通道的MSB。LVDS CLOCK OUT 信号从DATA OUT 偏移四分之一周期,以减轻时钟办理。在CLOCK OUT转化时捕获每个数据位。选用LVDS的另一个长处是能够用EIA/TIA568规范的双绞线发送这些信号。满意EIA/TIA568规范的双绞线具有100Ω 特性阻抗。紧靠在一起并承载相反电流的导体发生十分低的辐射。在高SNR要求的场合这是所期望的。

在传统单端并行CMOS输出12位ADC中,需求49条(4×12+1)线发送转化器,输出到数字处理器。若把输出位串行化,每个通道有单对差分线。也要阐明输出时钟和帧信号线。

由于LVDS用来自电源的电流,靠来自LVDS端或其他的“操作”(steering)电流,所以从电源稳定地吸收电流。这下降了呈现在电源线上的开关转化负载。此长处使电源线上的电源噪声比较低,然后减小去耦电容的尺度并减轻布线要求。

串行LVDS答应更小的封装,而信号传输是十分有用的。然而在许多使用中,低功耗是十分重要的。每个通道节约每毫瓦功率,关于需求几个数据通道的体系有巨大含义。因而,除静态驱动器外,ADC12QS0D65具有3个别离电源。能够衔接每个电源使其成为单电原ADC或维护别离。别离电源进一步阻隔ADC内部电路每部分。别离电源的另一个长处是输出驱动器电压能够低到2.5V,以节约功耗。

ADC12QS065也具有自己内部参阅供电的才能,答应外部驱动基准。这使多ADC可连组在一起,分别把一切的VRET和VREFN衔接在一起。靠确保每个芯片匹配的增益和偏移,可减小体系定标要求。若体系答应差分信号传输,用低共模噪声电感是有利的,能够下降电源瞬变,在输出线上有低数字辐射。ADC12QS065从模仿输入、时钟输入到串行LVDS输出,供给全差分转化。它所具有的别离电源才能答使用于进一步模仿数字域别离,并供给较低的功耗

责任编辑:gt