1.导言

时刻数字转化电路 TDC (Time to Digital Converter)广泛应用于高能物理中粒子寿数检测、自动检测设备、激光勘探、医疗图形扫描、相位丈量、频率丈量等研讨范畴[1]。如在医疗图象扫描仪 PET中广泛运用 TDC设备,其原理是检测人体内正电子对消失后发生的一对 gamma射线光子,运用模仿电路将所开释的 gamma射线光子与阈值比较,并在高于该阈值时发生一个触发脉冲,数字 TDC电路丈量该触发脉冲抵达的时刻。前期该类设备中的 TDC的分辩率为 2.5ns,现在新式设备中分辩率已达 1.4ns [2]。在激光勘探中,TDC电路用来丈量 TOF(Time of Flight for Laser),即分辩从激光源到方针后再返回到激光检测器的时刻[3]。别的,TDC也是直接完结 ADC的手法之一。假如在模仿信号前加一个 ATC(Analog to Time Conversion),加上后续的 TDC部分则能够完结 ADC进程。

前期 TDC电路一般由印刷线路板(PCB)上的分立元件组成,且一般是模仿-数字混合电路,因而功耗和体积较大、电路的一致性较差。超大规模集成电路(VLSI)工艺的前进使TDC规划在坚持高分辩率的前提下向高集成度、低本钱、低功耗方向开展。一起全数字集成(All DIGItal Integration)电路规划因工艺简略、规划本钱较低、规划难度较小、流片成功率高级要素而一直是电路规划人员寻求的方针,全数字的 TDC也是研讨人员重视的问题。

文献[4]于 1993年报导了一种依据环形延时门的全数字 TDC规划。该规划以 1.5微米 CMOS工艺完结了 13位数字转化输出,芯片面积为 1.1mm 2,分辩率为 0.5ns。之后于 2003年,该作者在文献[5]报导了一种全数字化的模数改换电路,该电路依据环形延时门的全数字TDC完结。文献称以 0.8微米 CMOS工艺在 0.45mm 2面积上完结了 18位全数字的 ADC。

跟着集成电路(IC)制作工艺的不断前进,以FPGA(Field Programmable Gate Array)和CPLD( Complex Programmable Logic Device)为代表可编程逻辑器材 PLD工业迅速开展,逐步蚕食专用集成电路ASIC(Application Specific Integrated Circuit)所占市场份额。这一开展使得依据PLD的TDC规划成为可能。众所周知,依据PLD的规划能够有效地缩短研发周期,

进步规划灵敏性和可靠性,下降规划本钱且无流片危险。成功规划的IP核(Intellectual Property Core )与工艺相对独立,可灵敏地移植到其他SOC,使规划重用变得非常便利。

本文学习文献[4]和文献[5]的环形延时门法提出一种依据 FPGA的高精度 TDC的规划办法,为了习惯 FPGA规划,对延时门法做了改造。假如简略移植延时门规划,在 FPGA中实践是行不通的。因为与 ASIC规划不同,在 FPGA里门电路是由 EDA软件归纳后完结,首要很难确保各门之间的延时一致性;其次,在时序上也很难确保和其他电路的合作。为了进步分辩率,与单纯计数型 TDC不同,本规划中也选用相似环形延时门规划的粗计数和细计数两部分电路对给定的时刻量进行丈量,粗计数部分操控丈量规模,细计数部分则由环形移位寄存器替代环形延时门完结。本转化电路以 QuartusII 4.2为软件渠道在 Altera系列芯品上完结,时序仿真标明昀高分辩率可达 3.3ns。

2.根本作业原理

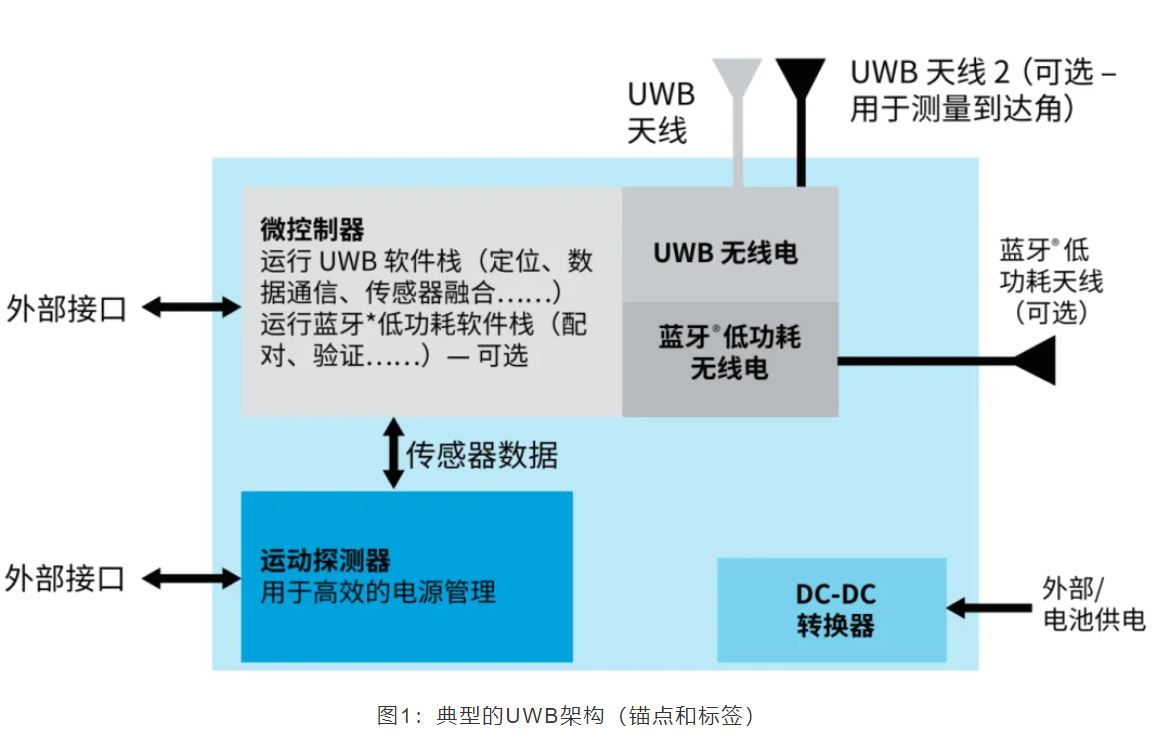

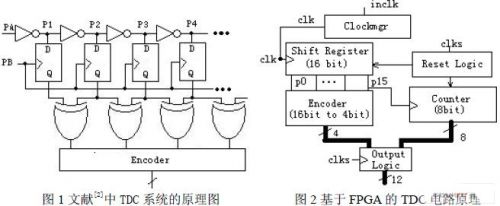

依据环形延时门的 TDC体系的原理框图如图 1 所示,PA是开始脉冲,由非门组成的特定结构延时链供给脉冲 PA的延时信息。在 PB上升沿,延时信息经锁存编码电路锁存并编码后输出,脉冲 PB与 PA之间的时刻差即由编码输出的数字量标明。试验成果标明,该办法适用于 ASIC完结,但不适用于 FPGA完结。原因是现在 EDA东西中归纳器的归纳成果是从规划目标的逻辑功用动身,而不重视规划者所特定的电路结构,而依据 FPGA电路的内部电路特色,文献[2]供给的延时链结构并不适于在 FGPA上完结。FPGA内部布线延时的不确定性会大大添加各单元延时信息的离散性。文献[6]介绍了该办法的 CPLD完结,但该法针对详细芯片附加了许多约束条件,延时链中每个非门由片内的一个逻辑宏单元 LE完结,因为 CPLD容量相对较小,导致芯片资源利率低,芯片间的移植性差,且因为 FPGA与 CPLD结构上的差异暂无法在 FPGA上完结。以下介绍一种全新的依据 FPGA的高精度 TDC规划办法。

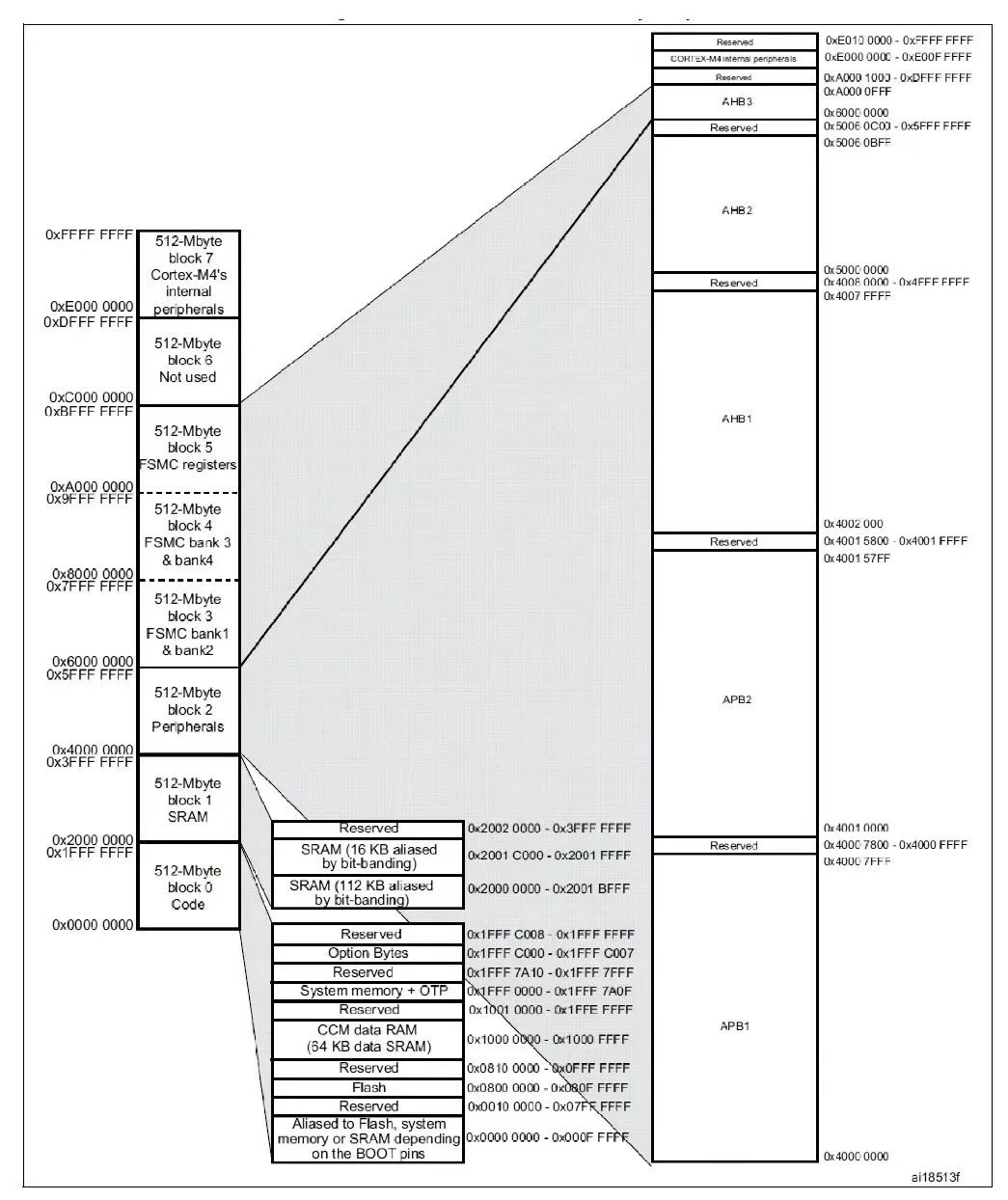

依据 FPGA的 TDC电路原理如图 2所示,该电路包含 16位环形移位寄存器 (Ring Shift Register)、16位输入 4位输出的编码电路 (Encoder)、时钟办理模块(Clockmgr)、8位通用计数器单元(Counter)、复位逻辑(Reset Logic)和输出逻辑部分(Out Logic)。其中环型移位寄存器和编码器组成该电路的细计数器部分,用来操控电路丈量精度;通用计数器作为粗计数部分,决议电路的时刻丈量规模;时钟办理模块经过调用 FPGA内部 PLL资源用来为移位寄存器供给适宜的作业时钟;复位逻辑操控整个 TDC电路的复位动作;输出逻辑将转化数字量的细计数和粗计数部分组合为昀终体系输出。

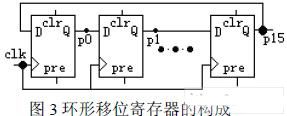

16位移位寄存器构成如图 3,由 16个带异步复位和置位端的 D触发器组成,初始状况或复位后电路节点 p15被置位高电平,其他节点(p14至 p0)被复位至低电平;正常作业时,在移位脉冲 clk上升沿时高电平在 16个电路节点中循环呈现,经过查看某时刻电路节点的状况(高电平的方位)能够判别体系所阅历的移位脉冲 clk的数量,电路的时刻分辩率即为 clk的时钟周期。编码器对移位寄存器节点状况编码并作为丈量电路细计数部分的 4位输出。通用计数器作业在移位寄存器节点 p15的上升沿,其计数周期为移位脉冲周期的 16倍,完结低位到高位的进位计数,并作为丈量电路的粗计数部分的 8位输出。复位逻辑担任环形移位寄存器和通用计数器的复位操作。输出逻辑分别将粗计数和细计数输出的 8位和 4位数据组合为丈量电路的昀终输出,并完结数据的校验。

依据 FPGA的单计数器脉宽丈量电路选用在脉冲宽度对应的时刻内记数的办法,因高频作业时计数器会呈现跳码或漏计现象,形成体系过错输出,所以分辩率很难进步 [7]。与单计数器脉宽丈量电路比较选用结构简略的细计数电路能大大进步电路的时刻分辩率,并避免了通用计数器极限作业频率下的跳码现象,且细计数电路占用很少的片上资源。

3体系完结及优化

Altera公司供给的 Stratix和 Cyclone系列 FPGA芯片具有嵌入式锁相环( PLL)模块,该模块可对外部时钟进行倍频分频及相移操作,可编程占空比和外部时钟输出,进行体系级的时钟办理和偏移操控,常用于同步内部器材时钟和外部时钟,使内部作业的时钟频率比外部时钟更高,时钟推迟和时钟偏移昀小,减小或调整时钟到输出(TCO)和树立(TSU)时刻,然后供给完好的时钟办理计划。运用 Altera Quartus? II软件无需任何外部器材,就能够调用芯片内部的 PLL来完结相应功用。

该体系时钟办理模块调用 FPGA内部 PLL完结,经过 QuartusII设置参数为:Ratio为倍频/分频因子(Ratio)为 4,输出时钟相移 (Ph) 为 0,输出时钟占空比 (DC)为 50%。

该 TDC电路的时刻分辩率取决于环形移位寄存器和编码电路组成的细计数部分,要得到正确的丈量数据有必要确保对移位寄存器输出状况的正确编码。与 AS%&&&&&%规划不同,规划者很难意料 EDA软件布局布线(Layout)后的状况,并且各种不同结构和功用的可编程器材布局布线的成果也不尽相同,并且构成移位寄存器的 D触发器的时钟到输出时刻(TCO)和 D触发器输入在金属连线上安稳树立的时刻(TSU)也存在必定离散性,使得高频移位脉冲(纳秒级)作业下的移位寄存器在状况转化时呈现毛刺现象,影响编码正确输出,一起编码器的固有延时特性也约束体系的时刻分辩率。该脉宽丈量电路体系选用的优化的编码算法,使得高频移位状况下编码输出能精确反映环形移位寄存器上各节点状况,然后确保了该体系的丈量精度;移位时钟为 333MHz(周期 3ns)时在 Altera公司 Stratix和 Cyclone系列芯片上完结了编码器的正常作业。

该体系包含了粗记数和细记数两部分电路,粗记数电路在细记数字电路高位输出(图 3中 p15)的上升沿作业。可是因为粗记数电路的延时在被测脉冲( clks)上升沿时可能会形成对输出数据的误读。

为处理误读现象,在输出逻辑模块里参加纠错电路。对被测脉冲 clks延时 clk周期后发生新时钟 clks1,在 clks和 clks1的上升沿一起对 q1和 q0取样并对取样数据进行处理后作为昀终数据输出,然后有效地处理了误读现象。

移位脉冲作业频率即为该丈量电路的时刻分辩率,经过时钟办理单元可选用不高的外部时钟便可得到很高的丈量精度。

3仿真成果和测验数据

为测验该体系的时刻分辩率,为根本时刻数字转化电路附加特定功用电路,使其具有接连丈量时钟脉冲宽度的功用,测验目标是 clks的高电平连续时刻。经过改动时钟脉冲源的频率来记载该电路对应的丈量数据,然后得到该 TDC电路的时刻分辩率。

本文以 QuartusII Web Edition 4.2为软件渠道,试验标明,本 TDC规划在 Altera各干流芯品上的时序仿真均能顺畅经过。适配 Cyclone EP1C3Q240C8芯片的时序仿真标明,移位时钟为 333M(即分辩率为 3ns),所得到的测验数据输出正确地反映了被测脉冲的宽度,被测脉冲下降沿到丈量数据树立的延时为 5ns。

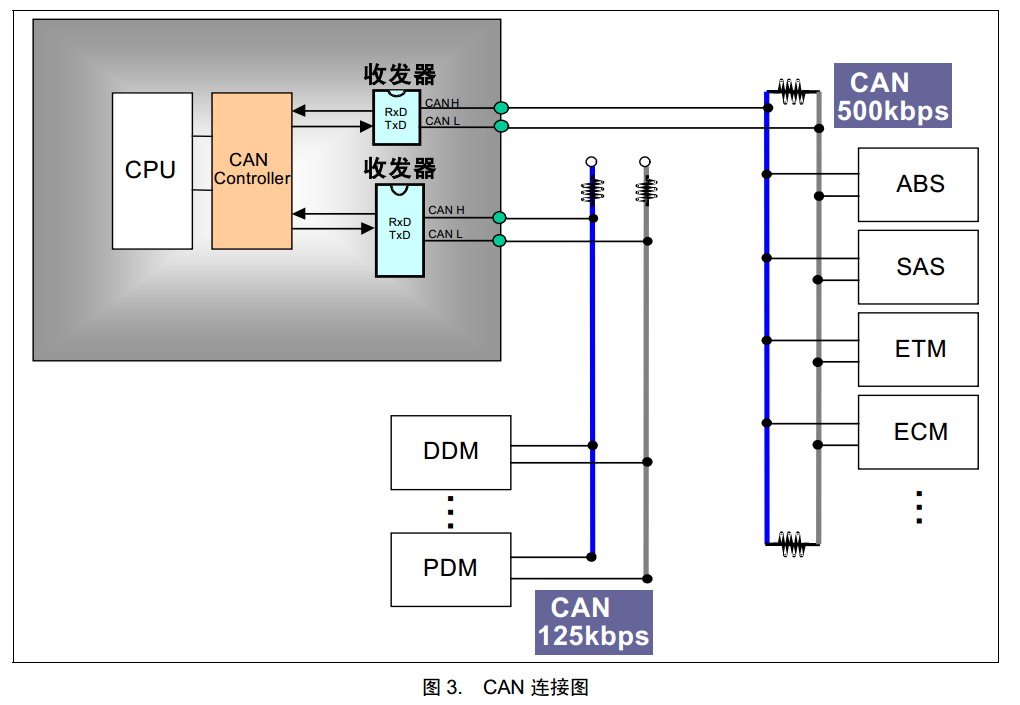

由该 TDC构成的脉宽丈量电路在 Cyclone EP1C3Q240C8芯片完结,体系外部时钟 25Mhz,PLL设置倍频因子 8,由 SP1641B信号发生器供给固定的被测脉冲频率 F,时刻分辩率 Res的散布如图 4所示,测验数据标明 Res在 4.9-5.1ns之间,理论值为 5ns。

丈量和仿真数据标明该电路能到达纳秒级时刻分辩率,逻辑资源占用少,可在低密度芯片上完结作为专用丈量电路运用,或在高密度芯片上作为功用模块嵌入到特定功用的片上体系(SOC)中;该 TDC电路的转化速度也在纳秒级,使该电路适用于实时数据收集及高速数据处理体系。精度可调也是该规划一大特色,移位脉冲的作业频率决议了该转化体系的转化精度,经过时钟办理单元能够发生不同频率的移位时钟,然后丈量精度能够依据详细需求进行恰当调整。

3结束语

本依据 FPGA的时刻数字转化电路规划在占用较少芯片资源的前提下,完结了很高的丈量精度,作业时数据转化速度也在纳秒级;本规划电路接口简略可作为独立的功用电路运用,亦可作为功用模块 IP核[8]便利地嵌入到其他体系完结特定功用。依据 Altera芯片的时序仿真和硬件测验标明晰该办法的可行性和精确性。