1 、导言

HDB3(High Density Bipolar三阶高密度双极性)码是在AMI码的基础上改善的一种双极性归零码,它除具有AMI码功率谱中无直流重量,可进行过失自检等长处外,还克服了AMI码当信息中呈现连“0”码时守时提取困难的缺点,并且HDB3码频谱能量首要会集在基波频率以下,占用频带较窄,是ITU-TG.703引荐的PCM基群、二次群和三次群的数字传输接口码型,因而HDB3码的编解码就显得极为重要了。现在,HDB3码首要由专用集成电路及相应匹配的外围中小规划集成芯片来完结,但集成程度不高,特别是位同步提取非常复杂,不易完结。跟着可编程器件的开展,这一难题得到了很好地处理。

本文运用现代EDA规划办法学和VHDL语言及模块化的规划办法,规划了适合于FPGA完结的HDB3编译码器的硬件完结计划。不光克服了分立硬件电路带来的抗干扰差和不易调整等缺点,并且具有软件开发周期短,成本低,履行速度高,实时性强,晋级便利等特色。

2、 HDB3编解码原理

要了解HDB3码的编码规矩,首要要知道AMI码的构成规矩,AMI码便是把单极性脉冲序列中相邻的“1”码(即正脉冲)变为极性替换的正、负脉冲。将“0”码坚持不变,把“1”码变为+1、-1替换的脉冲。如:

NRZ码:1 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1

AMI码:-1 0 0 0 0 +1 0 0 0 0 -1 +1 0 0 0 0 -1 +1

HDB3码是一种AMI码的改善型,它的编码原理可简述为,在音讯的二进制代码序列中:

(1)当连“0”码的个数不大于3时,HDB3编码规矩与AMI码相同,即“1”码变为“+1”、“-1”替换脉冲;

(2)当代码序列中呈现4个连“0”码或超越4个连“0”码时,把连“0”段按4个“0”分节,即“0000”,并使第4个“0”码变为“1”码,用V脉冲标明。这样能够消除长连“0”现象。为了便于辨认V脉冲,使V脉冲极性与前一个“1”脉冲极性相同。这样就损坏了AMI码极性替换的规矩,所以V脉冲为损坏脉冲,把V脉冲和前3个连“0”称为损坏节“000V”;

(3)为了使脉冲序列仍不含直流重量,则有必要使相邻的损坏点V脉冲极性替换;

(4)为了确保前面两条件建立,有必要使相邻的损坏点之间有奇数个“1”码。假如原序列中损坏点之间的“1”码为偶数,则有必要补为奇数,行将损坏节中的第一个“0”码变为“1”,用B脉冲标明。这时损坏节变为“B00V”方式。B脉冲极性与前一“1”脉冲极性相反,而B脉冲极性和V脉冲极性相同。

如:

NRZ码:1 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1

AMI码:-1 0 0 0 0 +1 0 0 0 0 -1 +1 0 0 0 0 -1 +1

HDB3码:-1 0 0 0 -V +1 0 0 0 +V -1 +1 –B 0 0 -V +1 -1

尽管HDB3码的编码规矩比较复杂,但译码却比较简单。从上述原理看出:每一个损坏符号V总是与前一非0符号同极性(包含B在内)。这便是说,从收到的符号序列中能够容易地找到损坏点V,所以也判定V符号及其前面的3个符号必是连0符号,然后康复4个连0码,再将一切-1变成+1后便得到原音讯代码。

3、 编解码器规划

3.1 编码器规划

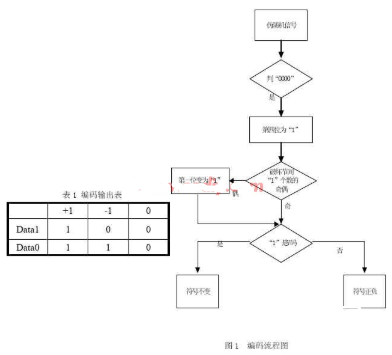

因为VHDL不能处理负电平,只能面向“1”、“0”两种状况,所以要对它的输出进行编码,如表1所示。编码的完结是依据HDB3编码原理把二进制码编码成两路单极性的码字输出,之后经过单双改换模块构成HDB3码。在编码过程中,要经过连0检测、损坏节判别、损坏节间“1”的个数判别、调整“1”的符号输出等过程,编码部分可分为4个模块,编码流程如图1所示。

在进行HDB3编码器的设计时,需注意以下两个问题:

(1) 考虑将某些“0”改为“1”

用一个四位移位寄存器来对输入的序列进行检测,当检测到4个连“0”时,将其第四个“0”改为“1”。再设置一个T触发器来检测两个相邻的损坏节之间“1”的个数,若T触发器为“0”则阐明两个相邻的损坏节之间“1”的个数为偶数,需要将第2个损坏节的第一个“0”置“1”,若T触发器为“1”,则阐明两个相邻的损坏节之间“1”的个数为奇数,第2个损坏节的第一个“0”不变。

(2) 正、负号的考虑

除了损坏节的V即“1”的符号与它前面最近的“1”的符号相同外,其他的“1”的符号都是正、负替换的。所以再设置一个T触发器,当它检测到“1”时就使DATA1翻转。当然,这样就不可避免地使损坏节的V的符号也呈现翻转,为了避免它的翻转,用一个三位移位寄存器来盯梢V码,以确保V码的符号不变(与它前面最近的“1”的符号相同)。

本文在程序的实体中界说了2个输入端口:时钟、伪随机序列,一个两位的输出数据(编码后的输出)。程序的结构体中运用的是进程句子,共选用4个进程,别离完结判别4连“0”方位并刺进V、记相邻V码间1个数、盯梢V码方位及编码输出的功用。灵敏信号均选用的是时钟信号,关于其任一改变都将一起发动4个进程,并行履行。在程序中共运用了5个信号,代表了电路的寄存器作用,装备到电路中也相当于寄存器。

3.2 解码器规划

解码规划是依据HDB3码的特色首要检测出极性损坏点,即找出4连零码中增加V码的方位(损坏点方位),其次去掉增加的V码,最终去掉4连零码中增加的B码以将其复原成单极性不归零码。

由HDB3码的编码规矩可知,“0000”都被“000+1”或“000-1”或“+100+1”或“-100-1”替代,所以,只要能检测出“+1000+1”、“-1000-1”、 “+100+1”、“-100-1”、将它们别离改为“10000” 、“10000”、“0000”、“0000”就能够了。

当然“+1”、“-1”、“0”仍是由Data1,Data0来标明,那么就需要有两个5位移位寄存器(C和D),Data0经过D,Data1经过C。经过D,C来检测,假如测到两个移位寄存器别离为“10001”、“0xxx0”或“10001”、“1xxx1”或“1001x”、“1xx1x”或“1001x”、“0xx0x”,数据输出是将D里边的数据流输出。所以只要将D中所测到的以上数据别离改为“10000”、“10000”、“0000x”、“0000x”,这样就能够得到HDB3码的解码了。

4、 仿真和试验成果剖析

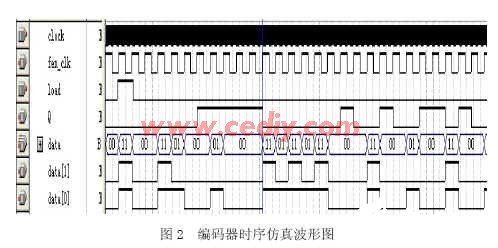

编译码器在QuartusII上仿真的波形别离如图2和图3所示。图2中fen_clk为分频后时钟信号,load 为使能信号,Q为伪随机序列,data为编码输出。因为输入的数据流经过了5个寄存器,所以输出延迟了4个时钟脉冲周期。但因为时钟频率很高,所以影响不大。

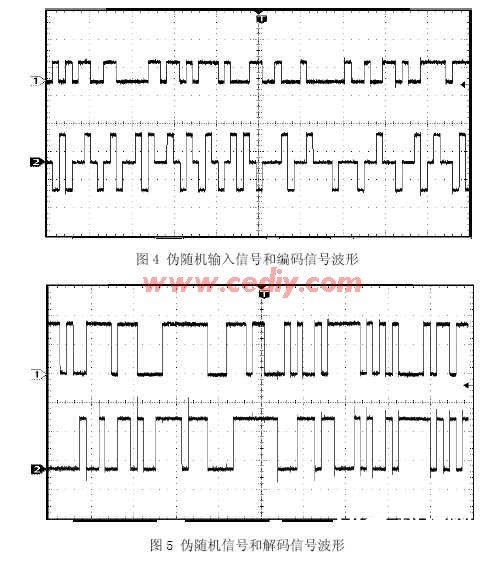

把上述规划下载到Altera EP1C3T144C8芯片上,并经过硬件调试、测验,在示波器上得到伪随机信号波形、编码波形和解码波形别离如图4和5所示。其间,CH1为伪随机信号,CH2别离为编码和解码信号。测验成果和时序仿真成果无失真。随机信号输入相对编码信号输出延迟了5个单位时钟。解码信号延时了11个单位时钟。

5、 定论

实践标明,运用FPGA来完结NRZ码到HDB3码的转化与选用专用集成电路CD22103比较,不只给调试带来了便利,并且能够把编码电路和解码电路及其它电路集成在同一块FPGA芯片中,减少了外接元件,提高了集成度。该规划已成功应用于网络化会集照明控制体系中。然而在实践无中继长线传输中,会呈现信宿端信号严峻失真的现象,一种对长线传输体系中HDB3编码的失真信号进行纠正的算法见文献。

本文作者的立异点:本计划规划模块能够作为IP(Intellectual Property)核,与嵌入式处理器及其他功用模块或IP芯核相结合在一片FPGA上构成片上可编程体系SOPC,使得所规划的体系在其规划、可靠性、体积、功耗、功能等方面完结最优化。

作者简介:

吴海涛(1975-),男(汉族),山东青州市人,广东肇庆学院电子信息工程系讲师,硕士,首要从事通讯、EDA技能应用研究。

陈帅气(1962-),男(汉族),广东潮州人,广东肇庆学院电子信息工程系副教授,首要从事计算机通讯及视频处理技能研究。

梁迎春(1975-),女(汉族),广西玉林市人,广东肇庆学院电子信息工程系讲师,硕士,首要从事EDA/SOPC技能研究。

责任编辑:gt