0 导言

在现代通讯体系中,信道编码技能得到了广泛的运用。卷积码结构简略,硬件完成简略,一起有着较好的查错纠错才能,因此在无线通讯中常常运用,而其解码办法常用Viterbi译码。

1 卷积编码

卷积码(Convolutional Coding)是由PgElias 于20 世纪50年代提出的一种非分组码。它完成十分简略,即将发送的信息序列通过一个特定的线性移位寄存器,即完成了编码。

卷积编码常用(n,k,m) 表明,一般n 和k 的值都比较小,其间m 为编码束缚长度,它表明编码时相应的信息比特在编码器中逗留的时刻。卷积编码是一种前后相相关的编码进程,编码后的码元和当时的k 个比特位相关,一起也与前m – 1 个输入比特相关,使得彼此相关的码元抵达m × n 个。衡量卷积码功能的两个重要参数是码率 (k n)和束缚长度。

2 卷积码的描绘办法

卷积码的编码描绘办法有许多,工程中最常用的是寄存器网络结构法、码多项式法和状况图形表明法。

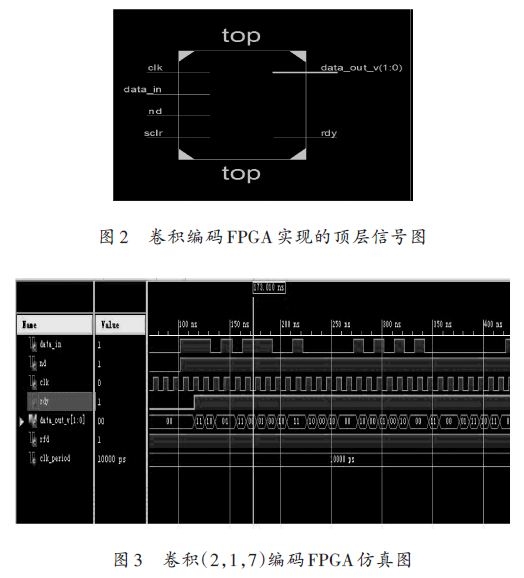

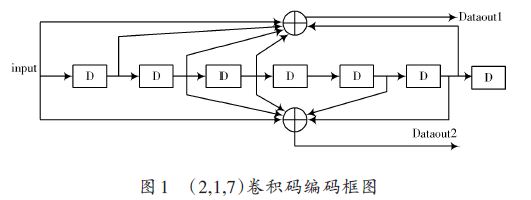

如本体系中运用的(2,1,7)卷积编码,它的寄存器网络结构法表明如图1所示。

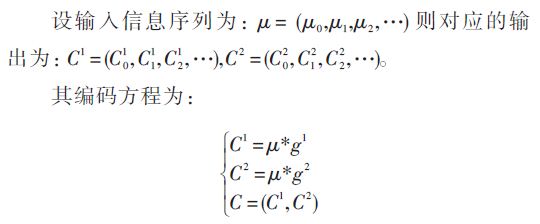

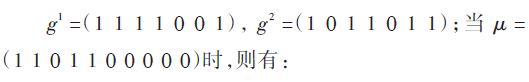

离散卷积法表明如下:

其间卷积运算用*表明, g1,g2 为脉冲冲激响应。则如图1中能够表明为:

3 卷积码的译码

因为卷积码自身没有严厉的代数结构,其译码进程相对杂乱。现在常用的办法有两类:

(1)代数解码。这种解码办法是运用编码自身的代数结构进行解码,但不考虑信道的核算特性;(2)概率解码。这一解码办法则充分运用了信道的核算特性。现在常用的有Viterbi译码、最大后验概率译码(MAP)以及它的改善算法Max_log_MAP等。本文选用的是Viterbi译码简称(VB)。

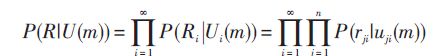

关于(n,k,m) 的二进制卷积码,编码输入的信息序列是独立等概率的,比较各种条件下的概率,即似然函数P(R|U(m)),挑选其间概率最大的,所得便是译码值,它具有最小过失概率。其间R 是实践接纳到的序列,U(m) 是或许的发送序列。当满意P(R|U(m′)) =max P(R|U(m)) 条件时,U(m′) 便是译码值。

假定加性高斯白噪声作为体系噪声,一起信道是无记忆性,则卷积码的似然函数为:

式中:Ri 是接纳序列R 的第i 个分支;Ui (m) 是特定码字U(m) 的第i 个分支;rji 是Ri 的第j 个码元;uji (m) 是Ui (m) 的第j 个码元,每个分支由n 个码元组成。在工程实践中通常用对最大似然函数取对数,以加法替代乘法。对数的最大似然函数界说为:

当log P(R|U(m)) 的值最大时,译码成功。Viterbi译码运用了编码网络图的特别结构,降低了核算的杂乱度,但它本质上仍然是最大似然译码。算法实践执行时,边接纳边比较,一起去除不或许成为最大似然挑选对象的途径,也便是说假如两条途径抵达同一状况,被选中的是具有最佳测量的途径。这一途径称为幸存途径,对一切状况进行比较、挑选,扔掉不或许的途径,然后降低了译码器的杂乱性。译码从根本上说,也便是挑选具有最小间隔的码字或最大似然测量的码字。

4 卷积码编码的工程完成

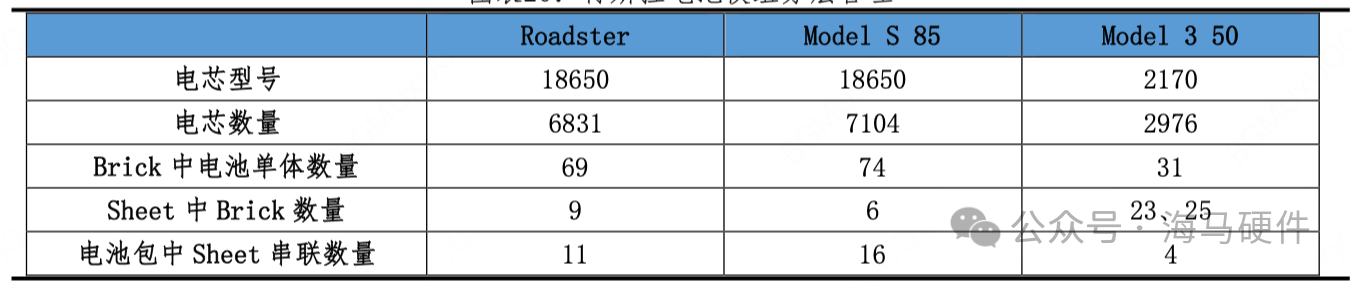

卷积码的编码在工程中比较简略,由移位寄存器和异或组成,体系中运用(2,1,7)编码,完成原理如图2所示。在FPGA中的仿真如图3所示。