跟着组成孔径雷达(SAR)对分辨率的要求不断进步,其间频采样后回波信号的数据量与信号处理后的二维雷达图画的数据量大大添加。为了便于后续剖析与处理,一般会将这些海量回波数据以及雷达图画数据进行无失真数据存储。这对数据存储体系的规划提出了两个方面的要求:(1)接口简略且有较高的数据存储速率;(2)因为所需存储数据数量巨大,要求存储体系有满意的容量。

传统的SDRAM存储计划跟着存储器容量的添加,其复杂性和完成本钱也敏捷进步,且在体系掉电后所存储数据会丢掉,不合适数据的回放剖析及处理的运用场合[1]。而选用依据Flash的存储计划,存储容量大(单片容量可以到达32 GB),不光数据存储的功率较高(单片读写速度可以到达160 Mb/s),并且其接口通用、规划简略,便利频频读写操作,因此是大容量雷达数据实时存储的优选计划。

1 体系规划

1.1体系规划方针

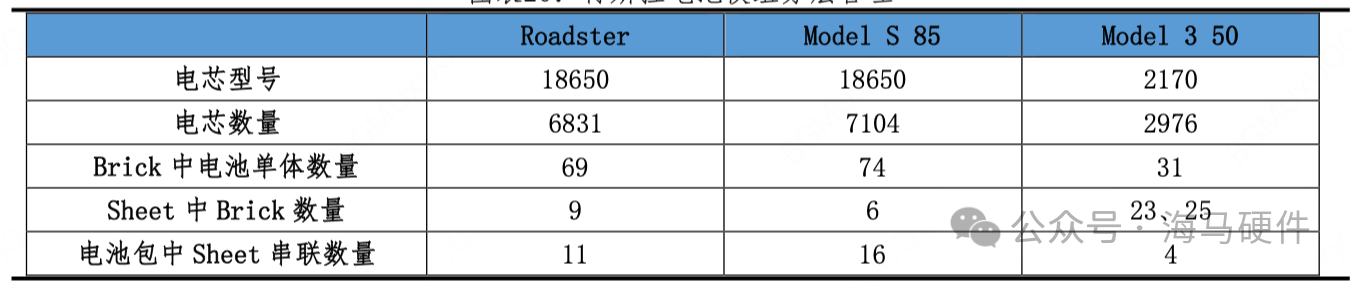

本体系是SAR雷达信号处理体系中的子体系,首要完成对中频采样数据和组成孔径雷达匹配现象数据进行存储与回放。依据运用需求剖析,规划的体系应具有数据存储和数据回传(上传至PC机)两项根本功用,其间以数据存储为中心功用。在数据存储进程中,最要害的两个方针别离是数据存储速率和数据存储量。这两项方针直接影响体系规划的好坏。依据表1列出的SAR作业典型参数,就上述两个方针进行剖析。

(1) 存储速率剖析

由表1可知,通过信号处理后的一帧图画为4 096×4 096像素。极限情况下,每秒钟信号处理模块会送出3.5帧匹配现象数据,则图画存储的速率有必要大于448 Mb/s。存储中频采样数据时,依据上述采样率以及A/D的采样位宽,可预算每秒收集到的正交两路中频雷达信号数据量为350 MB,即中频采样数据的存储速率要求高于2.8 Gb/s。

(2) 存储量剖析

因为体系选用非易失存储介质,存储量与体系开机运转时刻相关。依据剖析,设定存储体系作业在最长时刻5 min时,可预算规则时刻内体系需求存储102.6 GB的中频采样数据和16.5 GB的图画数据。这就要求规划体系板载总数据存储容量大于118.1 GB。

1.2 体系结构

为了满意规划技术方针要求,对构成体系的首要器材挑选如下: (1)存储体系主控器选取Altera 公司型号为EP2S90F780 的FPGA芯片。(2)存储芯片选取三星公司型号为K9LBG08U0M的NAND Flash。(3)选取Cypress Semiconductor公司的EZ-USB FX2作为数据回传USB2.0的微处理操控器。(4)选用美光公司型号为ML48LC8M16的SDRAM作为数据缓存芯片。体系硬件结构框图如图1所示。

2 硬件规划

2.1 SDRAM接口规划

SDRAM与FPGA的衔接示意图如图2所示。左面是SDRAM芯片ML48LC8M16的引脚,右边是FPGA中SDRAM数据接口模块对应的信号。体系中运用了两片ML48LC8M16,图2是一片SDARM的接口,另一片接口与之相同。两片SDRAM乒乓缓存高速数据,可以添加体系存储的安稳性和可靠性。

2.2 NAND Flash存储模块规划

体系数据存储根本单元由型号为K9LBG08U0M的NAND Flash芯片组成,K9LBG08U0M是一款低功耗、高功率的NAND Flash存储芯片。其内部选用典型“块-页”安排结构办法,片内一共分为8 192块,每块包括128页,每页可存储4 KB,总存储空间到达4 GB[2]。其典型编程和擦除时刻别离为0.8 ms、1.5 ms,存储速度较快,存储容量适中,合适SAR海量数据存储的运用场合。体系以FPGA为主操控器,并行操控4个NAND Flash存储器作业组,其接口电路原理图如图3所示。每个存储器组别离由8片K9LBG08U0M芯片组成。每组中又以4片为一个最小存储单位。每个最小存储单位中,将地址锁存信号ALE、指令锁存信号CLE等操控信号线通过并接的办法衔接到一同,各片数据地址复用线IO0~IO7独立衔接至FPGA的通用I/O中。

这样将数据通道可扩展至32 bit,有用地拓宽了数据存储带宽,进步了数据吞吐量。一起,因选用了32片NAND Flash芯片,板载存储容量到达了128 GB。

2.3 回传模块规划

数据回传通道通过EZ USB 68013与PC衔接,集成了USB2.0收发器、串行接口引擎(SIE)、增强型8051微操控器和可编程的外围接口。规划中选用USB 68013的GPIF接口,并运用8 bit的传输办法。EZ-USB FX2可装备成Ports、GPIF Master(主)和Slave FIFO(从)三种不同的接口形式,在规划中运用Slave FIFO形式[3]。在该形式下,外部逻辑直接衔接到FX2的端点FIFO,GPIF并没有被激活。因为外部逻辑可以直接操控FIFO,所以FIFO的根本操控信号(标志、片选、使能)由EZ-USB FX2的引脚引出,外部操控可以是同步或异步。图4为在Slave形式下USB芯片外围电路以及与FPGA衔接的原理图。

3 存储体系软件规划

3.1操控器软件模块

数据传输与存储操控电路的开发作业首要会集在FPGA上。依据上述剖析与介绍,结合NAND Flash以及USB 68013芯片的操作特色,考虑操控器的通用性与体系的可扩展性,存储体系软件规划如图5所示。其间包括USB操作指令解析模块、写时序产生模块、坏块办理模块、数据上传操控模块、块擦除时序产生器模块、读时序产生器模块等。

图5中,虚线框标定的软件模块均运用硬件描绘言语编写,在Quarters II编译环境下编译、归纳并得到了完成。

3.2 体系作业流程

体系作业流程如下:上电后,由坏块办理程序扫描一切存储块,一起记载坏块地址值,并存入FPGA内树立的RAM坏块表中;然后体系等候接纳并解析USB操控指令;若操控指令为数据存储,首要进行写数据方针块擦除操作,然后在坏块办理程序监管下,由写时序产生模块存储SDRAM接口准备好的数据,数据存储完毕后体系进入待命状况。若操控指令为数据读取,首要从USB操控指令中解分出方针数据地址,之后由读取时序产生模块将数据读入USB芯片的FIFO中;终究体系依据FIFO标志位将数据上传至PC机。整个存储体系作业的流程图如图6所示。

3.3存储速度优化

从存储芯片的存储机制动身,优化操控器软件结构可以到达进步体系存储速度的意图[4]。单片NAND Flash将数据写入的进程是:通过数据总线向存储芯片发送写数据指令80 h,紧接着写意图页地址,然后写4 096 B数据(核算数据写入所需求时刻为Tdata-in),终究输入完毕指令10 h[2]。这一系列操作完成后Flash进入繁忙状况,一起将4 KB数据从数据缓存区搬移到内核,核算搬移所需求的时刻为Tprog。则4 KB数据写入的总时刻如下:

由此可得到单片写入速度为96 Mb/s。体系硬件结构规划时将4片存储器作为最小单元级联,选用该办法数据写入速度可以进步到384 Mb/s。为进一步进步速度,可将数据搬移时刻Tprog充分利用起来。操控器软件能完成对两个不同的单元进行乒乓操作,即在一个存储单元进入忙状况时,另一个存储单元开端写。这样替换操作,写入速度可到达768 Mb/s。操控器一起驱动4个存储器组并行作业,则其数据存储速度可进一步提升到3 072 Mb/s(即3 Gb/s)。

3.4 NAND Flash坏块办理

因为NAND Flash 在出厂和运用进程中都会呈现坏块 (无法或过错地存储数据),这将对所存储数据的精确性构成影响。为了精确无失真地存储数据,有必要对NAND Flash中随机呈现的坏块进行有用的处理。本规划选用一种自习惯(可变长度)状况机办法,简略有用地完成了坏块的办理。体系上电运转时,将由主操控器扫描得到的一切坏块地址值存入FPGA内树立的RAM表中[5]。

采纳这样的办法,可使片上RAM资源耗费下降[6]。在进行数据写操作时(地址线性添加),判别坏块地址与当时写地址之间的间隔,通过内部计数器操作可避开坏块。坏块办理状况转换图如图7所示。

坏块办理状况机包括3个状况:Idle(空状况)、Get_timer(取坏块间隔状况)、Addr_change(块地址改动状况)。其操作流程如下:(1)体系复位时状况机进入Idle状况,等候不履行任何操作。(2)当页地址标志位不为0时(写操作开端),状况机进入Get_timer状况,此状况下取下一个坏块到当时块的间隔,并赋给定时器timer,若timer为“0”持续停留在该状况,一起接连坏块地址自加;若timer不为“0”,则状况跳转到Addr_change。(3)在Addr_change状况下,等候一个Block中一切页写完后,判别timer是否为非“0”,若是块地址自加,一起timer自减;反之输出块地址为原地址加上接连坏块寄存器的值。

该办法完成的坏块办理程序,能有用避开随机呈现的坏块,下降片上资源耗费,进步了作业功率,保证了雷达数据存储的完好性与精确性。

4 体系试验成果

通过软硬件协同规划,终究完成了整个存储操控体系,包括板载32片Flash芯片(正面16片,反面16片)、主控FPGA芯片、USB操控芯片、SDRAM芯片、装备芯片等。

将同一帧灰度图画数据别离存储在通过坏块办理的存储器组1和未通过坏块办理的存储器组2中,然后通过读时序操作别离读取数据,在PC机上整组成一帧完好的图画并做比照,其成果如图8所示。可见未经坏块办理存储的图画数据呈现失真,坏块区域输出成片“0”值,图画呈现带状白色噪声点,这些搅扰噪声会严重影响后续信号处理成果。

通过坏块办理后读出的数据构成如图8(b)的图画可以发现,彻底不存在图8(a)所示现象,图画中只要包括有实在方针的匹配成像信息。阐明通过坏块处理后数据被完好精确地存储起来,不会对后续的信号处理构成影响。

本文介绍的体系作为子模块已在SAR成像体系中成功运用。实践证明,本存储回放体系可以高效、安稳、可靠地作业,并且数据存储无失真。在后续作业中,可在Flash操控逻辑上选用双线程操作(Two Plane)办法,能将数据写入速度进步约1.6倍;也可验证操控器的通用性,在存储板上搭载单片容量更大的存储芯片,简略修正装备参数就可将现在板载总容量为128 GB的存储体系将其容量扩至4 TB,使其习惯未来大容量存储设备的发展趋势。