跟着信息处理技能的开展,实时图画处理已成为现代信息处理范畴中的一项要害技能,该技能的开展关于电视制导、图画盯梢等具有重要的意义。实时图画处理要求非常大的核算量与超高的核算速度,单片DSP很难满意要求,因而有必要选用多DSP并行核算结构。这就要求实时图画处理体系可以实时获取图画数据,并在多片DSP之间完结实时通讯交互。论文实时图画处理体系为中心,论说了依据Analog Device公司的DSP(TS201)为中心器材的链路口通讯规划。

1 实时图画处理体系的组成

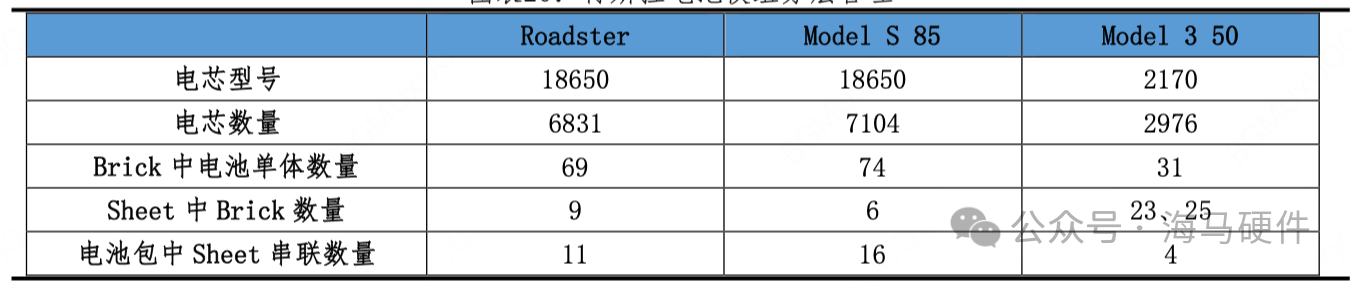

如图1所示,实时图画处理体系主要由4个模块组成:CCD图画收集模块、图画处理模块(TS201 3个DSP+FPGA模块)、图画处理成果输出模块、逻辑操控模块。

其根本的作业原理是将CCD摄像头收集得到的实时图画经AD转换成数字图画,经过FPGA(现场可编程逻辑门阵列)别离送到3个DSP中,DSP经过图画处理模块完结对图画信号的运算处理,最终经过输出模块输出所希望的运算成果如被捕捉方针的方位信号、调理操控信号等。

实时图画处理体系FPGA(Field Pmgrammable Gate Array)选用Altera公司的EP4SGX230/180,该器材具有高密度、高功能、低功耗等长处。FPGA是在专用ASIC的基础上开展而来的,它克服了专用AS%&&&&&%不行灵敏的缺陷。其内部的详细逻辑功用可以依据需求装备,对电路的修正和保护很便利。

DSP选用ADI公司的TigerSHARC 201,TS201是现在业界功能最高的DSP处理器之一,具有以下特色:主频可高达500 MHz;具有24 Mbit片上内存、双运算模块、外部端口、4个高速链路口、SDRAM操控器、可编程标志引脚、2个守时器和守时输出引脚、14通道的DMA操控器。可以完结片内存储器、片外存储器、储存器外设、链路口、主机处理器和其他处理器之间的地开支的高速传输,经过同享总线可无缝链接多达8个TigerSHARC ADSP。FPGA加多个DSP的体系结构在通讯、图画处理、遥感观测以及雷达等范畴得到了广泛的运用。

2 依据TS201链路口的图画接纳技能

2.1 TS201链路口

TS201具有4位宽的4个双向LVDS(LOW Voltage Differential Signaling)链路口是其组成并行体系的要害。链路口是ADI公司提出的总线传输方法,链路口可以直接由处理器核操控,也可以由DMA操控器操控。链路口由发送端和接纳端两部分组成,以低压差分信号(LVDS)方法传输数据,可以高速精确的完结板内或许板问数据的传输,满意体系的实时要求。每个链路口的接纳和发送都有指定的DMA通道。经过编程操控可以将链路口设置成4位并行或许1位的方法进行传输。TS201支撑点对点的链路口通讯,可用于恣意的依照链路口协议规划的器材之间的通讯,每个链路口的数据传输率高达500 Mbytes/s,4个链路口传输速度到达4 GB/s。TS201链路口发送及接纳数据的通讯协议中最小传输长度为4字。在1bit形式下,传输4字需求64个时钟周期;在4bit形式下,需求16个时钟周期;

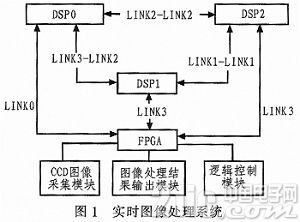

链路发送传输原理如图2所示。

当链路口的发送端发送数据时,首要检测链路接纳端LxACKI是否有用,有用后使能时钟信号LxCLKOUT,开端发送数据,LxBCMPO信号标明数据是否传输完毕;数据传输开端于第一个时钟的上升沿。完毕于最终一个时钟的下降沿;当传输完毕后,LxCLKOUT置为低。关于发送端,当LxACKI采样为高时,标明接纳端缓存闲暇,可以发送。

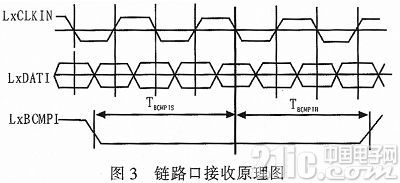

链路口接纳原理如图3所示。

在接纳方法中,当接纳端检测到LxACKO,有用后,时钟信号LxCLKIN开端传输,即开端接纳数据,LxBCMPI信号标明数据传输完毕。

2.2 直接存储器拜访DMA

TS201对图画的接纳可利用DMA进行。DMA(Direct Memory Access)是在处理器内核不干涉情况下的后台高速数据传送机制口,不占用DSP内核的处理时刻,TS201片内的DMA操控器答应将数据传输作为一个后台任务履行,从而将处理器核开释出来,进行其他数字信号处理操作。在杂乱信号处理体系中,特别是需求很多数据传输和搬移的操作体系,选用DMA方法可以开释处理器内核,进步作业效率。特别关于图画处理体系,可选用二维DMA数据传输方法,可以将图画数据块实时接纳到DSP中。

TS201有14个DMA通道。其间8个用于链路口。一个链路口有发送和接纳两个通道。DMA驱动传输仅答应4字传输,且支撑链路口DMA穿插传输。从发送链路到接纳链路的数据发送及接纳,要编程发送和接纳链路传输操控块寄存器TCB,发送数据到方针发送链路的缓冲区,DMA依据TCB编程和恳求发动一次传输。

2.3 传输操控块寄存器TCB介绍

传输操控块寄存器TCB是一个128位的四字组寄存器。

如图4所示:包含DI寄存器、DX寄存器、DY寄存器、DP寄存器。TCB包含了DMA传输的操控信息。

DI寄存器占TCB的0~31位,是32位DMA索引寄存器,用于设置要发送或接纳数据的源地址和意图地址,地址可指向内部,外部存储器及链路口。

DX寄存器占TCB的32~63位,假如传输的是二维数据的话,高16位是x方向计数值,低16位是x方向修正量。

DY寄存器占TCB的64~95位,DY寄存器和DX寄存器结合在一起运用,假如传输的是一维数据,不设置此寄存器,假如传输的是二维数据的话,高16位是Y方向计数值,低16位是Y方向修正量。

DP寄存器占TCB的96~127位,用于设置DMA传输的操控信息。包含TCB指针,链路指针选择器,链路意图通道,操作数据长度,二维DMA使能等。

3%20图画处理体系TS201链路接纳

在图画处理体系中选用了链路口接纳作为图画数据接纳方法。FPGA收集图画数据完结预处理后,将图画数据经过内部FIFO发送到高速链路口,经过链路口,将图画数据别离

传输到各个DSP。

图画处理体系中以DSP1获取FPGA传送的图画为例。

如图1所示:DSP1和FPGA之间经过链路口3(Link3)衔接,TS201%20Link3接纳通道对应DMA通道11。

链路口接纳过程如下:

1)翻开并答应DMA11中止。

2)设置DSP1链路口3接纳操控寄存器LRCTL,LRCTL寄存器好像5所示。

设置LRCTL3接纳使能,链路传输数据巨细形式等。代码如下:buihin_sysreg_write(LRCTL3,0x11);0x11的意义是使能Link3接纳,每次传送4 bit数据。

3)对DSP1 DMA11传输操控块(TCB)编程。

代码如下:

TCB_Link3R.DI=Image_Data;

TCB_Link3R.DX=4|(Img_Col16);

TCB_Link3R.DY=4 |(Img_Line16);

TCB_Link3R.DP=0x4fla0000;

Link3RecTCB=builtin_compose_128((TCB_Link3R.DI | TCB_Link3R.DX32,TCB_Link3R.DY |TCB_Link3R.DP32);

DI寄存器设置为二维图画接纳端的意图地址;DX寄存器为二维DMA的X方向传输的数据位数Img_Col,传送Img_Col个32bit数据,一个图画数据占16位,图画数据共Img_Col*2列;DY寄存器为二维DMA的Y方向传输的数据位数,传送Img_Line行数据,图画数据共Img_Line行;DP寄存器设置为二维链路口3接纳。

4 TS201各个DSP之间的通讯规划

实时图画处理体系中各个DSP之间的通讯规划选用链路口的方法。以体系DSP0和DSP1通讯为例,从图1可以看出DSP0 Link3衔接DSP1 link2,DSP0 link3发送通道为DMA7,DSP1 link2接纳通道为DMA10。

通讯过程如下:

1)翻开并答应DMA7,DMA10中止。

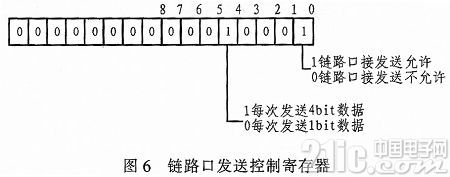

2)设置DSP0链路口3发送操控寄存器LTCTL,寄存器好像6所示。

代码为builtin_sysreg_write(LTCTL3,0x11);0x11的意义是使能Link3发送,每次发送4bit数据。

3)DSP0 DMA7传输操控块寄存器(TCB)编程,代码如下:

TCB_Link3Send.DI=(int *)DSP0SendData;

TCB_Link3Send.DX=4 |(DSP0SendData_Num16);

TCB_Link3Send.DY=0;

TCB_Link3Send.DP=0x47180000;

Link3_SendTCB=buihin_compose_128(TCB_Link3Send.DI | TCB_Link3Send.DX 32,TCB_Link3Send.DY | TCB_Link3Send.DP32);

DI寄存器设置为DSP0发送数据的源地址;DX寄存器为DSP0发送数据位数;DY寄存器为0阐明是一维DMA传输,DP寄存器设置为一维链路口3发送。

4)设置DSP1 link2接纳寄存器LRCTL,代码为builtin_sysreg_write(LRCTL2,0x11);接纳原理和DSP1 Link3接纳图画原理相同。

5)DSP1 DMA10传输操控块寄存器(TCB)编程,代码如下:

TCB_Link2R.DI=DSP1RecDSP0Data;

TCB_Link2R.DX=4 |((DSPlRecNum)16);

TCB_Link2R.DY=0;

TCB_Link2R.DP=0x47100000;

Link2_RecTCB=builtin_compose_128(TCB Link2R.DI | TCB_Link2R.DX32,(TCB_Link2R.DY |TCB_Link2R.DP32));

DI寄存器设置为DSP1接纳数据的意图地址;DX寄存器为DSP1接纳的数据位数;DY寄存器为0阐明是一维DMA传输,DP寄存器设置为一维链路口2接纳。留意DSP1接纳的数据长度DSP1RecDSP0Data和DSP0发送的数据长度DSP0SendData要共同。

5 定论

介绍了依据TS201+FPGA的施行图画处理体系中关于TS201链路口通讯的二维实时图画获取以及多DSP之间链路口通讯。给出了通讯时序图,要害代码,要害寄存器设置,保证了实时体系中的图画数据可以按帧获取及多DSP之间的实时通讯,保证体系的实时性。