当共模信号较难处理或对体系有负面影响的时分,需求进行信号调度。部分体系的规划会将模仿变换器输出的单端信号转为全差分信号,然后将这些信号传送到差分输入ADC。这种规划的长处是,大部分混入差分线路的噪声会一同出现在两条线路上 (假定差分线路都是按差分方法平衡布局)。

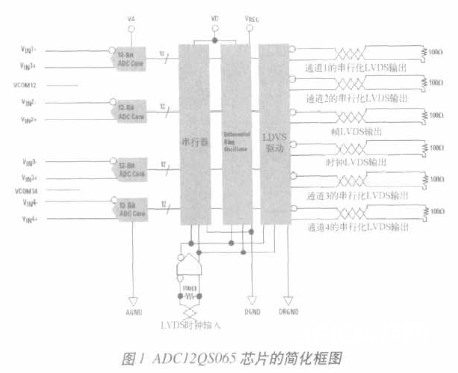

输入信号转为数字信号之后,便有必要传送到DSP或ASIC/FPGA,以便进行处理。全差分输出信号电路通过两条对称的线路输出及吸收电流。低电压差分信号 (LVDS) 就是这种信号。ADC12QS065 芯片就选用了 LVDS 技能,可解决体系这方面的问题 (见图 1)。

ADC12QS065内含 4 个 12 位的ADC。芯片的每一个输入端都可接纳全差分信号。此外,这款芯片一同供给的共模输出参阅电压 VCOM12 及 VCOM34 也可用作输入共模电压。ADC12QS065也可选用全差分或单端的时钟源,只需为 CLK 及 CLKB 供给 LVDS 信号,便可运用 LVDS 时钟,但要在挨近输入引脚的方位加设终端电阻。若要运用单端 CMOS 时钟,便要将 CLKB 置于低电平,这样便无需加设终端电阻。

每一个ADC将输出信号串行输出。输入时钟的输入12倍频之后,作为 LVDS 时钟输出,作为数据采样时钟。输出端也会依照输入时钟速率发生 LVDS 帧信号,以便承认取样数目。

输出守时将 FPGA 的数据采样简化。当取样数据可送出时,首要输出帧信号,然后是每个通道的高有效位数据,并输出一个LVDS时钟跳变沿信号。LVDS时钟信号会相对数据输出偏移1/4周期,以便简化时钟办理。每一数据位在时钟输出转化时采样。选用 LVDS 传输技能还有另一长处,即这些信号能够通过契合 EIA/TIA 568 规范的双绞线传送。契合这个规范的双扭线有 100的特性阻抗。两根导线距离很近,电流方向相反,只会发生很少的辐射。关于信噪比要求极高的运用来说,这个长处极为重要。

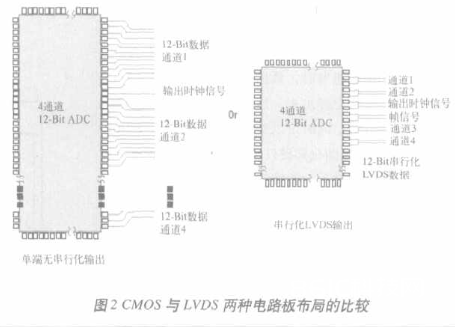

这儿运用图2所示的两款 4 通道、12 位ADC进一步解说这一点。左面的ADC设有传统的单端并行 CMOS 输出。若要将转化器的输出信号传送给DSP,便需求 49 条连线 (4 x 12 + 1)。若输出信号通过串行化处理之后,每一通道仅需求一对差分信号传输线。一同也需求输出时钟及帧信号。

因为 LVDS 芯片将电源供给的电流从一端送到另一端,因而 LVDS 芯片从电源吸收的电流是接连的,会下降电源的负载改变。这样做的长处是能够削减供电线路上因负载呼应发生的噪声,削减去耦电容器的体积以及下降布局的要求。

串行 LVDS 芯片能够选用较小的封装,并更有效地传送高速信号。但关于许多运用来说,低功耗的特性极为重要。以具有多条数据通道的体系为例,每一通道所节约的每一 mW 功率加起来便有很大的别离。因而 ADC12QS065除了设有几个无噪声驱动器之外,还设有三个独立的电源输入。每一个电源输入都能够衔接在一同,成为一个单电源ADC。但这三个电源输入也可分隔,各自独立操作,为每一电源输入独自规划无源滤波器,或爽性运用三个独立的电源。三个电源各自独立操作的另一长处是能够将驱动器的输出电压下降至 2.5V,这样有助于下降功耗。

ADC12QS065 也可将其内部电压参阅电路封闭,以便由外部参阅源驱动。只要将一切 VREFP 及 VREFN 各自连在一同,便可将多个ADC捆缚一同。这样做能够保证每一芯片的增益及电压偏移保持一致,令体系更简单校准。

责任编辑:gt