一种智能信号转化模块的规划办法。这种智能模块选用了根据FPGA嵌入式软核体系,是根据NiosII软核处理器的架构,能够在模块上彻底完结外部总线信号之间彼此转化,无需驱动程序或操作体系的干涉。一起对用户逻辑规划、用户逻辑集成、固件规划技能等内容进行了具体的介绍。

0 导言

在工业操控等范畴的计算机体系中广泛涉及到信号转化等,信号转化模块在体系中承担着在多种信号之间进行翻译转化的使命。跟着运用环境复杂性、计算机体系集成度的进步,信号转化模块上需包容的信号通道的品种与数量也越来越多。频频、很多的信号转化必然会占用较多的体系资源。跟着微电子技能的开展,国外的一些出产厂商如Altera已推出在FPGA上以软核(soft core)办法完结的嵌入式体系。这种嵌入式体系根据NIOS II嵌入式软核处理器,其外设能够灵敏挑选增删,并答应自定制外设。本文介绍了一种根据NIOSⅡ软核体系的智能429-422信号转化模块的规划。

1 规划原理

传统的非智能规划的转化模块,在作业时需求有驱动程序的操控,经过与操作体系或用户软件的交互,来完结信号转化的功用,亦即需求接入PCI Bus等体系总线,经过中止提请等办法作业,在转化通道数量多时,必然会影响体系的功能。选用智能规划的信号转化模块一般不需求操作体系的干涉,接纳到的外部总线信号经过本模块上NIOS II软核体系转化后,即可将数据信号输出。信号转化的作业悉数由模块的硬件完结,因此能够完结对整个计算机体系资源的零占用。选用非智能规划与智能规划模块的结构暗示框图如图1所示。

2 硬件规划

429或422总线适配电路已有很多老练的规划,本文不再赘述,仅要点介绍FPGA内部总线操控逻辑规划以及NiosⅡ软核体系的装备。

2.1 FPGA操控逻辑规划

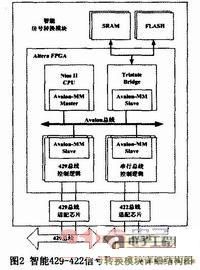

集成于FAPGA内部的Nios II CPU需求经过外部总线操控逻辑才能与外部总线进行通讯,而Avalon总线是Nios II CPU与外部总线操控逻辑、片外FLASH、SRAM之间交流数据信号的纽带。Avalon总线是一种协议较为简略的片内总线,在NiosⅡ体系中,外设都是经过Avalon总线与Nios II CPU相接的。Avalon总线接口能够分红两类:Slave和Master,Slave和Master首要区别是关于Avalon总线操控权的把握。Master接口具有与之相接的Avalon总线的操控权,而Slave接口是被迫的。Avalon总线支撑自定制外设,用户可将自己的逻辑规划挂接到Avalon总线上。根据NIOSⅡ软核体系的智能429-422信号转化模块规划的具体体系结构框图如图2所示。

2.1.1 串行总线操控逻辑规划

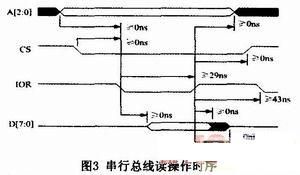

为了将用户自定制的串行总线操控逻辑接入NiosⅡ体系,有必要将其挂入Avalon总线。串行总线操控逻辑在规划上有必要完结两类端口:一类为Avalon总线端口,Avalon总线时序由NiosⅡ体系完结,用户在逻辑规划时可暂不作考虑;另一类为串行总线操控端口。串行总线读操作时序如图3所示,图中给出了操作时各信号的时序坚持联系。

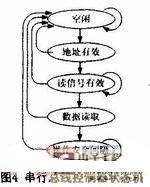

读时序在规划上能够笼统为一个有限状况机,如图4所示。其作业流程为:无数据传输时,状况机停留在闲暇状况;若有数据操作恳求时,进入“地址有用”的状况;再进入“读信号有用”状况,顺次完结“数据读取”、“操作安全距离”状况(FPGA片外器材要求的两次操作之间的最小距离)。考虑到反常发生后状况机的稳定性,每个状况都能够在反常发生时返回到默许的“闲暇”状况。一起,有些状况作了些等候延时,是为了让操控逻辑与FPGA外部较慢速的器材进行时序匹配。串行总线写操作时序与读操作时序相相似。

2.1.2 429总线操控逻辑规划

429总线操控逻辑规划和串行总线操控逻辑规划办法与上文所述相似,这儿不再重复。

2.2 NiosI%&&&&&%PU的装备

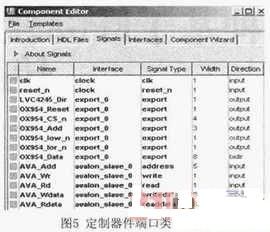

需求将自定制外设集成进嵌入式体系。本规划所运用的FPGA是Altera公司的EP2C35,可在Altera公司推出的开发软件Quartus II里对NiosⅡCPU进行装备。操作过程为:在System contents中新建一个组件,在弹出的Component Editor窗口中的HDL Files栏中导入用户规划好的422接口操控逻辑规划的verilog文件;Signals一栏中,Component Editor已主动解分出导入的verilog文件所包含的端口Name,但用户还需对端口的类型进行指定,串行总线方向的端口须指定为export(相关于Avalon Slave端口而言)类型,Avalon总线方向的端口别离指定为规范的address、write、read、writedata、readdata等信号,如图5所示。

设置完结后的自定制器材出现在Custom Devices中,能够将自定制的器材加入到Nios Ⅱ体系中,由Nios Ⅱ体系为其主动批定内存地址等资源。编译无误后即可完结NiosII CPU的设置。

3 软件规划

Nios II嵌入式体系运用Altera公司供给的开发环境Nios Ⅱ IDE,Nios II IDE运用规范的C/C++言语作为编程言语,因此开发入门门槛不高。软件规划时,除了包含指定的system.h,alt_main.h等头文件,用户应针对被集成进入体系的自定制器材编写相应的头件,行将Al-tera供给的根本指令从头封装成用户自定义的软件指令,以运用户的程序愈加直观、更具有可读性。

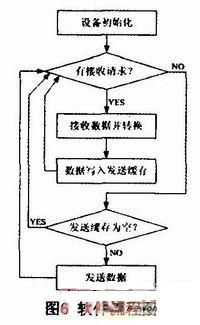

软件流程图如图6示。在每次上电复位后,智能模块应对整个体系进行从头初始化,包含外设操控字的装备以及缓存初始化等作业。初始化完结后,应首要查看有无接纳恳求,如有恳求,则开端接纳、转化数据,并写入发送缓存,然后再判别一次有无接纳恳求,如无,才转入发送流程。发送完一次数据后,再次查看接纳恳求。这种做法进步了数据接纳事情的优先权,能够确保接纳数据不丢掉。

4 结束语

根据NIOSⅡ软核体系的智能429-422信号转化模块选用了智能化的规划技能,比照于非智能信号转化模块,具有零体系资源占用、可装备性强、转化速度快等特色,一起因为无须开发驱动软件,因此显着缩短了研制周期,在工业操控等计算机体系中将会有广泛的运用。