嵌入式设备因为具有硬件可在线装备,完结灵敏等特色,使得其运用越来越广泛。尤其在根据FPGA的硬件体系中运用较多,现在在许多产品中完结了嵌入式网口、嵌入式PCI/PCI-E、嵌入式USB等各种模块。但在DSP中完结嵌入式设备还比较少,一般DSP都直接集成这些设备模块,用户挑选不同类型的DSP芯片以满意产品运用要求。但关于一些较为特别的嵌入式设备,DSP也能够完结该功用。

TI公司的DSP芯片C6727B,因为其片内集成dMAX模块,使得完结嵌入式FIFO成为可能。其完结嵌入式FIFO的实质便是将DSP的片内一段RAM空间设置成FIFO空间,FIFO和外部设备的数据交换由EMIF接口完结。该FIFO的数据读写不需求DSP的CPU参加,然后进步整个体系功用,完结数据交换和数据处理的一起进行。本文以dMAX和EMIF接口的数据传输为例,介绍嵌入式FIFO的规划、装备及其运用。

dMAX及其结构

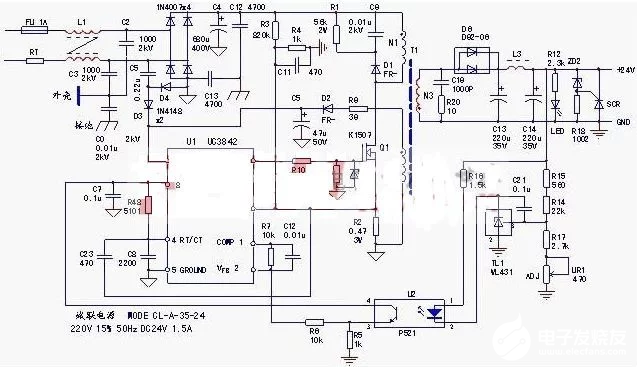

dMAX(Dual Data Movement Accelerator,双向数据传输加速器)是TI公司的DSP芯片C6727B特有的一种片内设备。运用dMAX和EMIF(External Memory Interface,外部存储器接口)能够完结片内RAM、片内和片外设备以及两个片外设备之间的数据传输。dMAX模块的内部结构如图1所示。

图1 dMAX内部结构图

从图中能够看出,dMAX首要由事情和中止处理模块、事情编码器、传输事情模块等组成。事情模块分红高优先级和低优先级两个彼此独立的模块,各自有独立的事情进口和事情参数表,和CPU有独立的接口。使得dMAX能够一起处理两个不同的事情。当拜访CPU端口时,MAX0的优先级高,MAX1的优先级低。dMAX能够经过履行先进的一维、二维与三维数据的存储器传输作业,然后使DSP得以专心于信号处理使命,明显进步体系功用。合适图画的子帧提取或许语音信号的子信道提取。

DSP内部的数据交换中心在dMAX的操控下,能够完结片内RAM、EMIF以及HPI接口之间的数据交换。本文介绍在dMAX操控下,完结片内RAM和EMIF接口之间的数据交换。假如DSP选用一般的异步接口方法,数据传输需求树立、选通和坚持3个阶段,最少需求5个EMIF时钟(树立和坚持各1个时钟,选通3个时钟)。为了确保通讯的牢靠性,一般选用10个EMIF时钟(树立3个时钟,坚持2个时钟,选通5个时钟)。而EMIF时钟最快为133MHz;这样,选用异步接口的通讯速率一般为13.3M×32b/s(选用32位数据总线宽度)。此外,异步接口数据传输必须在CPU的参加下,运用指令完结数据搬移。将占用许多的CPU开支,在许多高速的数据收集和处理中,将下降体系的全体功用。为此,选用dMAX完结嵌入式FIFO数据传输战胜异步传输的缺陷,其传输选用突发读写方法进行,能够接连突发读写8个数据,总共只需求20个时钟,通讯速率进步为53.2M×32b/s,进步4倍读写速率。还能够选用和DMA后台运转,这样将大大下降整个体系数据读写的开支,然后能够完结愈加杂乱和牢靠的算法处理。

嵌入式FIFO规划

嵌入式FIFO的规划首要便是操控FIFO的7个参数。这7个参数分别为基地址、空间巨细、空标志、满标志、过错标志、读指针和写指针。它们之间的联系如图2所示。

图2 FIFO结构示意图

基地址和空间巨细用于规划出一段内存空间,该内存空间用于FIFO设备,并被FIFO设备维护起来,使得其他设备和程序不能拜访该空间。为了便于操作便利,空间巨细一般为2的整数次幂,但不做要求。详细到C6727B类型的DSP,空间巨细最大为1M个元素,元素巨细能够是8位、16位或许32位数据,不能为其他类型的数据。基地址能够为内存空间的任何一个地址,相同为了操作便利,一般为空间巨细的边界点。例如,8个元素的FIFO,其基地址一般为XXXXX000b,也便是地址的低3位为0,基地址就肯定为8的整数次。相同,64个元素的FIFO,其低6位为0。基地址和空间巨细的特别要求防止拜访时的地址跨越多页问题,能够进步FIFO的拜访速度。

空标志和满标志用于表明FIFO的存储状况。读指针和写指针用于表明读写的当时地址。过错标志表明对FIFO的过错操作。当FIFO处于满标志情况下依然写FIFO,或许FIFO处于空标志情况下依然读FIFO,FIFO都将停止当时操作,并将过错标志置位。

FIFO的写操作只要一种作业方法,即每次写一个新的数据,写指针加1,直到写满。而FIFO读操作有两种作业方法,分别为规范操作和多阶推迟(Multi-tap Delay Transfer)操作。规范操作和写操作相同。多阶推迟操作一般用于滤波处理,当需求对输入信号进行滤波处理时分,每次期望从FIFO读取一段窗口的数据,进行滤波处理,数据窗口依然只移动一个数据。在规范操作情况下,假如读取一段窗口的数据,FIFO则将该段窗口的数据悉数弹出。多阶推迟操作则只弹出一个数据。该操作方法对语音或许AD采样数据的滑润、FIR等滤波十分适用。需求留意的是,多阶推迟操作的数据窗巨细需求设置,假如FIFO存储的数据个数小于数据窗,FIFO则停止当时操作,并给出过错标志。

体系硬件结构

C6727B和其他DSP有一个较大的差异,便是C6727B不再供给专门的外部中止引脚,而是选用GPIO引脚和dMAX合作运用,经过寄存器的设置将GPIO引脚装备成外部中止引脚。本文为了完结FIFO的实时操作,一旦外设向FIFO写入数据,即宣布中止信号到DSP的CPU,告诉CPU读取数据。为此,需求运用1个外部中止引脚,将C6727B的音频串口的AXR[8]装备成通用的GPIO引脚,并在dMAX中设置成中止引脚。此刻需求将音频串口的CONFIGMACSP0寄存器设置为0x0001,如图3所示。此刻音频串口不能再作为一般的音频口运用,而是装备成IO接口。

图3 中止功用设置框图

从图3中能够看出,装备好音频串口后,一旦AXR[8]引脚有上升沿到,则McASP0激活dMAX的事情26,向CPU发送内部中止13。McASP的与中止相关的寄存器装备是完结以上计划的要点。运用PFUNC寄存器将其装备成通用IO引脚;PDIR寄存器操控IO引脚的方向;假如是输出引脚则由POUT引脚输出凹凸电平,假如是输入引脚,则由PDIN寄存器读出该引脚的状况;此外,能够运用PDCLR和PSET寄存器铲除或许设置输出引脚的状况。

体系软件规划

体系软件规划首要包含McASP的初始化、dMAX的初始化、FIFO的初始化、中止使能等。体系主程序只需求等候中止进行相应的处理,首要的数据传输作业都是dMAX依照软件装备主动完结,不需求CPU参加。图4是完结由外设写FIFO,DSP读取FIFO数据的流程。图中虚线部分表明由dMAX独立完结的作业,实线部分表明由CPU完结的作业。两者之间经过内部中止方法完结状况的沟通。

图4 体系软件流程

为了进步FIFO的读写速率,一般选用突发方法进行读写。突发方法的读时序如图5所示。写时序和读时序相似。突发方法一次最多只能读写8个数据,也能够一次突发读写4个或许2个数据。突发读写时数据的树立和坚持时刻最少能够设置成1个时钟周期,如图中所示。但为了通讯牢靠,一般选用2个时钟周期。突发方法最大的节省时刻是接连的其他数据将不再需求树立和坚持周期,而是直接进行读写,一般只需求两个时钟周期就能够完结一个数据的读写。最快情况下,突发读写8个数据只需求20个时钟周期,读写速率到达53.2M×32b/s,满意大部分设备的要求。

图5 突发读时序图

总结

dMAX的特有结构使得其能够完结嵌入式FIFO。本文介绍了根据C6727B的dMAX的根本结构以及根据dMAX的嵌入式FIFO软硬件规划,设置通用GPIO引脚作为中止,为了加速FIFO的传输速率,运用突发读写方法进行数据传输。嵌入式FIFO的完结,使得DSP和外部设备的通讯愈加便利和方便,并且不需求CPU的参加,减轻了CPU的担负,CPU能够专心于杂乱的算法处理。