依据灵敏自适应的空口波形技能FOFDM(Filtered OFDM)是现代通讯技能的研讨热门,规划并完结可调FIR滤波器是完结该技能的中心作业之一。本文规划的依据FPGA的可调理FIR滤波器系数的自适应调整是经过操控算法对信道中的信号进行快速检测,然后将作用和滤波器的输出作用进行差值核算进行反应调理。运用Quartus II和DSP Builder规划依据FPGA的16阶系数可调FIR滤波器,给出中心模块的规划电路图和仿真作用。仿真作用表明:依据灵敏自适应空口波形技能能够在FPGA上完结,并且由于FPGA具有天然的并行性,实践的通讯体系中能够选用并发形式进行,到达进步信号传送速率的意图。

0导言

4G移动通讯方兴未已,业界关于5G移动通讯技能的评论现已如火如荼。作为移动通讯范畴“皇冠”上的一颗明珠,依据灵敏自适应的空口波形技能和成倍提高频谱功率的多址技能SCMA(Sparse Code MulTIple Access)成为业内人士重视的焦点,其间,优化频带资源的运用率是FOFDM的中心。人们在研讨算法优化的一起,也在重视算法的硬件完结。FPGA(Field Programmable Gate Array)在能耗、本钱、运算速度等方面具有得天独厚的优势, 现已被广泛应用于各种数字信号处理和数字通讯范畴。本文要点研讨FOFDM中心技能之一的可调FIR滤波器,规划并完结依据FPGA的可调理FIR滤波器。

近年来,依据FPGA的数字滤波器研讨现已取得了许多作用。可是,从现有的文献来看,并没有可供参考的用于依据自适应的空口波形技能的办法。本文第1节为中心模块规划,第2节为MATLAB仿真作用和体系仿真作用,第3节给出了根本定论和下一步研讨方针。

1依据FPGA的可调FIR滤波器规划

该规划整体思路是:运用输入波形的各项参数,凭借MATLAB中的FDAtool东西核算出FIR滤波器所需参数,存入RAM。滤波器中心模块读取参数信息,调理滤波器的截止频率等参数,调理该模块的功用。

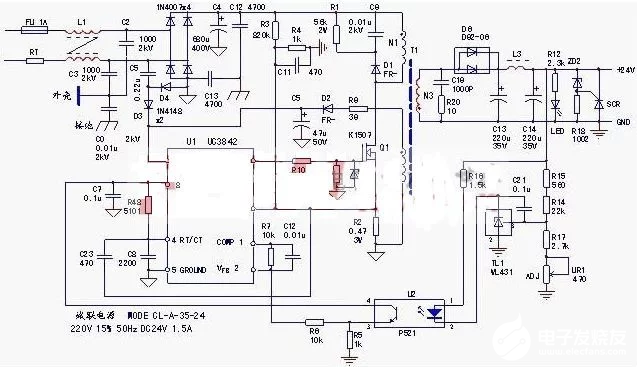

运用DSP_Builder开发中心滤波器模块的流程示意图如图1所示。

最根本的FIR滤波器的体系函数为:

能够用卷积表明为:

y(n)=x(n)*h(n)(2)

例如,一个典型的直接型4阶FIR滤波器,其表达式[11] 可写为式(3):

h(n)=h(0)x(n)+h(1)x(n-1)+h(2)x(n-2)+h(3)x(n-3)(3)

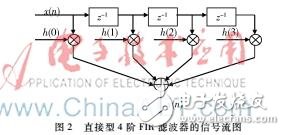

在图2中,一共存在3个延时单元、4个乘法器和一个4输入的加法器。

假如运用一般的数字信号处理器来完结这个4阶FIR滤波器,只能用串行的办法次序地履行延时、乘、加操作。这有必要用到多个指令周期,而无法在一个指令周期内完结。可是假如选用FPGA来完结,就能够运用FPGA指令能够并行的长处,在一个指令周期内得到作用。

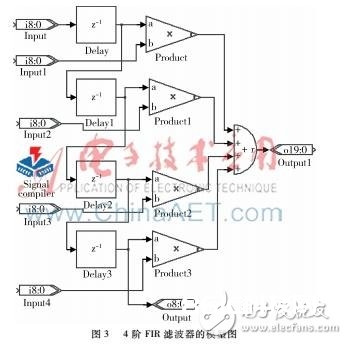

依据公式(3)和图2,能够在Simulink顶用DSP_Builder里的相关器材画出一个图3所示的4阶FIR滤波器模型。

图3中“Delay”为延时单元,“Product”为乘法器单元,“ParallelAdderSubtractor”为加法器单元,“Input”与“Output”分别为输入输出。

(1)规划4阶FIR滤波器子体系

新建一个文件,将子体系模块(Subsystem)放入文件中,双击翻开子体系模块,将上面现已规划好的4阶FIR滤波器放进去,并对端口进行修正。修正后的Subsystem模块有5个输入和2个输出,“input”与“output”都修正为“Altbus”(由于它们不再作为主输入端口,而是作为子体系的传输端口)。

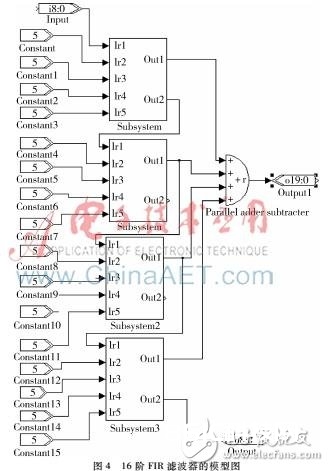

(2)规划16阶FIR滤波器

4阶子体系完结后,依照图4建立一个16阶的FIR滤波器。其间Constant模块的初始值为5,需求别的核算,下文解说怎么核算Constant值。

(3)核算Constant的值

Constant的值就相当于h(n),是决议FIR滤波器详细功用的重要参数,该值为滤波器要调理的中心参数,它是经过滤波器的输出和输入信号的差值得到的。

(4)导出参数

点击左上角的File,单击Export,跳出Export界面,点击下方的Export按钮,能够将16个参数导出到MATLAB的主窗口。

(5)将参数填入FIR滤波器的模型中

在MATLAB仿真阶段,该参数能够手动输入到FIR滤波器Constant模块中,这样便完结了一个16阶低通FIR滤波器的规划。在体系规划阶段,过程(4)核算作用会暂存在定制的RAM模块中。

2规划验证

2.1中心模块仿真

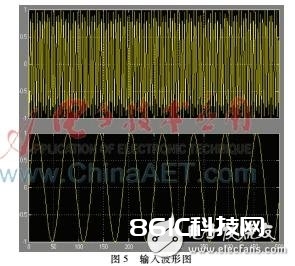

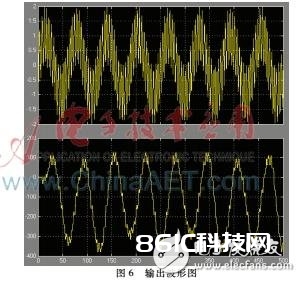

为了验证规划的16阶FIR滤波器正确与否,需求进行仿真。为此,给滤波器的输入端加上一个混合信号,混合信号包括一个40 Hz的高频信号和一个0.013 Hz的低频信号,两个信号由Add模块相叠加,再分别加上示波器模块“Scope”来显现波形作用。FDAtool设置就和上文所述相同,并将所得数据填入Constant模块中,仿真时刻设为500 s。

图5的上方为40 Hz的波形,下方为0.013 Hz的波形。图6的上方为输入的混合信号波形,下方为滤波器输出波形。将两幅图比较能够显着看出,高频信号40 Hz的波形被滤除,滤波器输出的是低频的0.013 Hz的信号。

2.2体系仿真

(1)将将mdl文件编译生成VHDL言语;

(2)核算输入信号和滤波器输出的差值,将该值存入RAM;

(3)读入RAM数据,逐步确认滤波器截止频率;

(4)仿真。

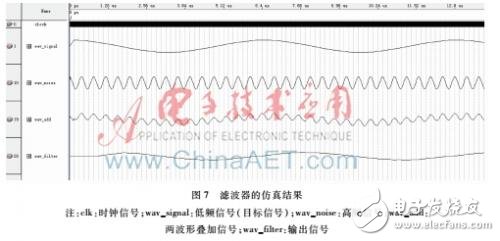

为了验证所规划的可调FIR滤波器的正确性,规划了依据上述模块的低通滤波器进行波形的仿真。两个正弦波叠加构成输入信号,一个25 kHz信号人为标记为噪声信号,另一个4 kHz作为方针信号,程序调理滤波器的截止频率到4.5 kHz。仿真作用如图7所示。由图中可知,该滤波器滤除了高于截止频率的信号部分,保留了低于截止频率的信号部分,因而滤波器功用正确。调理输入信号和截止频率后,作用也能到达如图7所示的作用。

3定论

本文FPGA规划了一种可调FIR滤波器,运用DSP Builder结合MATLAB的优势将该滤波器的规划简化为MATLAB Simulink规划,大大缩短了规划时刻。未来将进一步完善可调滤波器规划,探究依据FPGA的可调FIR滤波器在实践通讯体系中的完结办法,进而提高通信体系功率。