文章转自ADI官网,版权归属原作者一切

曩昔,恣意波形发作器最扎手的部分是输出级的规划。典型信号发作器的输出规模在25 mV 到5 V 之间。为了驱动一个50 Ω 的负载,传统规划选用高功用分立式器材,并联很多集成器材,或许本钱贵重的ASIC,而要构造出安稳且可编程规模较宽的高功用输出级,规划师往往要投入很多小时的时刻。现在,技能前进带来的扩大器能够驱动这些负载,下降输出级的杂乱性,一起还能削减本钱、缩短上市时刻。

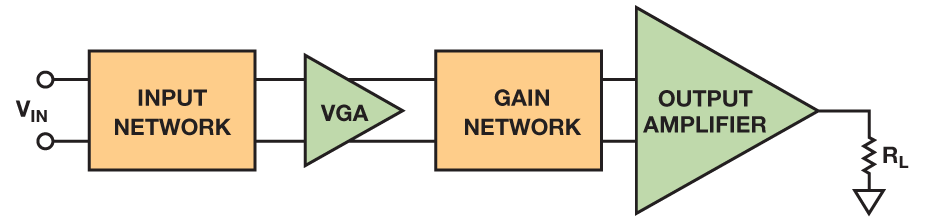

在运用通用信号发作器时,先输入一个频率,然后按下一个按钮,终究仪器发作一个新的频率。接下来,输入所需输出功率,再按下另一个按钮。在切换内部网络、调整输出电平常,继电器宣布咔哒声。这种非接连运转形式是补偿宽可编程规模缺失问题的必要条件。本文提出一种新的架构,它能够处理输出级规划中的一半问题。

战胜这个前端规划应战的两个要害组件是:供给高速、高电压和高输出电流的高功用输出级;以及带接连线性dB 调谐的可变增益扩大器(VGA)。这种规划以20MHz 的功用为方针,起伏为22.4 V(+39 dBm),负载为50 Ω。

新式紧凑式输出级

初始信号或许来自数模转化器(DAC)以发作杂乱波形,也或许来自直接数字频率组成(DDS)器材以发作正弦波。任一情况下,其规范和功率调整才能都或许达不到抱负状况。第一个要求是用VGA供给衰减或增益。但许多VGA 供给的增益是有限的,往往不足以在本运用中发挥作用。

假如VGA 的输出能够设为方针电平,则不管输入为何,都能够强制输出已知起伏。例如,假如所需输出起伏为2 V,且功率输出级的增益为10,则VGA 的输出起伏应调理至0.2 V。当输出级规划正确时,输出起伏终究由VGA 输出设定。不幸的是,大都VGA因可编程规模有限而成了瓶颈问题。

AD8330是完结50 dB 规模的首款VGA,但AD8338则树立了新的标杆,这款新式低功耗VGA 具有高达80 dB 的可编程规模。典型的高品质信号发作器的输出起伏规模为25 mV 至5 V。高达46 dB的可调规模超越了市面上大都现有VGA 的才能规模。抱负条件下,经典信号发作器的输出起伏或许为0.5 mV 至5 V,无需运用继电器或开关网络。满量程接连可调,不存在开关和继电器的非接连性问题。别的,不必继电器还能够延伸仪器寿数,前进体系可靠性。

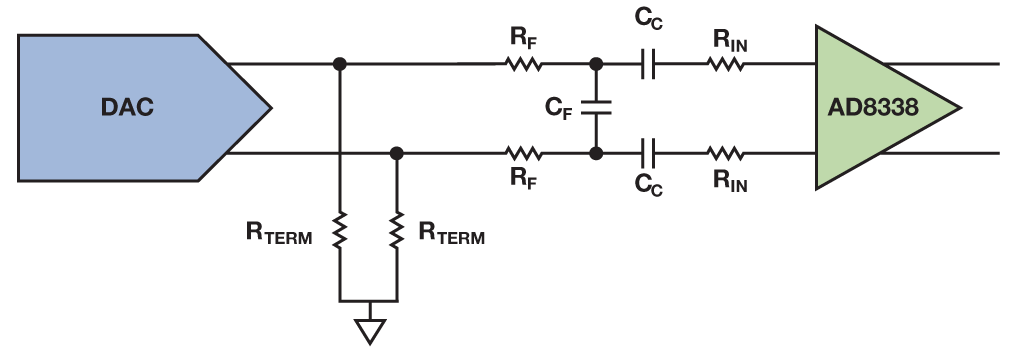

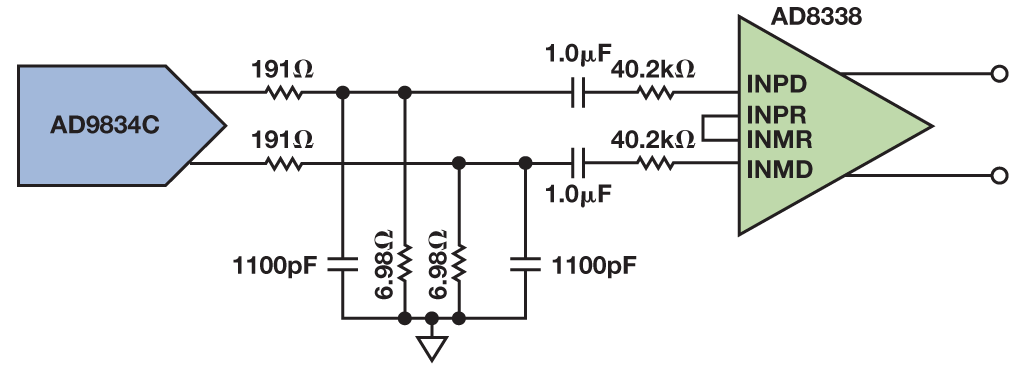

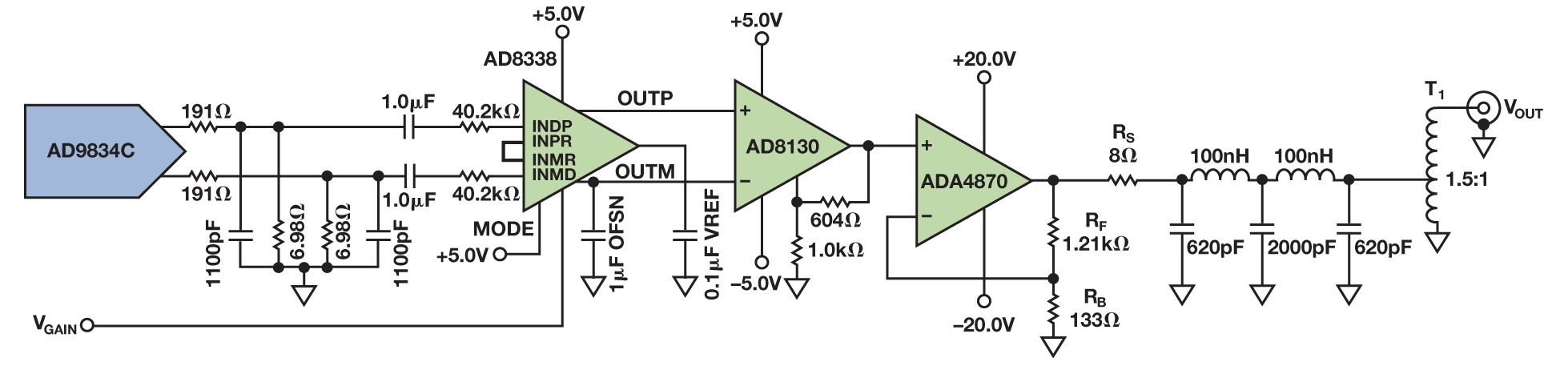

现代DAC 和DDS 器材一般搭载差分输出,要求规划师运用一个变压器,用单端衔接丢失一半信号,或许添加一个差分转单端转化器。AD8338 具有天然的适用性,供给全差分接口,如图3 所示。关于正弦波运用,用DDS 代替DAC。

AD8338 的一个首要特点是灵敏的输入级。作为一款输入VGA,它经过ADI 研究员Barrie Gilbert 创造的”H-amp”拓扑结构来操控输入电流。该规划用反应来平衡输入电流,一起使内部节点电压保持于1.5 V。正常条件下,运用500 Ω 输入电阻,最大1.5 V输入信号会发作3 mA 的电流。假如输入起伏较大,比方15 V,则将一个较大的电阻衔接至”直接”输入引脚。该电阻的巨细有必要适宜,以得到相同的3 mA 电流:

|

(1) |

单端15 V 信号将以差分办法输出1.141 V。此刻,最小增益条件下,AD8338 供给28.4 dB 衰减,因而,最大或许增益为+51.6 dB。作为一种低功耗器材,在1 kΩ 负载条件下,典型输出摆幅为1.5 V。

输入VGA 的功率有必要满意以下条件:其总增益规模在不同设定点周围。首要,确认信号发作器发作最大输出需求的输出电平。许多商用发作器为50 Ω 负载(正弦波)只供给250 mW rms (+24 dBm)的最大输出功率。这无法满意需求更多输出功率的运用需求,比方测验高输出高频扩大器、超声脉冲发作等。

电流反应扩大器(CFA)技能的前进意味着,这不再是个问题。ADA4870CFA 能够用±20 V 电源驱动1 A(17 V)。关于正弦波,能够在满负载条件下输出最高23 MHz 的频率,使其成为新一代通用恣意波形/信号发作器的抱负前端驱动器。

关于反射灵敏型50 Ω 体系来说,ADA4870 要求一些无源器材使源阻抗与50 Ω 负载相匹配:一个阻性焊盘和一个1.5:1 RF 主动变压器。在1 V 裕量条件下,当扩大器有用负载为16 Ω 时,可取得8 W 峰值功率。别的,假如反射不构成问题,则可移除阻性焊盘,并用匝数比为0.77:1 的变压器代替主动变压器。无阻性焊盘地,输出功率增至16 W峰值(28.3 V 起伏)。

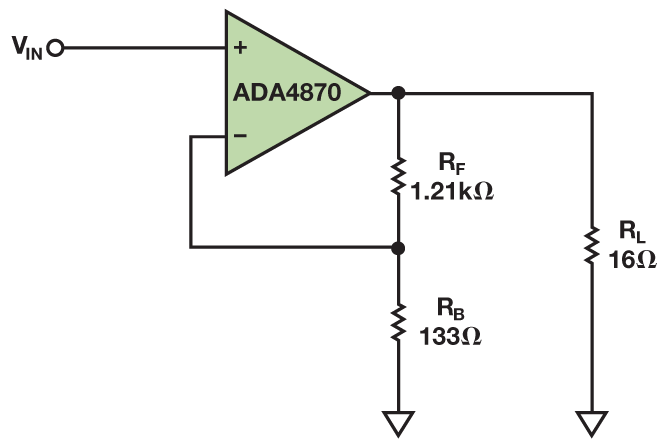

为优化输出信号摆幅,咱们将ADA4870 的增益倍数装备为10,因而,所需输入起伏为1.6 V。ADA4870 有一个单端输入,AD8338有一个差分输出,因而,AD8130 差分接纳扩大器及其270 MHz增益带宽积和1090 V/μs 压摆率可一起供给差分至单端转化和所需增益。AD8338 的输出约束为±1.0 V,因而,AD8130 有必要供给1.6 V/V 的中心增益。组合起来时,三个器材构成一个完好的信号发作器输出级。

完结整个规划还需求终究两个过程:装备输入网络以完结最大输入信号和抗混叠,规划输出网络以完结阻抗转化。

AD8338 输入网络

关于该规划,差分输出起伏为±1.0 V。在工厂默认设置、内部500 Ω电阻和最大增益条件下,输入起伏必定是100 μV。经过向直接输入引脚添加电阻,规划师能够调理该要求。由输入电阻决议的增益规模为:

|

(2) |

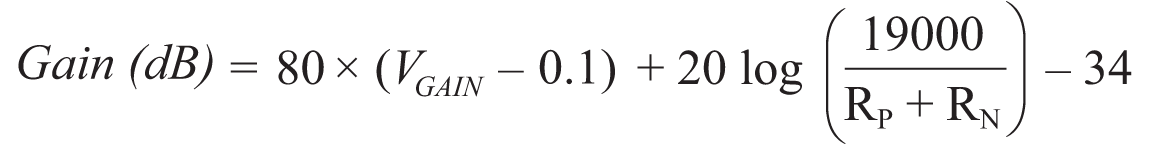

在各输入端运用40.2 kΩ 的电阻,能够在噪声功率与输入衰减之间 完结杰出平衡。当VGAIN = 1.1 V(最大增益)时,增益为:

|

(3) |

此刻,差分输入只需为21 mV。

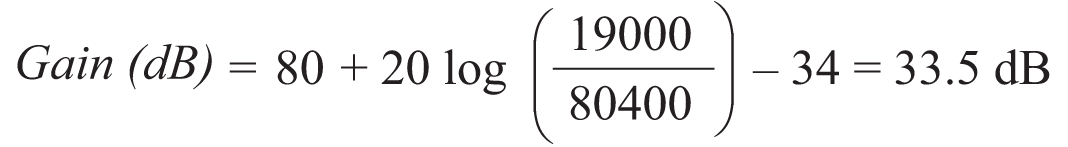

当VGAIN = 0.1 V 时,增益为:

|

(4) |

关于相同的21 mV 输入,输出约为100 μV。

考虑AD8130和ADA4870 的总增益,约为24.1 dB,ADA4870 的输出起伏规模为1.6 mV 至16 V。在阻性焊盘和主动变压器之后,输出端的电压将在2 mV 到20 V 之间。

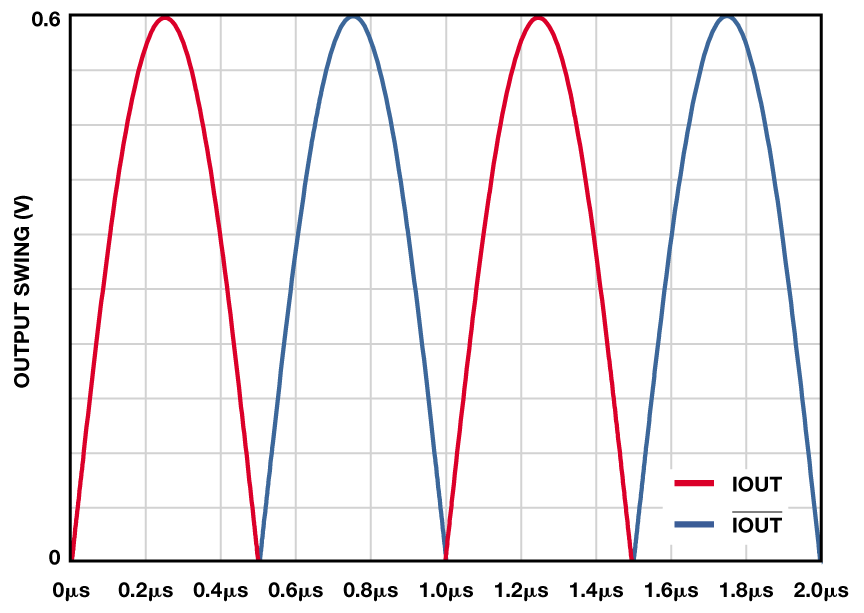

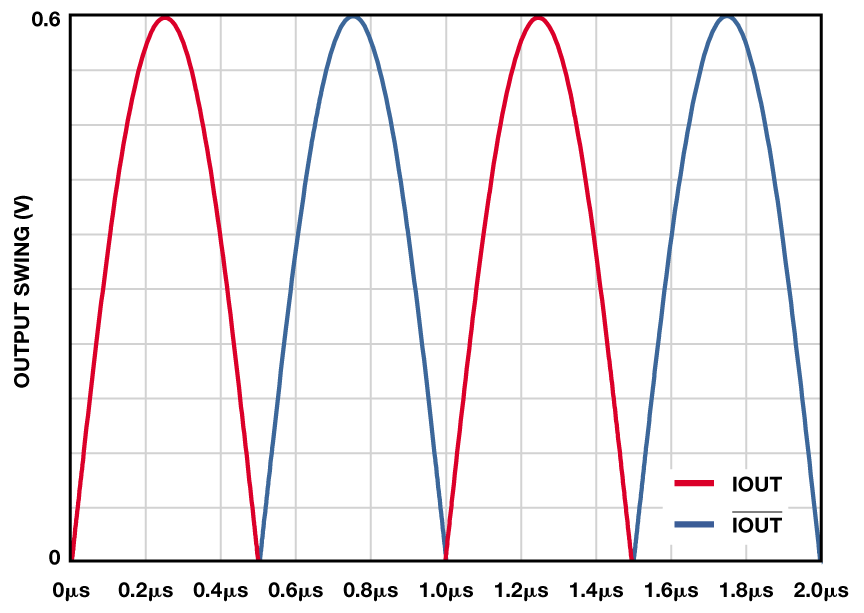

把AD8338 衔接至DDS 等器材,要求考虑抗混叠和输入衰减。例如,差分输出AD9834CDDS 要求200 Ω 电阻接地,以完结正确的摆幅。每个输出只会发作一半的正弦波信号,如图6 所示。

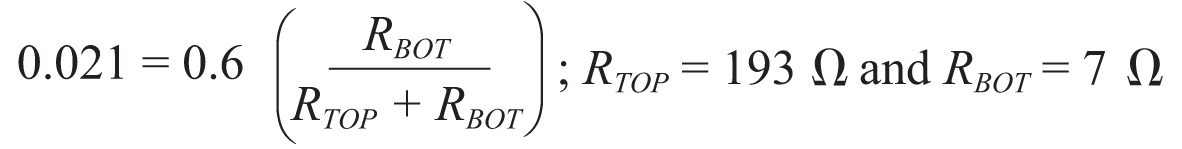

每个输出峰值为0.6 V,使得有用输入为±0.6 V,所需衰减为26 dB。在运用200 Ω 电阻时,经过构建简略的电阻分压器,能够轻松完结衰减。因为信号摆幅并不一致,因而,信号峰值应该会到达预期衰减值。

|

(5) |

运用规范的6.98 Ω 和191 Ω 电阻值,成果会发作0.7%的差错。

终究,需求必定的抗混叠处理。在75-MSPS 采样速率下,奈奎斯特速率输出为37.5 MHz,超越了该规划的20 MHz 带宽。将抗混叠极点设为20 MHz,则所需电容为:

|

(6) |

这是一个规范值,因而,完好的输入网络如图7 所示:

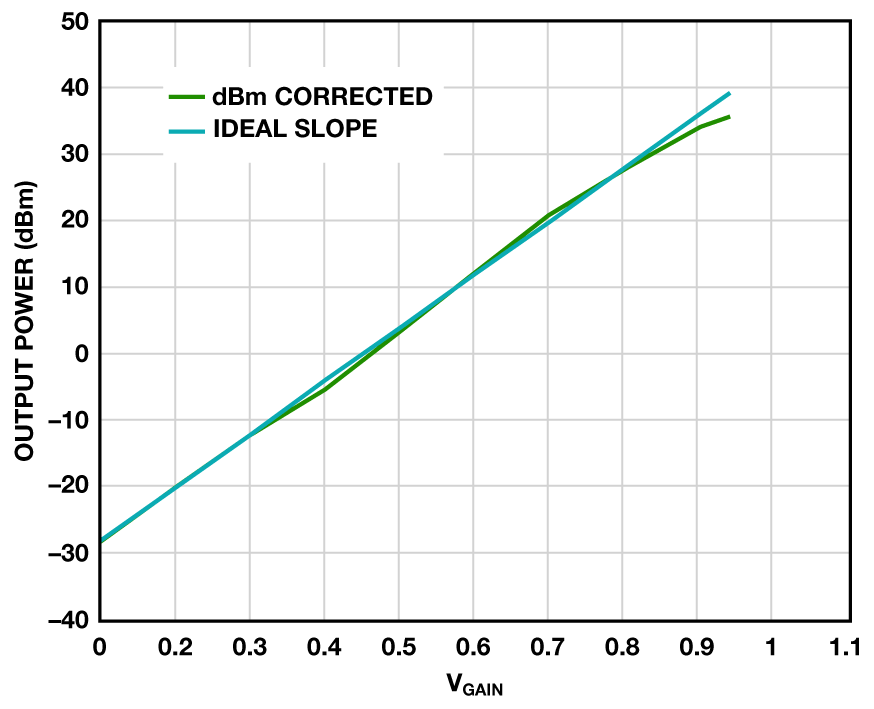

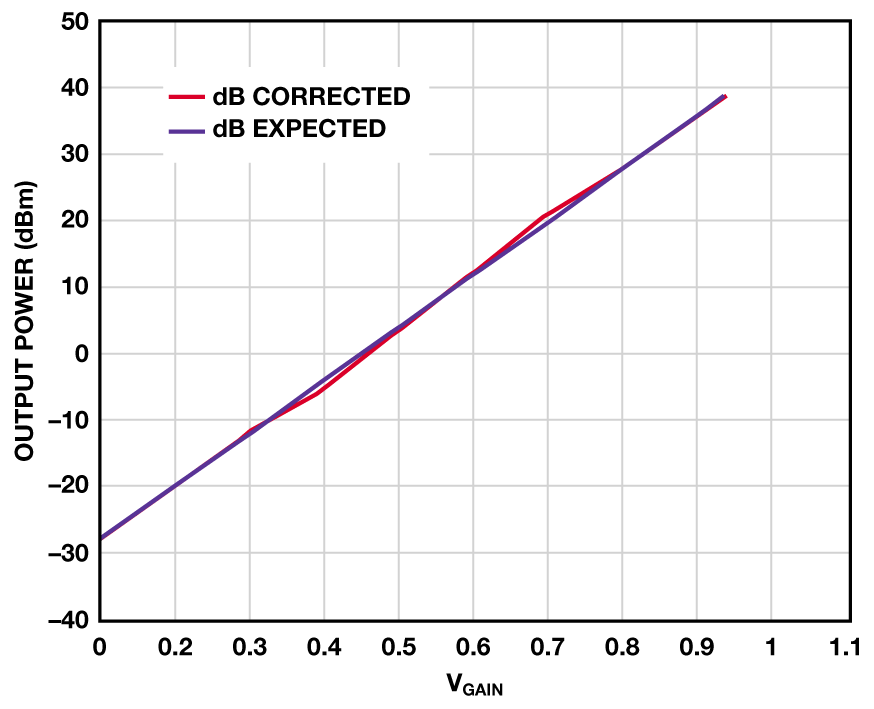

构建该级并进行丈量。全体改变在±0.6 dB 之内,如图8 所示。

ADA4870 输出级

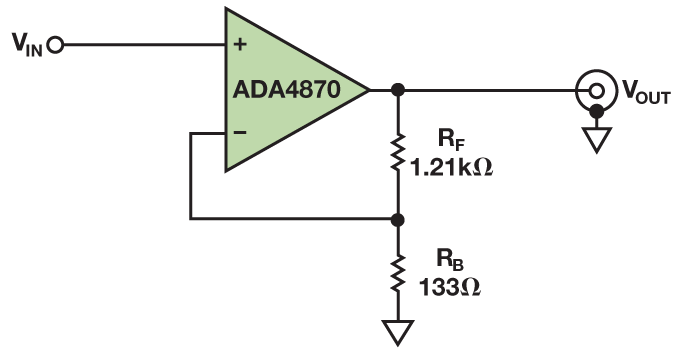

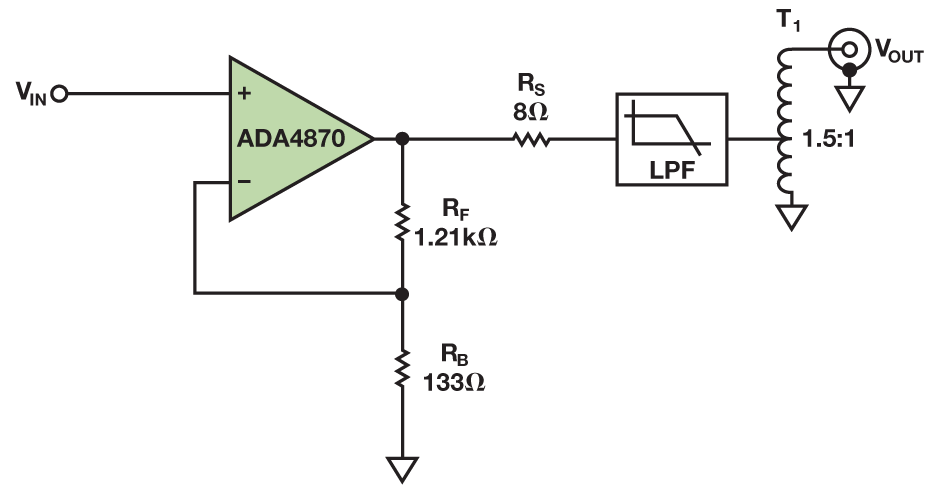

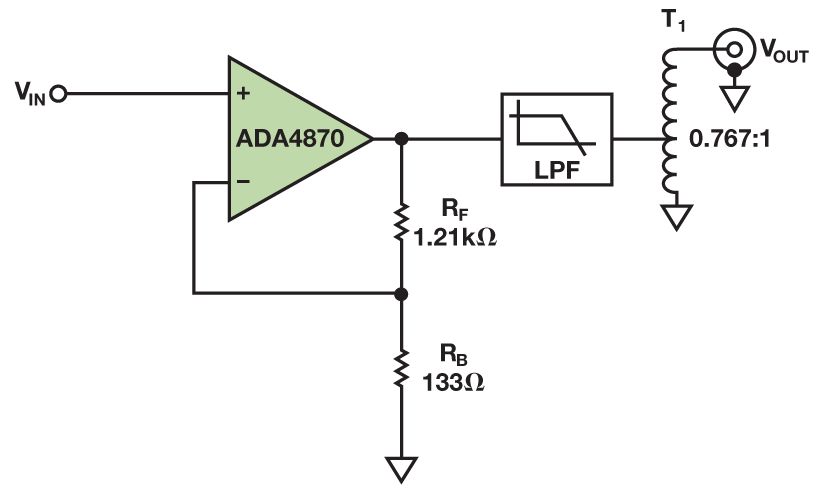

在单端输出由AD8130 供给的情况下,ADA4870 将履行终究10倍增益。设置该增益需求两个电阻,无外部补偿情况下,该级很安稳。未完结的仅有作业是调整输出网络,以满意运用需求。有三种通用完结计划:

- 从扩大器直接输出至50 Ω

- 填充主动变压器输出至50 Ω

- 未填充主动变压器输出至50 Ω

关于直接输出,扩大器输出直接衔接输出衔接器,无需用任何网络来转化源,如图9 所示。这种办法是真直流衔接源的完美挑选,尽管不能发挥出器材的悉数潜力,但依然比典型信号发作器的10 V输出起伏要好得多。在这种情况下,最大峰值功率为5.12 W。

关于焊盘式规划,16 Ω 负载在一个8 Ω 的串联焊盘与经滤波处理的1.5:1 主动变压器之间分配,如图10 所示。在该形式下,因为规划具有低阻抗特性,因而,规划师运用的电感值能够比用于50 Ω规划的电感小6.25 倍。低通滤波器和主动变压器把8 Ω 有用源阻抗转化成匹配杰出的50 Ω 负载。这种规划办法的总峰值输出功率为8 W,最适合需求50 Ω 匹配源的运用,在这类运用中,反射或许成为一个问题,比方,传输线路较长时。

在方针频段内,关于任何反射, 输入阻抗均表现为50 Ω

终究一个选项,也或许是信号发作器最有用的选项,不运用8 Ω焊盘,并且输出功率前进了一倍。咱们依然主张运用LC 阶梯式滤波器,如图11 所示,但阶梯值比用于50 Ω 体系(规划的标称阻抗为16 Ω)的值小3.125 倍。在这种情况下,主动变压器运用的匝数比为0.77:1。该形式下,峰值正弦波输出起伏为28.3 V,ADA4870 将驱动约16 W 至50 Ω 负载(8 W rms 或39 dBm)。

全体处理计划

在实践国际中,假如与实在国际不相符,仿真和等式毫无意义。因而,有必要构建一个完好的体系,根据预期值丈量其功用。图12 所示为一种实践焊盘式输出规划的原理图。

图13 所示为无滤波器条件下的实测成果。体系增益一致性差错为±1 dB,最差条件下输出功率高达2.75 W rms(5.5 W 峰值)(P1dB紧缩点,34 dBm)。值得留意的是,总增益规模超越62 dB,规模比许多规范发作器多16 dB。

增益规模可经过改进DDS 输出端滤波机制以及下降体系噪声的办法前进。图14 所示为选用滤波器时的相同丈量值。滤波输出不存在相同的P1dB 问题,成果将满量程+36 dBm 输出转化成50 Ω负载。总增益线性度更佳(≤0.65 dB),差错仅出现在中心电平周围。

假如详细运转形式需求乃至更高的输出功率,则针对给定运用,能够将多个输出扩大用于驱动专业变压器。或许,能够将这儿描绘的规划办法用于电源较低的体系,但这些办法有必要契合代替规划的约束要求。

留意,受累积输入衰减和增益差错影响,丈量上限止于VGAIN =0.9375 V。经过调整初始衰减网络,充分考虑全体系差错,能够处理这个问题。校正后,全体系增益规模将增至74 dB。

定论

合作高功用VGA 运用高功用、高输出CFA,能够为新一代信号发作器构建出一种简略前端。这些器材的高度集成能够下降PCB电路板的总面积和本钱。

要取得更多功用,能够在闭环反应体系中运用AD8310等对数扩大器。添加对数扩大器后,合作AD9834C 等DDS,规划师能够集成各种形式的包络调制,如频移键控(FSK)、开要害控(OOK)和相移键控(PSK),将其作为一项内涵功用;经过创造性地运用两个根本模块,完结不尽其数的选项。

参阅电路

电流反应扩大器。

对数扩大器/检测器。

Signal Synthesis.

可变增益扩大器(VGA)。

MT-034 攻略,电流反应(CFB)运算扩大器。

MT-057 攻略,高速电流反应运算扩大器。

MT-060 攻略,在电压反应和电流反应运算扩大器之间挑选。

MT-072 攻略,精细可变增益扩大器。

MT-073 攻略,高速可变增益扩大器。