谈谈旁路和去藕电容-原理部分

看了许多关于旁路电容和去藕电容的文章,有代表性的如下:

- 退耦电容的挑选和运用

- 十说电容

- 关于旁路电容和耦合电容

- 关于旁路电容的深度对话

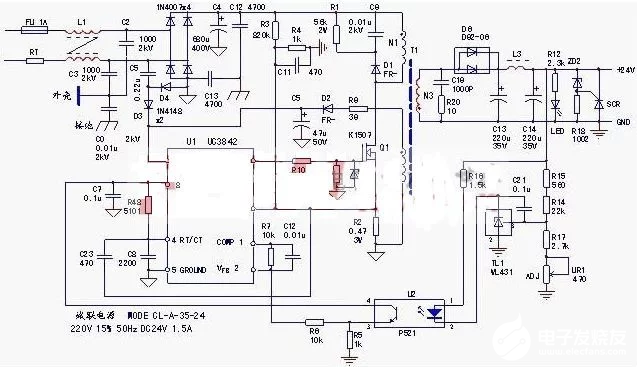

先看看此类电容的运用场合:

依据以上电路来说,由一个电源驱动多个负载,假如没有加任何电容,每个负载的电流动摇会直接影响某段导线上的电压。

瞬间冲击电流的发作原因

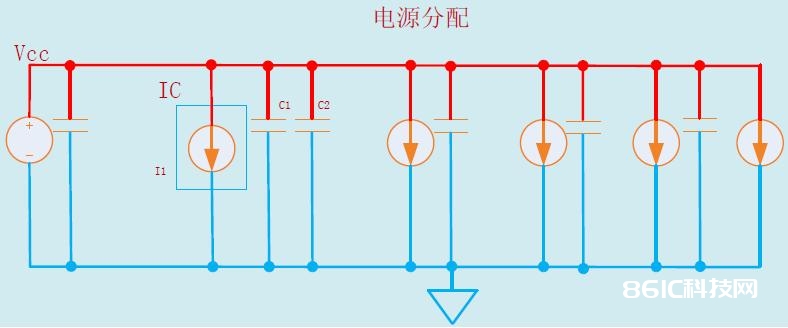

1.容性负载

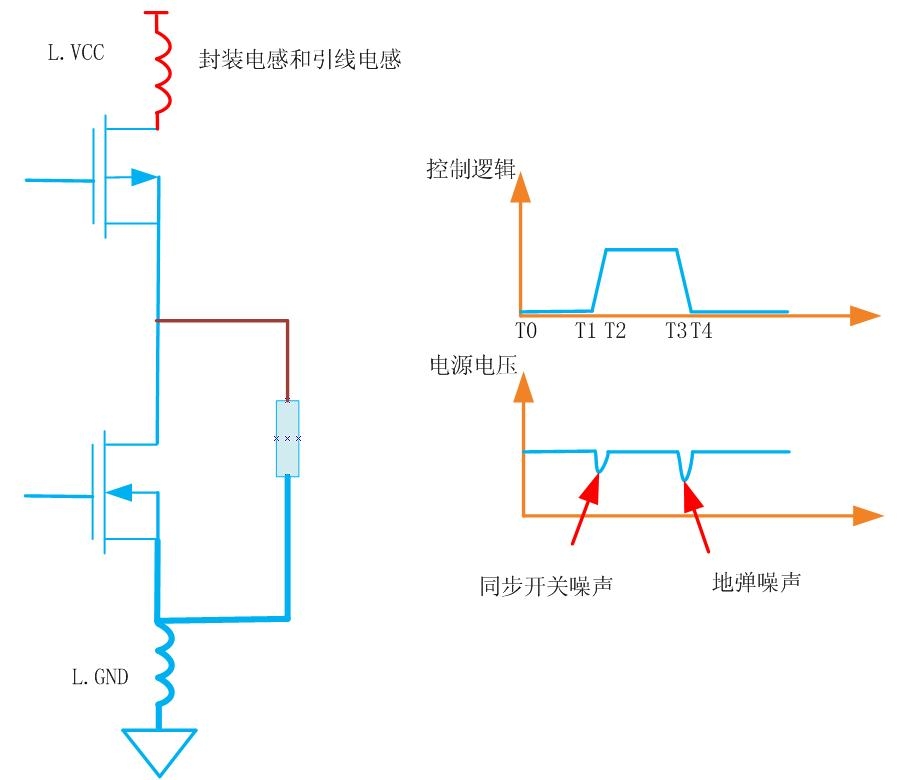

来剖析一下数字电路的电流动摇,数字电路的负载并不是纯阻性的,假如负载电容比较大,数字电路驱动部分要把负载电容充电、放电,才干完结信号的跳变,在信号上升沿比较峻峭的时分,电流比较大,关于数字芯片来说,新派驱动部分电流会从电源线上吸收很大的电流,由于线路存在着的电感,电阻(特别是芯片管脚上的电感,会发作反弹),这种电流相关于正常状况来说实践上便是一种噪声,会影响前级的正常作业,下图反响了作业状况

2.输出级操控正负逻辑输出的管子短时刻一起导通,发作瞬态尖峰电流

PMOS和NMOS一起导通的时分出现的电流尖峰。

电压陷落噪声

咱们考虑数字电路内部结构一般由两个Mos管组成,为了便于剖析,咱们假定初始时刻传输线上各点的电压和电流均为零。现在咱们剖析数字器材某时刻输出从低电平转变为高电平,这时分器材就需要从电源管脚吸收电流(上面一个剖析的是容性负载,现在考虑的是阻性负载)。

从低到高(L=>H)

在时刻点T1,高边的PMOS管导通,电流从PCB板上流入芯片的VCC管脚,流经封装电感L.vcc,经过PMOS管和负载电阻最终经过回来途径。电流在传输线网络上继续一个完好的回来时刻,在时刻点T2完毕。之后整个传输线处于电荷充溢状况,不需要额定流入电流来坚持。

当电流瞬间涌过L.vcc时,将在芯片内部电源和PCB板上发作一个电压被拉低的扰动。该扰动在电源中被称之为同步开关噪声(SSN)或Delta I噪声。

从高到低(L=>H)

在时刻点T3,咱们首要封闭PMOS管(不会导致脉冲噪声,PMOS管一向处于导通状况且没有电流流过的)。一起咱们翻开NMOS管,这时传输线、地平面、L.gnd以及NMOS管构成一回路,有瞬间电流流过开关NMOS管,这样芯片内部至PCB地节点前处发作参阅电平被举高的扰动。该扰动在电源体系中被称之为地弹噪声(Ground Bounce)。

实践电源体系中存在芯片引脚、PCB走线、电源层、底层等任何互连线都存在必定电感值,就整个电源散布体系来说来说,这便是所谓的电源电压陷落噪声。

去藕电容和旁路电容

去藕电容便是起到一个小电池的作用,满意电路中电流的改变,避免相互间的耦合搅扰。关于这个的了解能够参阅电源掉电,Bulk电容的核算,这是与之类似的。

旁路电容实践也是去藕合的,仅仅旁路电容一般是指高频噪声旁路,也便是给高频的开关噪声进步一条低阻抗泄防途径。

所以一般的旁路电容要比去藕电容小许多,依据不同的负载规划状况,去藕电容或许差异很大,当旁路电容一般改变不大。关于有一种说法“旁路是把输入信号中的搅扰作为滤除目标,而去耦是把输出信号的搅扰作为滤除目标,避免搅扰信号回来电源”,我个人不太赞同,由于高频信号搅扰能够从输入耦合也能够从输出耦合,去藕的掉电能够是负载激增的输出信号也能够是输入信号源的骤变,因而我个人觉得怎样区别有点纠结。

电容模型剖析

假如电容是抱负的电容,选用越大的电容当然越好了,由于越大电容越大,瞬时供给电量的才能越强,由此引起的电源轨迹陷落的值越低,电压值越安稳。可是,实践的电容并不是抱负器材,由于资料、封装等方面的影响,具有有电感、电阻等附加特性;尤其是在高频环境中更体现的更像电感的电气特性。

咱们这儿运用的电容一般是指多层陶瓷电容器(MLCC),其最大的特色仍是由于运用多层介质叠加的结构,高频时电感十分低,具有十分低的等效串联电阻,因而能够运用在高频和甚高频电路滤波无对手。

关于其特性剖析和分类能够参阅曾经的文章:

Surface Mounted Capacitor(表贴电容) Ps:大部分是英文的,我有空把它翻译收拾过来。

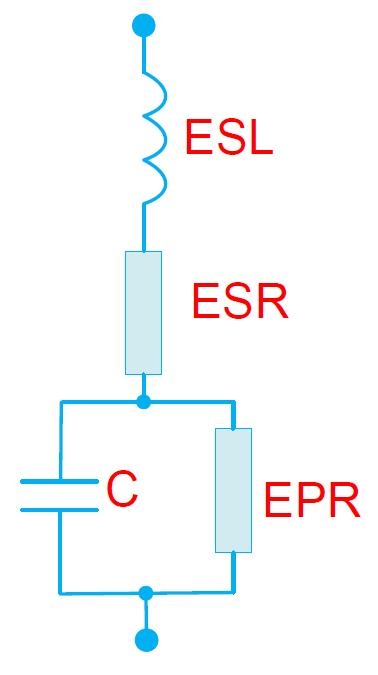

电容模型为

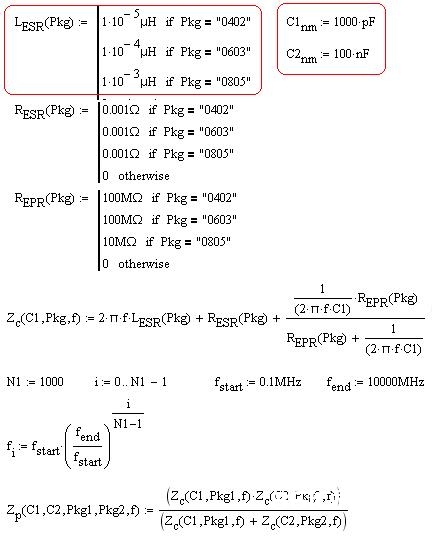

等效串联电阻ESR:由电容器的引脚电阻与电容器两个极板的等效电阻相串联构成的。当有大的沟通电流经过电容器,ESR使电容器耗费能量(然后发作损耗),由此电容中常用用损耗因子表明该参数。

等效串联电感ESL:由电容器的引脚电感与电容器两个极板的等效电感串联构成的。

等效并联电阻EPR:电容器走漏电阻,在沟通耦合运用、存储运用(例如模仿积分器和采样坚持器)以及当电容器用于高阻抗电路时,Rp是一项重要参数,抱负电容器中的电荷应该只随外部电流改变。可是实践电容器中的EPR使电荷以RC时刻常数决议的速度缓慢泄放。

经过上述参数,咱们能够知道得到电容阻抗曲线

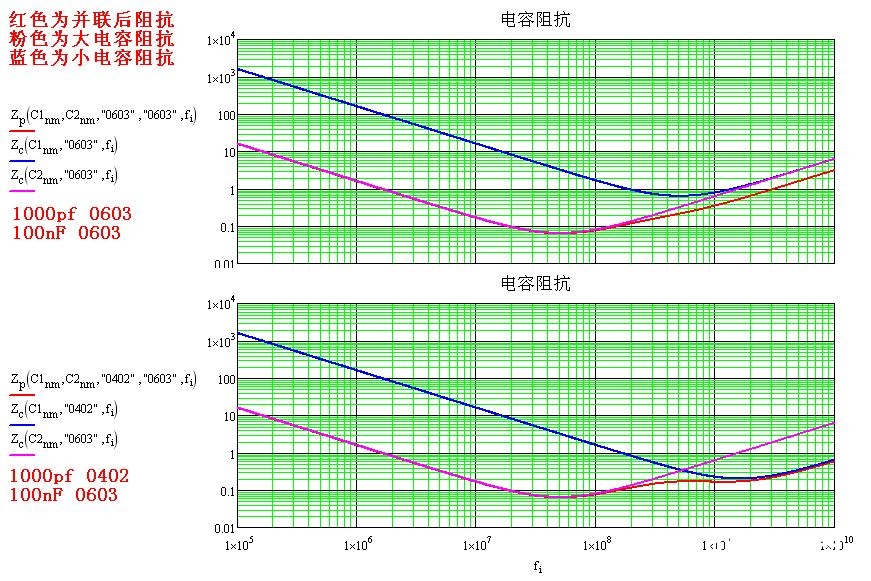

我找了Murata的电容做了比照

1000pF 0402

100nF 0603

实践电容的阻抗是如图所示的网络的阻抗特性,在频率较低的时分,出现电容特性,即阻抗随频率的添加而下降,在某一点发作谐振,在这点电容的阻抗等于等效串联电阻ESR。在谐振点以上,由于ESL的作用,电容阻抗跟着频率的升高而添加,这是电容出现电感的阻抗特性。在谐振点以上,由于电容的阻抗添加,因而对高频噪声的旁路作用削弱,乃至消失。电容的谐振频率由ESL和C一起决议,电容值或电感值越大,则谐振频率越低,也便是电容的高频滤波作用越差。

ESL首要和电容的封装直接相关的,封装越大,ESL也越大。因而咱们并联三个电容以上关于滤除噪声来说并不是很显着的。这儿有个问题,咱们乃至期望能够得到0402的0.1uF的电容,可是这个是比较可贵,由于封装越小,操作电压和容值都是有约束的,所以沉着的做法便是用两个电容。

经过曲线咱们发现,假如咱们仅仅考虑1MHz以内的噪声的时分,在大多数状况下,旁路电容的规矩能够简化为只用0.1 μF电容旁路每一个芯片。不过咱们要挑选0603的MLCC的电容,并且要注意电路布局。假如咱们沿着电路板上的电流道路,能够发现电路板铜线上存在电感。在任何电流途径上的电感与该途径的闭环面积呈正比。因而,当你环绕一个区域对元器材进行布局时,你需要把元器材紧凑地布局(为了使电感为最低)。