PCI Express 构架

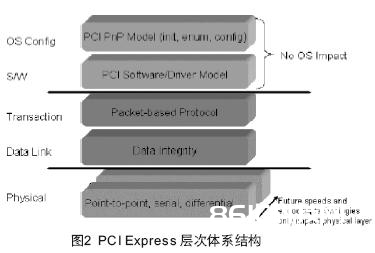

如图 2 所示,即 PCI Express |0″>PCI Express 的层次体系结构。它坚持了与 PCI 寻址形式(加载-存储体系结构且具有单层地址空间)的兼容性,然后确保了一切现有的应用程序和驱动操作无需改动。PCI Express 装备运用的是PCI 即插即用规范中所界说的规范机制。软件层宣布读和写恳求,并运用根据数据包、分段传输的协议经过处理层传输至I/O 设备。

链路层向这些数据包增加序列号和循环冗余校验(CRC )然后创立了一个高度牢靠的数据传输机制。根本的物理层包含两个单工通道,即传输对和接纳对。这个传输对和接纳对一同被称为一个信道。2.5 Gb/s 的初始速度供给了在每个PCI Express 信道上每个方向上大约250 MB/s 规范带宽。一旦考虑协议头,这其间大约200 MB/s 由设备用来传输数据。这一速率是大多数典型 PCI 设备的 2 番到 4 番。而且不同于 PCI 的是,只需总线带宽在设备之间同享,每一个设备都 具有此带宽。

|

物理层

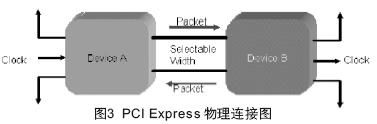

根本的PCI Express 链路包含两个低电压的AC 耦合差分信号对(一个传输对和一个接纳对),如图3所示。物理链路层信号运用一个去加剧(de-emphasis )战略来削减符号间搅扰,然后进步了数据完整性。数据时钟经过运用 8b/10b 的解码战略来嵌入,然后抵达极高的数据传输率。初始的信号产生频率是每个方向 2.5 Gb/s (生成1个信号) 而且它将会跟着硅工艺的进步而增加至每个方向10 Gb/s(信号在铜线中传输或许完成的最大速率)。两个链路层的 PCI Express 署理在物理层上传输数据包。

|

图3 PCI Express 物理衔接图一个PCI Express 链路层的带宽或许经过增加信号对构成多个信道而线性增加。物理层供给 x1, x2, x4, x8, x12, x16 和x32 信道宽度,理论上它将输入的数据包在这些信道上分配。运用 8b/10b 编码方法,每一个字节在这些信道上传输。数据的分拆和整合关于其他层来说是通明的。在初始化阶段,每个PCI Express 链路经过链路两头署理的信道宽度的匹配和频率操作来树立。在这其间没有固件和操作体系软件的参加。PCI Express 体系结构供给了将来经过速度晋级和高档编码技能所带来的功能提高。将来的速度、编码技能或许前言只是会影响物理层。

在PCI Express 中运用不同的信道宽度需求用户留意扩展板要求的带宽以及与母板供给的带宽相匹配。除了图形卡以外(一般是X16 ),许多前期的PCI Express 扩展板运用的 X1 的宽度。跟着更高的带宽要求,越来越多的板卡将运用更宽的带宽。前期的PCI Express 计算机供给一个X16 的衔接器以及一些X1 、X4 、X8 插槽的组合,这由计算机面向的客户所决议。PCI Express 答应在不匹配的信道宽度上进行一些交互操作,这取决于不匹配的方向。在一个较小宽度的衔接器上运用更大宽度的扩展板卡是向下刺进。例如,运用PCI ,您能够在一个32 位的插槽上刺进一个64 位的PCI 板卡。

可是,在 PCI Express 中,向下刺进在物理上被扩展板卡和衔接器所阻挠。另一中不匹配在一个较大的衔接器上运用一个较小的扩展板卡是向上刺进。向上刺进是答应的,可是会受到约束在这种装备下,母板厂商需求支撑仅在X1 数据率上的扩展板卡,然后糟蹋了在具有更快接口速率的扩展板卡上的出资。不管一个特定的母板在向上刺进装备时能否在全速率时处理一个扩展板卡,都必须在每种情况下向母板生产商承认。例如,一些母板能够在一个X4 的扩展板卡刺进一个X8 或X1 的插槽时,以全速率(X4 )进行处理,可是来自同一厂商的其他母板或许仅以X1 的速率运转。在一个母板既带有集成图形操控器(板载)又带有一个 X16 的 PCI Express 插槽以用于将来图形扩展的情况下,一般不或许在板载图形卡使能的一起运用那个 X16 的插槽。

数据链路层

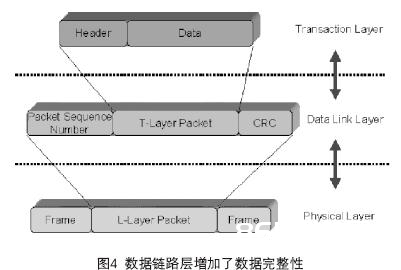

链路层的首要效果便是确保数据包在 PCI Express 链路上的牢靠传输。链路层担任数据完整性并向处理层的数据包增加序列号和循环冗余校验,如图4所示。大部分数据包在处理层初始化。一个根据优先数的、流量操控的协议确保了数据包仅在另一端具有接纳这个数据包的缓冲区情况下才干传输,这样就去除了任何数据包的恳求以及由于资源约束而引起的总线带宽糟蹋。链路层会主动的从头收发一个被标记为损坏的数据包。

|

处理层

处理层接纳软件层的读和写恳求,并创立恳求数据包发送至链路层。一切的恳求都被分段的处理而且一些恳求包需求一个呼应包。处理层也从链路层接纳呼应数据包而且将它与原先的软件恳求相匹配。每一个数据包都具有一个仅有的标识,使得呼应包能够指向正确的源。数据包的格局供给了32 位的存储地址和扩展的64 位地址。数据包也具有比如“无侦听”、“灵敏排序”“优先级”等特点,这或许用于将这些数据包在I/O 子体系中以最优的途径传输。

处理层供给4 个地址空间3 个PCI 地址空间(内存、I/O 和装备)和音讯空间。PCI 2.2 引入了另一种播送体系中止的方法称为音讯信号中止(MSI )。作为PCI 2.2 体系中一种可选的功能, 这儿运用了一种特别格局的内存写处理代替硬衔接的边带信号。PCI Express 技能指标从头运用了MSI 概念以作为一种首要的中止处理方法,而且运用了音讯空间来接纳一切的优先的边带信号来作为带内信号,例如中止、电源办理恳求,和复位。其它PCI 2.2 技能指标中的“特别周期”,例如中止承认,也被处理成带内音讯。您能够将 PCI Express 音讯视为“虚拟的线”,由于他们的效果是消除当时平台上所运用的各种边带信号。

软件层

软件兼容性关于 PCI Express 是极为重要的。软件兼容性有两个方面初始化(或许罗列)和运转时间。PCI 具有一个功能强大的初始化形式,其间操作体系能够发现一切当时增加的硬件设备然后分配体系资源,例如内存、I/O 空间和中止,然后创立一个优化的体系环境。PCI 装备空间和I/O 设备可编程才能是PCI Express 体系结构中坚持不变的重要概念。PCI 所运用的运转时间软件形式是一个加载-存储、同享内存的形式,它在PCI Express 体系结构中得以坚持以使得一切现有的软件能够无需改动即可履行。新的软件也能够运用一些PCI Express 最新的先进特性,例如高档开关(本文并未述及)。