1、体系简介

通用串行总线(USB)支撑热插拨,真实的即插即用。USB1.1在全速传输时能够到达12Mbps的传输速率;低速传输时传输速率可达1.5Mbps。USB电缆线只要4根,两根是电源线,传送5V电源,可用来向设备供电;别的两根是信号线,用来传输串行数据。与传统的RS-232串口比较,USB具有传输速度更快、集成化程度更高、编程化更好以及能够支撑多个设备等长处。因而在咱们的规划中用它来和主机接口完结高速的数据通讯。

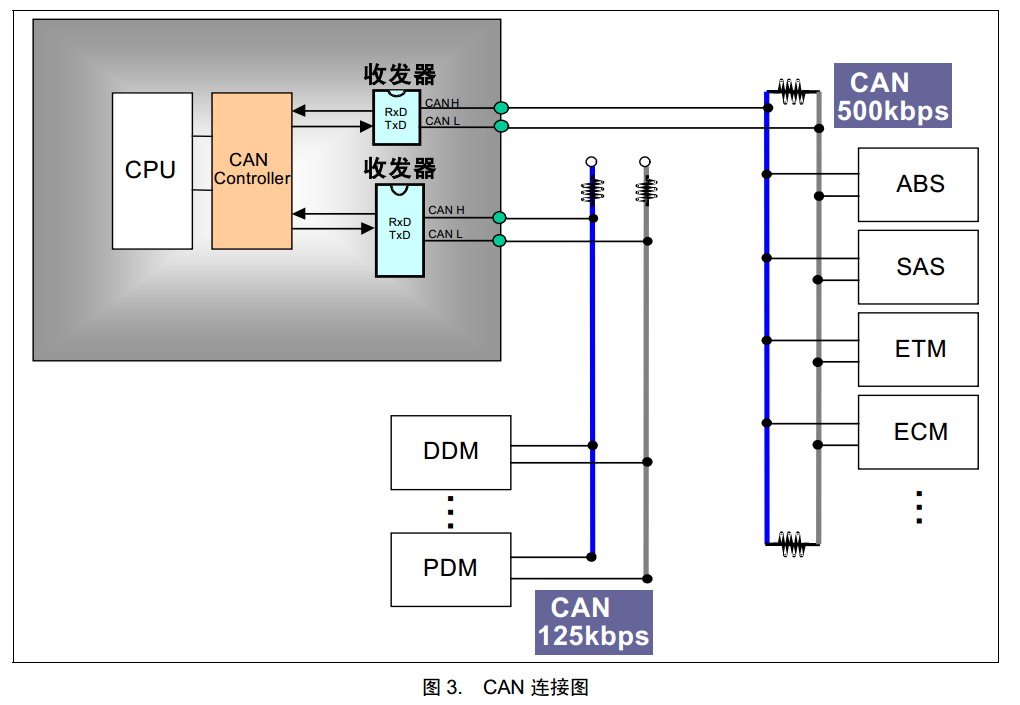

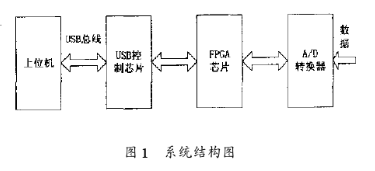

在数据收集体系中,一般选用单片机或DSP(数字信号处理器)作为CPU,操控ADC(模/数转化器)、存储器和其他外围电路的作业。可是单片机的时钟频率较低,难以习惯高速数据收集体系的要求,而DSP尽管能够完结较高速的数据收集,但其速度进步的一起也进步了体系的本钱。FPGA(现场可编程门阵列)有单片机和DSP无法比拟的优势:时钟频率高,内部时延小;悉数操控逻辑由硬件完结,速度快,效率高;组成办法灵敏,能够集成外围操控、译码和接口电路。因而,在本体系中咱们用FPGA来操控A/D和USB芯片的运转。体系结构图如图1所示。

图中FPGA选用ALTERA公司出产的APEX 1k系列芯片,型号为EP1K30,经过在EPGA中编写硬件逻辑操控A/D转化器的运转;完结A/D转化器和USB 操控芯片间数据传输的数据总线接口。除此之外,为了确保EPGA和USB操控芯片间数据交互进程的完结,有必要在FPGA中供给一个用于传输通讯两边操控和状况信息的GPIO接口。

2、 A/D转化环节

在该体系中咱们选用TI公司的ADS7800。它是12位并行模数转化器[2》,接口简略,很简单操控,最大采样率可达333kHz,输入的电压规模为-10V~+10V或-5V~+5V。ADS7800芯片的数字接口比较简略,能够很便利地与其它数字体系相衔接。对此芯片地操控有彻底操控形式(full control mode )和孤立操控磨蚀(stand-alone control mode )两种操控办法。

在本体系中,对ADS7800芯片的操控是经过在FPGA芯片中编写操控逻辑来完结的。咱们选用了孤立操控形式,在此操控形式下,输出数字信号是12位并行的。

运用FPGA芯片的可编程性能够运用芯片中的12个IO脚作为数据总线,另运用一些IO脚作为ADS7800的操控信号输入,操控模/数变换器以32kHz的速率对模仿输入信号进行采样,采样的数据存入FPGA的RAM中。本体系中所运用的FPGA芯片型号为EP1K30QC208-3,它具有着杰出的特性,芯片内部共有3万个逻辑门,容量相当大;6个嵌入式阵列块,可是现最大为3k字节的RAM存储器。

3、 体系的规划与完结

3.1 USB接口芯片介绍

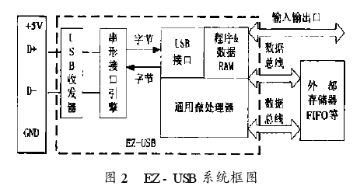

在规划中,咱们选取Cyprees公司的EZ-USB系列芯片来完结USB接口设备方的操控。它是一款带有多个外设、高度集成的芯片,其功用框图如图2所示。一个集成的USB收发器(transceiver)衔接USB总线的D+和D-。串行接口引擎(SIE)对总线上的数据进行编/解码、过错检测、位填充以及USB标准规则的其它信号级操作的完结,而且终究把数据收或发到USB接口部分。

内部的微处理器是8051单片机的增强型,进步了履行速度并添加了一些新的特性。它运用内部RAM作为程序和数据存储器;带有16位地址线和8位数据线用来拜访外部存储器,特有的快速传输形式能够在外部逻辑和内部USB FIFO间快速地传递数据。

3.2 USB总线数据通讯解决计划

在完结数据通讯解决计划时,为完结数据流地正常传输,所树立的硬件渠道有必要能够供给两个接口。首要有必要要有一个完结数据传输的数据总线接口;除此之外,为了确保数据交互进程的正常完结,有必要供给一个用于传输通讯两边操控和状况信息的GPIO接口。

AN2135SC芯片供给了EZ-USB系列芯片的一切接口和功用。在本体系中,咱们将运用这款芯片和FPGA芯片合作作业,树立一个依据USB总线接口的数据通讯解决计划,以完结将采样信号输出到上位机中的功用。

在此解决计划中,咱们挑选AN2135SC芯片作业在快速数据传输形式下的8位并行数据总线D[7…0》作为数据传输的总线接口;挑选AN2135SC芯片中的通用 C总线主操控器接口作为数据通讯进程中进行操控和状况信息传输的GPIO接口。这样,芯片中的一般GPIO引脚就能够用来完结其它功用,便利了体系的进一步扩大。图3所示为AN2135SC芯片与FPGA芯片的接口示意图。

为了使AN2135SC芯片中快速数据传输形式下的数据总线D[7…0》和通用 主操控器别离完结流数据传输和操控状况信息传输的功用,需求在芯片的8051核中编写程序,对AN2135SC芯片内部相关的专用寄存器进行装备[3》。

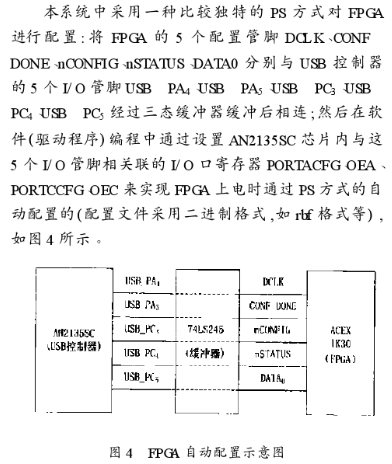

3.3 FPGA的共同装备计划

FPGA芯片是一种依据SRAM工艺制造的可编程器件,其编程数据存储于器材的SRAM存储器内。这是一种易失性的存储器,在体系掉电时,FPGA芯片中的逻辑将会丢掉,芯片功用随即消失,上电后需求从头对其进行装备。运用此功用能够灵敏地改动FPGA芯片中的逻辑结构。这是一种动态装备进程,这种办法称为ICR办法(in circuit reconfigurable)。

本体系中对FPGA的装备选用PS(passive serial,即被迫串行)办法。一般选用的是以下两种装备办法:装备数据来自于ALTERA公司出产的串行制造器材或体系操控器,如 等,体系上电时可对ACEX1K系列芯片进行装备;装备逻辑也能够经过ALTERA公司出产的Master Blaster、Byte Blaster MV或Bitblaster下载电缆进行手艺下载。可是前者会添加体系的本钱,而后者又很不便利。

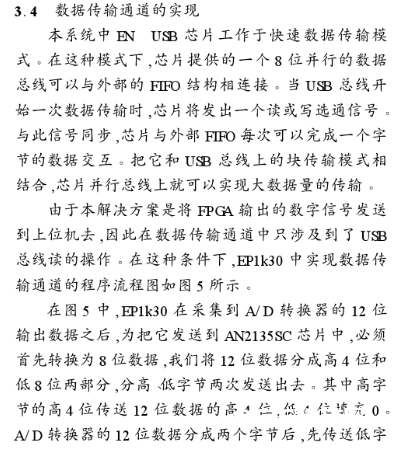

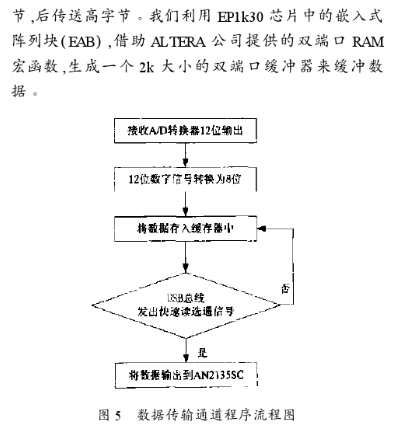

上面的程序给出了这一次读进程中读地址指针的改变状况。跟着读地址指针的改变,缓冲器中的数据依次输出到数据总线D[7…0》上去。程序中 …0》为缓冲器的读地址指针, …0》是缓冲器的输出端口, … 是 芯片的数据总线 … 。

3.5 功用的完结

在 芯片与 芯片进行数据传输的一起,两边需求一些握手信号来和谐传输进程。为此,咱们挑选了 芯片中的 总线主操控器作为 端口,用来传输一些必要的操控和状况信息。

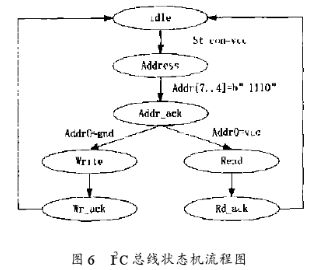

为了与 芯片中的 总线主操控器合作作业,咱们在 芯片中编写了一个 总线从模块,使得 总线上的数据传输能够顺畅进行。依据 总线传输标准,咱们设定了一个状况机 ,它共有如下7个状况: 。图6给出了此状况机的状况图。

由图6能够看出,在开端条件( 发生后, 由闲暇( 状况进入地址状况( 。咱们在 中指定了两个寄存器用于存储从 总线上发送来的操控信号和即将发送到 总线上的状况信号,它们别离是操控寄存器 ‥0 和状况寄存器 ‥0 ,这两个寄存器地址的高4位均为“1110“。相同,咱们能够把1 芯片中一切由 总线寻址的寄存器的高4位地址都设定为“1110”。如图6所示, 总线在地址期内发送的高位地址只要为“1110”时,1 才会发生呼应。这样做的优点是便于扩大其它 总线设备。

总线在地址期内发送的最低地址用于指定随后的数据传输是首要设备读仍是主设备写,高电平表明主设备读,低电平表明主设备写。读写状况转化如图6所示。因而,8位地址中能够用作寻址 端口的地址位为 ‥ 。

4、 结束语

本文介绍了数据通讯解决计划中数据传输通道和 功用的完结。试验证明,两个模块合作作业即可完结数据的正常传输,然后顺畅地将 转化器的输出信号经 总线传送到上位机去。这个解决计划依据 总线规划而且结合 来进行操控,充分运用了 总线数据传输速率高、 设备可热插拨等功用和 速度快、效率高、装备灵敏的特色。经实践证明,它是一个功用齐备、高效安稳的解决计划。

责任编辑:gt