1、概述

AD5532是美国ADI公司推出的一款32通道、14位串行输入、电压输出型单片集成数模转化器。它还内置一个额定的A/D转化器,能将外部电压采样数据传递至相应D/A单元,能够完结精度高达±0.018%的无限采样坚持功用。AD5532具有串行输人、多通道模仿输出等特性,适用于对功用、功耗要求高,模仿通道需求多的测控体系。

2、内部结构及引脚功用

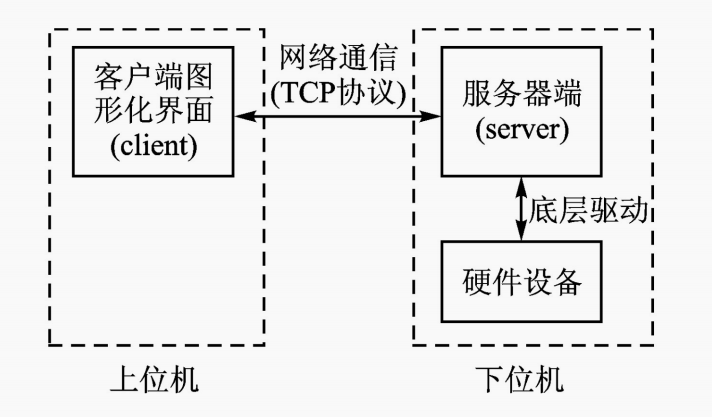

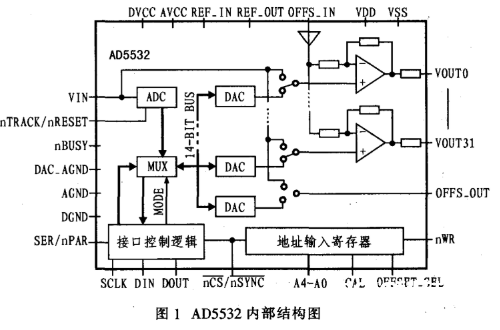

图1所示为AD5532的内部结构框图,AD5532片内集成1个A/D转化单元(专为ISHA形式设置)和32个D/A转化单元,每个D/A转化单元均配有一个输出缓冲器。此外,片上还有串行、并行逻辑电路易于外部操控器相连。在D/A转化形式下,需求经过串行输入方法将14 bit的数据传送到32个D/A转化寄存器中的某一个,随后,该数据将转化为模仿输出VOUT0~VOUT31(带有增益和偏移)。

AD5532的引脚功用描绘如下:

AVCC:模仿供电电压,规模为4.75 V~5.25 V,只向D/A转化器内核供电;

VDD:正电源端,规模为8 V~16.5 V;

VSS:负电源端,电压规模-4.75 V~-16.5 V;

DGND:数字地,数字电路的参阅点;

DVCC:数字电源端数字信号供电电压,规模为2.7 V~5.25 V;

DAC_GND:一切D/A转化模块的参阅地;

REF_IN:VOUT0~VOUT31的参阅输入电压;

REF_OUT:内部参阅输出电压,供给3 V电压;

VOUT:32个通道的输出;

VIN:无限采样/坚持模仿输入电压,在D/A转化形式时,该引脚接地;

A4~A0:并行形式下端口地址,5个地址引脚选定32个通道。A4是通道地址的MSB,A0是通道地址的LSB。每个引脚均有内部上拉电阻,因而,这些引脚悬空时,默以为逻辑高电平;

CAL:并行形式下操控32个D/A转化单元同步向VIN采样,接内部下拉电阻,因而,该引脚悬空时,默以为逻辑低电平;

nCS/nSYNC:低电平时,在并行形式下,片选使能;在串行形式下为帧同步;

nWR:在并行形式下有用,写信号,低电平有用,合作nCS/nSYNC引脚可经过并口确认地址,内部下拉电阻,悬空时默以为逻辑低电平;

OFFSET_SEL:并行形式下有用,偏移挑选,高电平有用,用于挑选偏移通道,内部下拉电阻,悬空时默以为逻辑低电平;

SCLK:串行形式下的串行时钟输入,作业频率为14 MHz,20 MHz时作业在ISHA形式。

DIN:串行形式下的串行数字输入,在SCLK下降沿数据有用,内部上拉电阻,悬空时默以为逻辑高;

DOUT:串行形式下的串行数字输出,在SCLK上升沿数据输出;

SER/nPAR:答使用户挑选串行接口或并行接口形式,当拉为低电平时,挑选并行接口形式,当拉为高电平时,挑选串行接口形式。内部下拉电阻悬空时默以为逻辑低;

OFFS_IN:偏移输入,改动其输入电压调理VOUT的输出规模;

OFFS_OUT:偏移输出,衔接至OFFS_IN可调理VOUT的输出规模;

BUSY:使能采样输入电压,该引脚下降时,采样输入信号,上升时,采样完结;

nTRACK/nRESET:该引脚坚持高电平时,一旦通道被选中,采样VIN;该引脚坚持低电平时,直接切换至GAIN/OFFSET环节输入至VIN,选定通道在nTRACK的上升沿采样VIN。该引脚也可用于将器材复位至上电复位阶段。内部上拉电阻,悬空时默以为逻辑高电平。

3、作业原理

AD5532供给串并行两种操控方法,数字/模仿转化、无限采样/坚持、回读以及采样回读四种作业形式,其间并行操控方法只在无限采样/坚持形式下起效果。

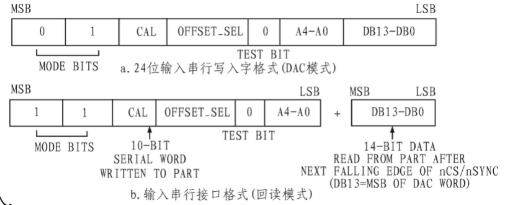

图2的a、b分别是DAC形式和回读形式下的数据传输格局。这两种形式下的数据传输格局根本相同,仅仅MODE BIT不同。图b中DIN引脚上的数据在输入A0位后主动疏忽,DOUT在第2个nCS/nSYNC下降沿后输出相应DAC寄存器中DB13~DB0位。

串行数据传输格局的前2位为作业形式位。CAL位在DAC作业形式下是测验位,为‘1’时32个DAC寄存器一起置‘1’或‘0’。OFFSET_SEL位为‘1’时表明选用OFFSET通道,A4~A0位疏忽。A4~A0位为地址位,这5位数据确认相应的DAC,A4为MSB,A0为LSB。DB13~DB0位中的数据,写入由A4~A0确认的DAC寄存器,其间,DB13为MSB,DB0为LSB。

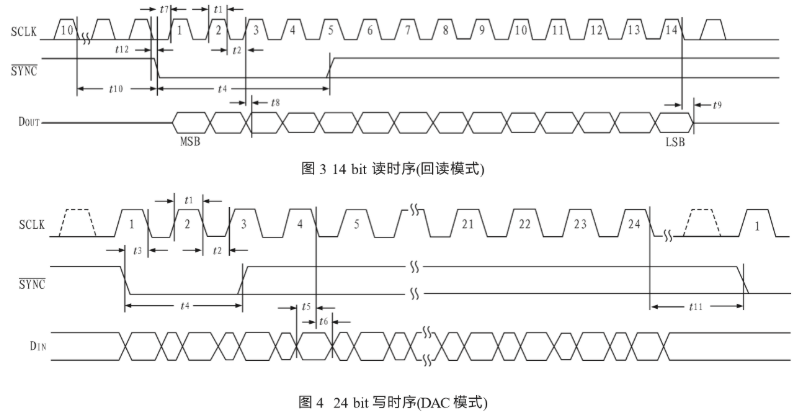

图3和图4所示分别为AD5532的串行读、写时序。在接连或非接连串行时钟下。在nCS/nSYNC的第一个下降沿复位计数串行时钟计数器,保证相应位移入或移出串行寄存器。一旦在所选的作业形式下移人或移出数据位后,SCLK信号被疏忽。下一次串行数据传输时首要使用nCS/nSYNC的下降沿复位计数器。

回读形式下,nCS/nSYNC的下降沿后第一个SCLK的上升沿时DOUT离开高阻状况并在其上升沿输出数据,一旦抵达SCLK的第14个下降沿DOUT回来高阻状况。DIN上的数据在nCS/nSYNC下降沿后的第一个SCLK的下降沿被锁存并在后续的SCLK下降沿接连锁存。串行接口仅在SYNC的下降沿时输入/输出数据。

4、 典型使用

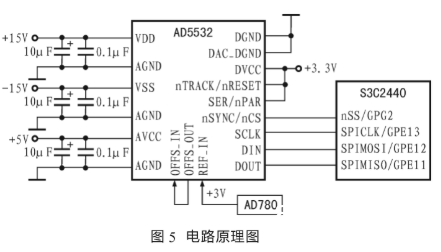

图5所示为AD5532在DAC作业形式下的典型使用原理图。其间VDD供给+15 V电压,VSS供给-15 V电压,AVCC供给+5 V电压,与三星公司S3C2440相连,DVCC供给+3.3 V电压。因为本体系仅需DAC功用,所以将SER/nPAR及nTRACK/nRESET引脚电压拉高,串行输入/输出引脚与S3C2440的相应SPI引脚相连。其他未触及引脚如果是输入端最好接地或拉高。

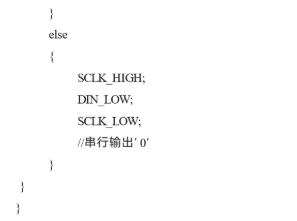

S3C2440选用两种方法完结与AD5532的串口通讯:一是选用串行外围设备接口(SPI接口);二是经过直接编程操控相应I/O引脚完结通讯功用(软件SPI方法)。前者SPI模块在一系列寄存器设置后,由硬件主动完结数据的移入和移出完结串行通讯;后者是经过软件操控I/O端口,逐位将数据由端口发送或接纳。因为AD5532串行接口在D/A输出时接纳24位数据,而回读时只需10位数据,不符合S3C2440的SPI接口传输时8位数据对齐要求。故本体系选用软件SPI方法,依据D/A输出形式与回读形式下数据传输格局编写相关函数。

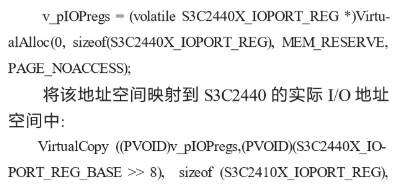

体系选用Windows CE.NET4.2操作体系,程序运转空间分红内核态与用户态,且一切地址均为虚拟地址。因为使用程序无法拜访I/O引脚的操控与数据寄存器,所以编写函数前需先依照WindowsCE.NET驱动程序方法编写:先请求某一内存地址空间,然后将该地址空间映射到I/O引脚的寄存器,最终对该地址相应位进行读写操作,模仿AD5532所需的串行传输方法操控器材。请求地址空间:

完结了上述过程,可经过读写v_pIOPregs实践操控相应引脚。

SPICLK/GPE13,SPIMOSI/GPE12,SPIMISO/GPE11引脚输人/输出状况设置:

以上函数中channel取0~31,被移位到低14位时,表明挑选的通道;value取低14位,表明输出的详细值。

将以上代码加入到使用程序源代码中,就可依据需求调用函数拜访AD5532进行D/A输出。当然,在编译前,还需求找到pkfunc.h,ceddk.h,Winbase.h文件,并将其放置在源代码目录下,并请求内存空间及映射内存空间代码文件头include进去,不然使用程序最终无法编译,提示找不到相应函数。

5、 结束语

选用AD5532串行形式进行D/A转化具有速度快、精度高、功耗低、占用口线少的长处,十分适用于需求多通道,宽规模模仿信号输出的场合。该体系电路已在试验中调试经过。

责任编辑:gt