微操控器现在有一个惊人的数字,能够一起运用来卸载初级其他功用从CPU片上外设。这能够大大进步加工功率,下降功耗,并简化规划。你或许会在一个不幸的意外,不过,假如你的外设功用压倒内部总线接口和数据传输缓慢的大幅进步。走运的是,微操控器制造商现已添加了新的,高效的总线接口,常与要害外设和片上存储器,能够协助支撑多种数据传输之间的多条途径。这些新的公交车的确有局限性,可是,由于衔接全部,全部是在芯片面积和功耗方面过于贵重。了解常见的运用形式,这些新的片上总线将协助您创立,最大极限地进步数据传输带宽,高效的规划。本文将快速回忆一下一些常见的智能片上总线的功用并举例阐明例如规划,充分利用这些要害功用。一些触及的主题将包含:片上总线矩阵架构,选用DMA操控器,专用外设数据传输功用,智能缓存,公交优先体系,并中止操控。

通用总线接口架构

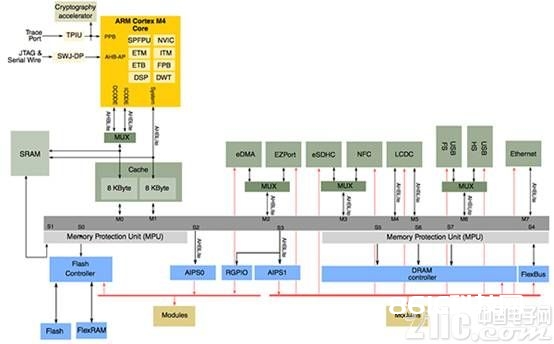

几个要害的架构办法出现在简直一切的高功用总线互连结构。这并不古怪,由于在要害战略支撑高带宽是能够树立可独立运转多个并行衔接。总线矩阵架构,几个总线操控器能够独立拜访多个公交车奴,也许是最常见的构建块的高功率总线架构。飞思卡尔的Kinetis K70 MCU是需求有用的数据处理和移动互连架构类型的一个很好的比如。如图1所示,飞思卡尔的Kinetis K70 MCU运用多级总线矩阵,可八个独自的总线主控器和八个独立总线从设备之间相互衔接。这是或许的多个主机和从独立运作。内存分配是非常重要的效益最大化。例如,以下操作或许一切操作在没有堆叠平行:

•中心 – 在Flash中的阐明和中心只要数据和仓库的SRAM_L

•USB – 在SRAM_U数据缓冲区

•LCD操控器 – 图形缓冲区DDR

图1:飞思卡尔的Kinetis K70 MCU总线互连架构。 (飞思卡尔供给)飞思卡尔还供给了一个模块化开发渠道,为K70,它的飞思卡尔Tower System的一部分,使经过可重构硬件快速原型和东西再利用。该TWR-K70F120M可与宽广的挑选塔式体系的外设模块,包含新的TWR-LCD-RGB它从K70 MCU图形LCD操控器承受RGB数据。当两个或多个主机企图拜访一个从端口,接口将运用裁定算法,以确认哪些主机将首要拜访端口。两种常见的裁定计划,能够常常用于总线拜访是固定的优先级或循环。在一个固定的优先级计划中的主优先级是固定的,经过优先级较低的主人给予高优先级的主站的拜访权限。假如有几个主站以持平的优先权,以循环优先级计划能够被运用。在这个计划中的主人旋转优先为,跟着时刻的推移,有相等时机取得资源。告诉的DMA拜访总线矩阵的重要性。通常情况下,DMA传输是最节能的所以对DMA具有高效的主机拜访总线矩阵是至关重要的。一些资源将有多个衔接到总线矩阵 – 留意例如DRAM操控器 – 由于它们是多个主要害资源。这经过消除“拜访堵塞”当多个主需求拜访相同的资源,或许会产生,进步了全体功用。

高档外设总线结构,以进步功率

在许多MCU使用,外设的操作是相同的CPU和内存操作相同重要。它能够进步转化功率,假如有与要害外设功用以及根据CPU的功用,选用先进的总线接口。瑞萨RX600 MCU有多个外围总线,可用于更有用地传达带宽负载。如图2所示,RX600不只具有用于面向CPU动作的总线矩阵(在该图的顶部示出),但多个外围总线(在图的底部示出),以更好地智能外设之间分配带宽。甲明显量周流量历来不需求拜访CPU总线矩阵和这个进步了数据传输功率,而不添加CPU总线矩阵的巨细,通常是更高的功用以及大芯片尺寸和更高功率子体系。

图2:瑞萨RX600多总线架构扩展带宽负载。