1. 封闭看门狗

由于要运用仿真器调试,加断点后MCU被挂起,会导致看门狗被触发而将MCU复位。因而在调试阶段,咱们需求先封闭看门狗。封闭看门狗的办法是:

WDTCTL = WDTPW + WDTHOLD;

WDTCTL是一个16位的寄存器,望文生义,便是看门狗的操控寄存器。WDTHOLD是操控看门狗开关的标志位。给WDTHOLD置位即封闭看门狗。可是这个WDTPW是什么呢?查手册得知WDTPW是看门狗的暗码,这是一个宏,被界说为了0x5A00,这个暗码是干什么用的呢?本来,WDTCTL寄存器是一个十分特别的寄存器,为了避免程序反常时意外封闭看门狗,对它进行赋值操作时有必要将其新值的高8位设为0x5A这个特定的值,也便是“暗码”。假如赋值时新值的高8位不是0x5A,会导致MCU当即被复位。总归,对WDTCTL进行任何修正操作时,都要加上WDTPW的值。

2. 时钟体系

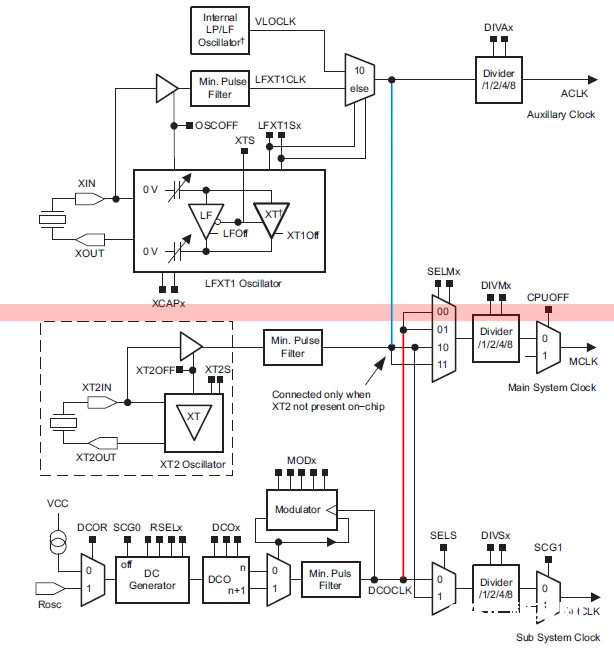

关于玩51单片机的人来说,学习MSP430的时钟体系是很苦楚的,也很推翻的。MSP430为了做到超低功耗,对时钟体系进行了精妙的规划。网上有文章专门解说MSP430的时钟体系,还有生动的配图。但惋惜的是这些解说都多多少少的存在问题乃至是过错的。已然说人家讲得欠好,我也就大胆说说自己的了解。对时钟体系最精确的描绘当然便是手册里的框图了:

我不喜欢看这种框图,觉得特别杂乱,看起来累。可是静下心来看它时,你会发现其实它并不是那么杂乱,许多困惑的问题也就方便的解决了。仅有需求你了解的布景常识是,你有必要要知道啥是多路挑选器(Mux)。。。

首要,MSP430的时钟体系有这么几个概念。

时钟源:发生震动的时钟信号。MSP430中最多有4个时钟源,分别是:DCO(数控晶振),VLO(超低功耗低频晶振),LFXT1(低频外部晶振),XT2(高频外部晶振)。在Value Line产品中,并非支撑悉数的四种时钟源。以MSP430G2231为例,内置了DCO和VLO,XT1能够自己焊接,XT2不支撑。

时钟:供体系设备运用的时钟信号,通常是时钟源的原始信号通过分频后得到。MSP430有3个时钟,分别是:MCLK(主时钟,供CPU中心运用),ACLK(辅佐时钟,供外围设备运用),SMCLK(子体系时钟,供外围设备运用)。

每个时钟都能够装备(1)从指定的时钟源取得信号 (2)对信号进行/1/2/4/8分频 (3)时钟开关

上面的框图咱们从中心横向的红线分隔看,上面一部分是低频时钟,LFXT1Sx这两个标志位用于挑选运用哪个时钟源来驱动体系的低频时钟。蓝色的线便是低频时钟源的输出。下面一部分是高频时钟,赤色的细线是高频时钟的输出(对没有XT2的芯片来说)。需求留意的是,这条蓝色线接在LFXT1Sx对应的数据挑选器的后边。也便是说,体系只能挑选一个低频时钟。比方我挑选VLO作为ACLK的时钟源,那蓝色那条线上便是VLO的时钟信号。那即便我有外部晶振,也不能挑选LFXT1作为MCLK的时钟源。便是这种机制,许多人没有了解清楚(或许没有表达清楚),致使网上的大部分教程都在说,MCLK是从ACLK和DCO中二选一,这样说是不精确的。由于蓝色的线在ACLK的分频器之前,所以并不受ACLK分频设置的影响,因而蓝色线上跑的并不是ACLK时钟信号,而是ACLK的时钟源信号。

更精确的了解是这样的:MCLK依然是从DCO、VLO、LFXT1和XT2(假如有的话)中四选一,ACLK依然是从LFXT1和VLO中二选一,SMCLK依然能够从DCO和XT2(假如有的话)中二选一(假如没有XT2就在DCO、LFXT1、VLO中三选一)。只不过有一个束缚,那便是假如MCLK或许SMCLK想要挑选VLO或许LFXT1,那就有必要跟ACLK选的相同。

在绝大部分Value Line产品中(以MSP430G2231为例),你能够选用更简略的记法:低频时钟源从LFXT1和VLO中选一个,高频时钟源只要DCO一个。因而对体系时钟(MCLK, ACLK, SMCLK)来说,只要2个时钟源,一个低频一个高频。三个体系时钟都能够挑选运用低频时钟源(图中蓝线)或许高频时钟源(图中红线)。(2012年7月11日订正:MCLK和SMCLK能够从低频和高频中选一个,而ACLK只能挑选低频)

———以下内容均以MSP430G2231和MSP430G2553芯片为例,即不存在XT2———

3. 详细编程,对时钟源和体系时钟的装备和运用

(1)低频时钟源装备——寄存器BCSCTL3 (Basic Clock System Control Register 3)

装备低频时钟的时钟源其实便是修正上面图中的LFXT1Sx,这两个标志位坐落BCSCTL3这个8位寄存器的第4、5位。

//运用频率约为12kHz的VLO作为低频时钟源

BCSCTL3 |= LFXT1S_2;

头文件中界说了LFXT1S_2,其实便是第4位为1,第5位为0. 意义是运用VLO

// 运用Launchpad自带的32768Hz外部晶振,电容12.5pF

BCSCTL3 |= LFXT1S_0 + XCAP_3;

头文件中界说的LFXTS_0意义是运用外部晶振,一起设置XCAP_3,意义是晶振的负载%&&&&&%是12.5pF

—————————-待续,,,下面的还没写完——————————

(2)高频时钟源的装备——

(3)体系时钟MCLK的时钟源挑选——寄存器BCSCTL2 (Basic Clock System Control Register 2)

// 清晶振过错标志位

IFG1 &= ~OFIFG;

// 不明白。。。

__bis_SR_register(SCG1 + SCG0);

//体系时钟挑选为低频,/8分频

BCSCTL2 |= SELM_3 + DIVM_3;