1.导言

跟着电子技能的开展,在现代电子产品的毛病检测中,往往需求频率和起伏都能主动调理的正弦信号源,而且要求该信号源发生的信号频率稳定性好,转化速度快,具有调频、调幅和调相的功用。本文结合实际需求,提出一种依据单片机和FPGA的直接频率数字组成器的规划计划,能够发生两路频率和相位均可调的正弦波信号,到达了预订的要求。

2.体系计划规划

2.1 体系的功用剖析

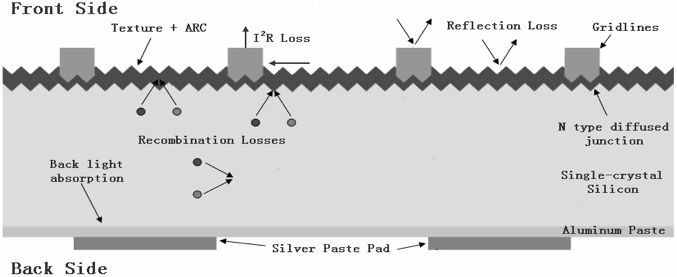

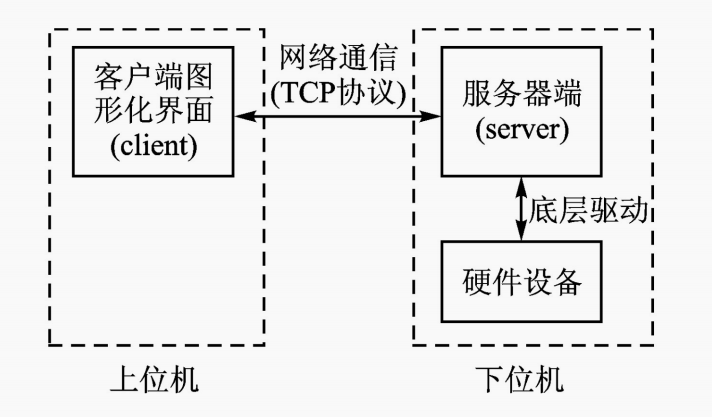

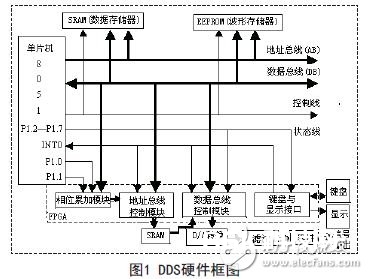

体系首要由单片机最小体系、存储器电路、FPGA模块、键盘与显现接口电路、D/A转化电路、低通滤波电路组成,其硬件框图如图1所示。通过键盘输入频率操控字、相位操控字和幅值操控字,单片机最小体系操控FPGA模块发生用户需求的正弦波信号,再通过DA转化,最终通过低通滤波器生成滑润的正弦波信号。

体系的功用要求:频率规模20Hz~20KHZ,步进20Hz;差0o~359o,步进1o;两路输出正弦波信号,峰峰值分别在0.3V~5V改变;数字显现频率、相位差。

2.2 体系完结的原理

2.2.1 DDS的根本原理

直接数字频率组成器(DDFS)的根本原理:

DDS是运用采样定理,依据相位距离对正弦信号进行取样、量化、编码,然后储存在EPROM中构成一个正弦查询表,通过查表法发生波形。

它是由参阅时钟、相位累加器、正弦查询表和D/A转化器组成,如图2所示。

相位累加器由N位加法器与N位累加寄存器级联构成,其原理框图如图3所示。每来一个时钟脉冲Fc,N位加法器将频率操控数据K与累加寄存器输出的累加相位数据相加,把相加后的成果Y送至累加寄存器的输入端。累加寄存器一方面将在上一时钟周期效果后所发生的新的相位数据反应到加法器的输入端,以使加法器鄙人一时钟的效果下持续与频率操控数据K相加;另一方面以相加后的成果构成正弦查询表的地址,取出表中与该相位对应的单元中的起伏量化正弦函数值,作为取样地址值送入起伏/相位转化电路。这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完结相位到幅值转化。波形存储器的输出送到D/A转化器,D/A转化器将数字量方式的波形幅值转化成所要求组成频率的模拟量方式信号。

相位累加器的最大计数长度与正弦查询表中所存储的相位分隔点数相同,在取样频率(由参阅时钟频率决议)不变的情况下,因为相位累加器的相位增量不同,将导致一周期内的取样点数不同,输出信号的频率也相应改变。

假如设定累加器的初始相位,则能够对输出信号进行相位操控。由采样原理可知,假如运用两个相同的频率组成器,并使其参阅时钟相同,一起设定相同的频率操控字、不同的初始相位,那么在原理上就能够完结输出两路具有必定相位差的同频信号。

2.2.2 FPGA完结的直接数字频率组成器

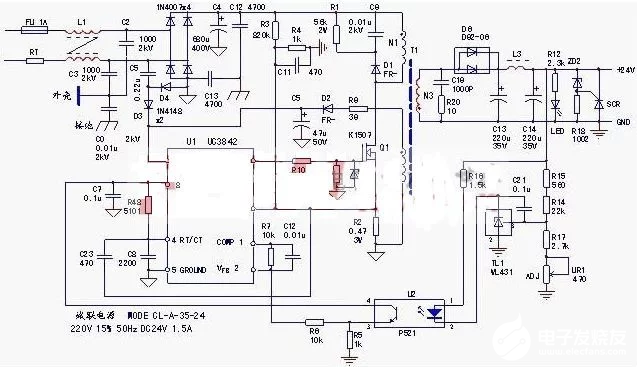

依据DDS的根本原理,运用Altera公司的FPGA芯片FLEX10系列器材设法将波形采样点的值顺次通过数模转化器(MDAC)转化成模拟量输出,可到达预期的意图,具有较高的性价比。其根本环节由计数器(Counter)、只读存储器(EPROM)、数模转化器(MDAC)和滤波器等组成。

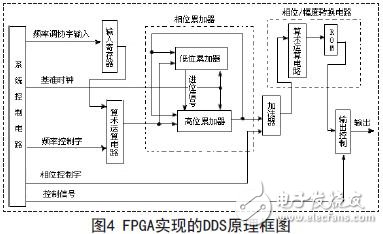

详细计划如下:累加器由加法器和D触发器级联组成,在时钟脉冲fc的操控下,对输入频率操控字K进行累加,累加满量时发生溢出。相位累加器的输出对应于该组成周期信号的相位,而且这个相位是周期性的,在0~2π 规模内起改变。相位累加器位数为N,最大输出为2N-1,对应于2π的相位,累加一次就输出一个相应的相位码,通过查表得到正弦信号的起伏,然后经D/A转化及低通滤波器滤除不需求的取样重量,以便输出频谱纯洁的正弦波信号。整个DDS电路的电路结构如图4所示。

3.体系硬件电路规划

在功用上,单片机与FPGA有很强的互补性。

单片机具有性价比高、功用灵敏、易于人机对话、杰出的数据处理才能等特色;FPGA则具有高速、高可靠性以及开发快捷、标准等长处。用这两类器材相结合的电路结构在许多高功用仪器仪表和电子产品中仍将被广泛使用。

单片机的功用首要是传送频率操控字K1和相位操控字K2给FPGA处理;生成波形表存储于EEPROM中;操控键盘的写入和LED的显现;操控DAC0832进行幅值转化。在每次加电前都要通过单片机初始化,将写好的程序加载在信号发生体系上,然后把从键盘上输入的数据送到中央处理芯片上,信号通过低通滤波器输出的一起,LED数码管显现信号的频率和相位差。

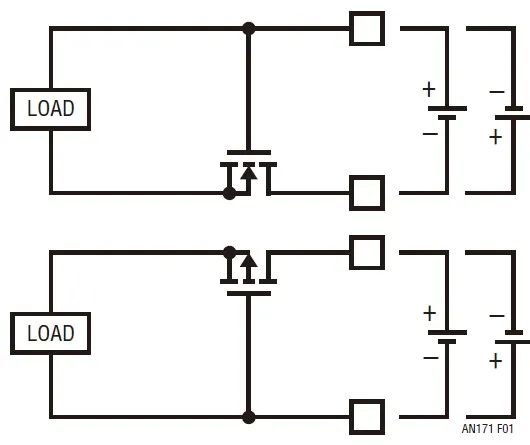

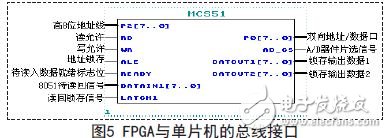

FPGA与单片机的总线接口如图5所示。

4.体系的完结

4.1 体系的核算与仿真

用MAX+plusⅡ规划DDS体系数字部分最简略的办法是选用原理图输入。相位累加器调用lmp_add_sub加减法器模块,相位累加器规划的好坏将直接影响到整个体系的速度,选用流水线技能能大起伏地提高速度。波形存储器(ROM)通过调用lpm_rom元件完结,其LPM_FILE的值。mif是一个寄存波形幅值的文件。波形存储器规划首要考虑的问题是其容量的巨细,运用波形幅值的奇、偶对称特性,能够节约3/4的资源,这是十分可观的。为了进一步优化速度的规划,能够挑选菜单Assignal GlobalProject Logic Synthesis的选项Optimize10(速度),并设定Global Project LogicSynthesis Style为FAST,经寄存器功用剖析最高频率到达100MHZ以上。DDFS中的分频、累加器及正弦波的仿真如图6、7、8所示。

4.2 单片机的编程完结

因为运用了8051单片机及FPGA构成的DDS体系,外围电路变得反常简略,而FPGA的运用使单片机的程序大大简化。DDS体系及其与单片机的接口部分用VHDL言语写。在规划过程中波形频率随CPU的频率而改变,单片机的实时时钟通过PLL倍频电路发生体系时钟频率fc,fc再通过分频得到CPU时钟频率(CPUCLK)可通过对P_SystemClock(写)(7013H)单元编程来操控。在规划过程中,波形修改的第一步便是进行CPU频率挑选,挑选最高频和最低频作为粗调,在用键盘和中止进行微调,以便到达所需的频率、相位及其幅值。单片机编程的整体流程图如图9所示。

5.结束语

本文结合实际需求,提出一种依据单片机和FPGA的直接频率数字组成器的规划计划。计划以FPGA为中心模块,以单片机为操控模块,选用直接数字频率组成技能规划了双通道相位联系可调的信号发生器,输出信号频率规模为0~20KHz,频率分辨率高于20Hz,相位调理步进1o.两个通道不只能够输出相同频率的信号,还能够输出不同相位、不同幅值的正弦信号。经体系仿真标明,本计划可到达预订要求,使用便利灵敏。