摘要:跟着现代导航技能的开展,惯性导航作为一种自主导航技能现已广泛应用于多种兵器体系中,而导航核算机又是捷联式惯导的中心部件。文章提出了一种选用依据DSP的某型导航核算机模块的解决计划,规划计划选用双处理器TMS320C6713,对数字电路接口完成了光电阻隔,选用 FPGA完成对多路信号的中心处理,并具有CAN总线通讯接口。本文对核算机单元的硬件规划与完成办法进行了较为翔实的描绘。该核算机单元满意了某型兵器惯性导航体系的运用需求。

导言

跟着现代兵器技能的开展,作为惯性导航体系操控中心的核算机单元,其一体化和集成度越来越高、接口越来越丰厚。本文以某型导航核算机模块的需求作为布景,介绍了一种依据双DSP(TMS320C6713)和FPGA的核算机模块的硬件规划与完成计划,较好得满意了导航核算机的各操控需求,一起具有小型化和一体化的特色。

1 总体规划

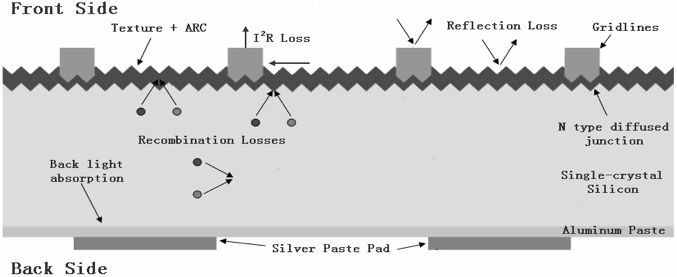

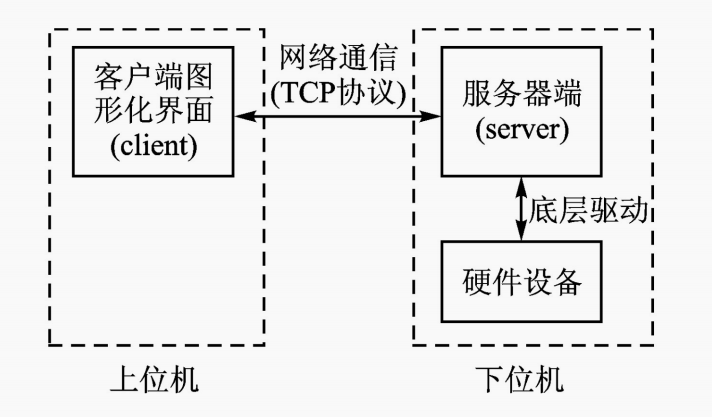

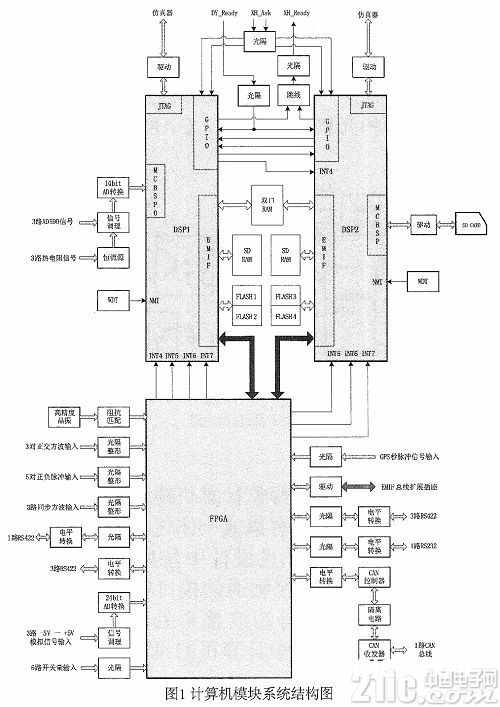

导航核算机板由两个DSP构成,首要功用是守时收集三路陀螺正交编码信号、三路加速度计的输入和里程计输入信号,并对收集的数据进行必要的处理,以完成导航解算;一起将收集数据经过RS422总线和CAN总线发送给地上监测设备;经过RS422总线接纳相关的指令和相关的参数。核算机体系结构见图1所示。

核算机单元各操控接口丰厚,其首要功用模块包含:处理器相关电路、正负脉冲信号处理电路、正交方波信号处理电路、异步串行接口电路、AD测温电路、CAN总线接口电路、开关量输入输出电路、模拟量输入电路、电源转化电路和FPGA等。

2 具体规划

由于核算机单元接口很多,在具体规划中仅对首要的以下电路作出介绍:处理器相关电路、正负脉冲信号处理电路、正交方波信号处理电路、AD测温电路和CAN总线接口电路。

2. 1 处理器及其外围电路

处理器及其外围电路包含双TMS320C6713处理器、时钟电路、JTAG驱动电路、复位电路、存储器电路。

双DSP各自具有不同的操控功用分工,两者均经过各自的EMIF部分总线和FPGA通讯,拜访和操控FPGA中不同的操控功用模块,两者之间能够经过双端口RAM存储器完成相互通讯。

处理器最高作业频率200MHz,最大处理才能1200MFLOPS,经过EMIF部分总线完成对SDRAM和FLASH存储器的无缝接口,单片支撑4路外部中止,片内两路32位守时器。

2.2 正负脉冲信号处理电路

信号方式为正交方波信号(需阻隔、整形),5V TTL信号,正交方波信号先经过RC滤波电路和维护二极管,然后经过光隔进入FPGA。

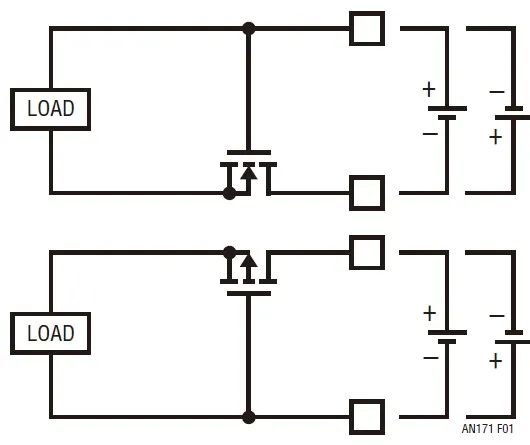

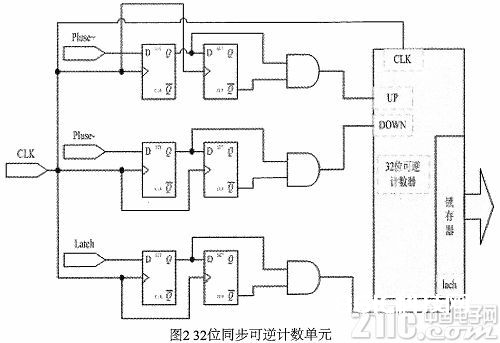

5路正负脉冲信号输入为可逆脉冲,频率最高256KHz,每个通道加速度计输入包含3路信号,分另0是G+(H+、I+、E+、F+)、G-(H-、 I-、E-、F-)、GND(公共地),G+信号上有脉冲时计数值添加,G-信号上有脉冲时计数值削减,上电默认值为满量程的中心值,当采样时钟中止发生时,将计数成果存入锁存器内。规划时5路信号别离选用32位同步可逆计数单元来完成,正负脉冲和锁存信号均经同步处理,同步时钟为DSP1的体系时钟,锁存信号为经分频后的采样时钟S_CK。32位同步可逆计数单元结构图如图2所示。读一次锁存器内的32位计数值需进行两次读操作,别离读出低16位和高 16位数值,然后整合。

2.3 正交方波信号处理电路

3对正交方波信号由3个通道输入,每个通道包含A+A-、B+B-、C+C-信号和各自独立地线。信号方式为正交方波信号(需阻隔、整形),5V TTL。

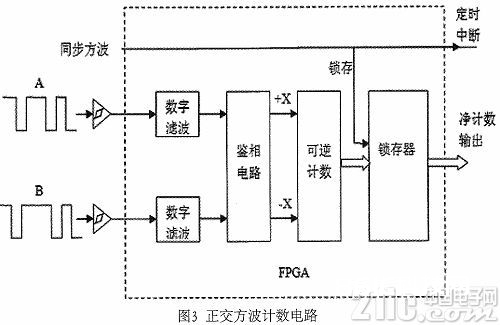

当A+相超前A-相90度时计数值添加,当A+相落后A-相90度时计数值削减,频率最高1MHz。信号进入FPGA后首先进行数字滤波处理,滤波后的信号再进行鉴相,发生四倍频的可逆脉冲信号,然后对可逆脉冲进行计数,当同步方波中止发生时,将计数成果存入锁存器内。信号在滤波后鉴相,得到可逆脉冲后进入32位同步可逆计数单元(图2),此刻的同步时钟为DSP1体系时钟,锁存信号为同步方波中止。正交方波计数电路原理如图3。

信号进入FPGA后经过一个4位推迟数字滤波器,数字滤波器参阅了积分解码器/计数器芯片HCTL2000的规划,原理如图4所示。依据原理图,数字滤波器的输入信号有必要在三个接连的时钟上升沿坚持同一电平,才能够经过4位推迟移位寄存器,因而小于两个时钟周期的噪声脉冲都被按捺掉。

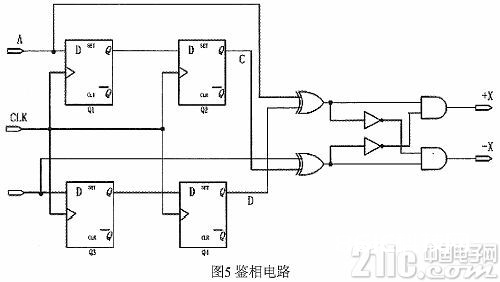

每路正交方波的两个信号经过数字滤波器输出后,进入鉴相电路,经过处理后,变为四倍频的可逆脉冲信号,鉴相电路原理见图5所示。以X正交输入为例,两路输入信号A、B别离经过两级移位寄存器,A经过第二级的输出信号命名为C,B输出信号别离是D,最终输出别离得到正、负通道信号+x和-X,(A![]() D)(not(B

D)(not(B![]() C)),-X=(B

C)),-X=(B![]() C)(not(A

C)(not(A![]() D))。这种鉴相电路具有较强的抗干扰才能,即便A或B输入上有噪声信号经过前面的滤波电路,也会在+X和-X上发生对称的脉冲而相互抵消掉,最终信号输入至32位同步可逆计数单元(图2)。

D))。这种鉴相电路具有较强的抗干扰才能,即便A或B输入上有噪声信号经过前面的滤波电路,也会在+X和-X上发生对称的脉冲而相互抵消掉,最终信号输入至32位同步可逆计数单元(图2)。

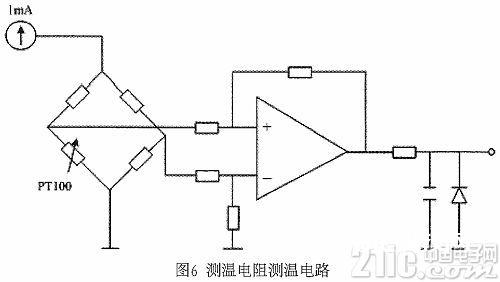

2.4 AD测温电路

测温信号包含3路测温电阻输入。规划中,测温电阻、恒流源与3个高精度电阻组成电桥,如图6所示,电桥两臂中点别离接入运算扩大器,压差信号经同向份额扩大后由AD转化芯片收集温度测验成果。调度扩大后的电压信号由AD转化芯片采样后输入DSP1,AD转化芯片选用串行接口(SPI)芯片,与DSP1的 McBSP0接口衔接。

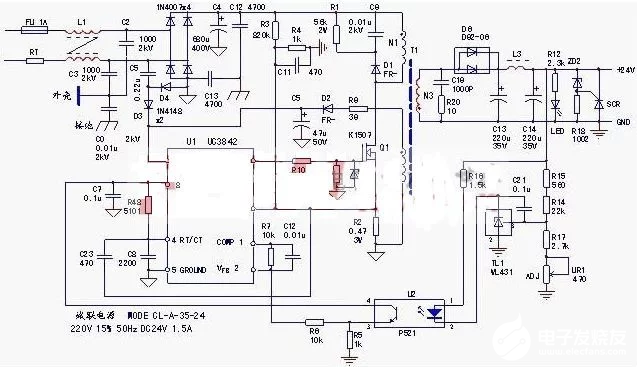

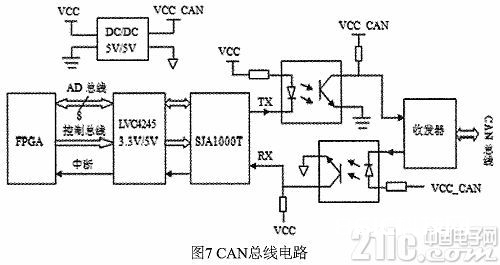

2.5 CAN总线接口电路

CAN总线接口电路包含CAN协议芯片和总线收发器,作业时钟16MHz,协议芯片与收发器之间选用光隔进行阻隔。CAN协议芯片运用AD总线,需求 FPGA将DSP的地址数据总线与AD总线进行转化。由于阻隔的需求,CAN总线电路需求一路阻隔5V电源为收发器和光耦供给电源。CAN总线电路如图7 所示。

3 结束语

本文介绍了一种导航核算机模块的规划与完成办法,此规划办法具有集成一体化、处理才能强和接口丰厚的特色,而且规划中运用了双DSP结合FPGA的架构。一切操控通讯接口完成光电阻隔,对中心计数信号均有滤波整形处理,并配有AD测温电路。本文对导航核算机的规划具有必定的参阅价值。