68亿只晶体管、1,954,560个逻辑单元(容量相当于商场同类最大28nm FPGA的两倍)、305,400个CLB切片的可装备逻辑块(CLB)、21,550Kb的分布式RAM容量、以及2,160个DSP slice、46,512个BRAM、24个时钟办理模块、4个PCIe模块、36个GTX收发器(每个功能达12.5 Gbps)、24个I/O bank和1,200个用户I/O、19W功耗……是的,您没有看错,这一连串令人目不暇接的数字,便是赛灵思(Xilinx)日前宣告可正式供货的“国际最大容量”FPGA Virtex-7 2000T为咱们呈现出的令人震慑的功能指标。

2010年10月,Xilinx高调宣告推出业界首项堆叠硅片互联技能(SSI,Stack Silicon Interconnect)。该公司全球高档副总裁兼亚太区履行总裁汤立人着重说,之前曾有厂商企图经过将两个或多个FPGA进行逻辑互联,创立出更大型的“虚拟FPGA”,终究完成杂乱规划。但往往因为可用I/O数量有限,再加之FPGA间信号传输构成的时延约束功能,以及运用规范的器材I/O来创立多个FPGA之间的逻辑衔接添加功耗等要素,这些尽力都宣告失利。而SSI技能的中心则来自于赛灵思专利的ASMBL架构、微凸块技能以及TSMC的硅通孔(TSV)技能。

2.5D SSI的首要技能打破

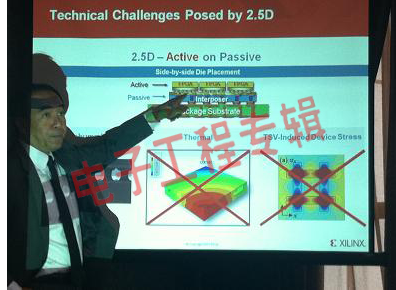

Virtex-7 2000T是Xilinx选用台积电(TSMC)28nm HPL工艺(低功耗高介电层金属闸技能)推出的第三款FPGA。更重要的是,这将是“国际上第一个选用SSI技能的商用FPGA”。赛灵思方面将该项技能命名为2.5D SSI。汤立人坚持以为,2.5D并不意味着就比传统意义上的3D封装功能差。事实上,假如将逻辑单元与内存进行笔直堆叠(Vertical Stacking),也便是所谓的3D封装,现在面临着散热、RAM/Logic等有源层之间因为膨胀系数不同,导致内部应力不均,影响晶体管功能等多项重要应战。“赛灵思相同看好不带中介层的彻底3D IC堆叠技能远景,但从现在来看,该技能在整个工业中完成规范化还要花更长的时刻。”

“咱们的2.5D SSI结构选用并排式芯片布局,将4个经ASMBL架构优化的FPGA Slice并排摆放在硅中介层上,Slice之间具有超越10,000个过孔走线,时延仅为1纳秒。然后再经过微凸块将硅片衔接至硅中介层。”汤立人进一步解说说,“因为选用的是很多低延时、芯片间互连,并衔接至球形栅格阵列,然后也避免了笔直硅片堆叠办法呈现的热通量和规划东西流问题。”

几项关键技能中,赛灵思专有的ASMBL架构是完成SSI技能的根底。在该根底之上,赛灵思又进行了三项严重改善:首要,每个芯片Slice接纳自己的时钟和装备电路;其次,对走线架构进行了改善,经过对芯片进行外表钝化处理,完成了FPGA逻辑阵列内部布线资源的直接衔接,绕开了传统的并行和串行I/O电路;最终,对每个芯片Slice进行进一步加工,构成微凸块,以便将芯片衔接到硅基片上。与选用传统I/O比较,正是这项立异使衔接的数量大幅添加,一起又明显降低了时延和功耗(与规范I/O比较,单位功耗芯片间衔接功能可进步约100倍)。

来自TSMC的无源硅中介层也功不可没。汤立人介绍说,硅中介层开始是针对各种芯片堆叠规划办法而开发的,相当于硅片中一种微型电路板,其上并行放置多个芯片并相互衔接。与有机或许陶瓷基片比较,硅中介层可以供给更好的互联几许结构(走线距离可缩小约20倍),以供给器材规划的互联层级,完成超越1万条芯片间衔接。

经过结合运用硅通孔技能与受控的塌落芯片衔接(C4)焊锡凸块,赛灵思得以将FPGA/中介层堆叠用倒装片拼装技能贴装到高功能封装基片上。这种节操距硅通孔为并行和串行I/O,电源/接地、时钟、装备信号等供给了封装和FPGA之间的衔接。