CPU(Centralprocessingunit)是现代核算机的核心部件,又称为“微处理器”。关于PC而言,CPU的规范与频率常常被用来作为衡量一台电脑功用强弱重要目标。Intelx86架构现已阅历了二十多个年初,而x86架构的CPU对咱们大大都人的作业、日子影响较为深远。

CPU 它是核算机的核心部件,核算机进行信息处理可分为两个进程:

将数据和程序(即指令序列)输入到核算机的存储器中。从第一条指令的地址起开端履行该程序,得到所需成果,完毕运转。CPU的作用是和谐并操控核算机的各个部件履行程序的指令序列,使其有条有理地进行。因而它有必要具有以下底子功用:

a)取指令:当程序已在存储器中时,首要根据程序进口地址取出一条程序,为此要宣布指令地址及操控信号。

b)剖析指令:即指令译码。是对当时获得的指令进行剖析,指出它要求什么操作,并发生相应的操作操控指令。

c)履行指令:根据剖析指令时发生的“操作指令”构成相应的操作操控信号序列,经过运算器,存储器及输入/输出设备的履行,完结每条指令的功用,其间包含对运算成果的处理以及下条指令地址的构成。

将其功用进一步细化,可归纳如下:

能对指令进行译码并履行规则的动作;

能够进行算术和逻辑运算;

能与存储器,外设交流数据;

供给整个体系所需求的操控;

虽然各种CPU的功用目标和结构细节各不相同,但它们所能完结的底子功用相同。由功用剖析,可知任何一种CPU内部结构至少应包含下面这些部件:算术逻辑运算部件(ALU)、累加器、程序计数器、指令寄存器、译码器、时序和操控部件。

许多对电脑知识略知一二的朋友大多会知道CPU里边最重要的东西便是晶体管了,进步CPU的速度,最重要的一点说白了便是如安在相同的CPU面积里边放进去愈加多的晶体管,因为CPU真实太小,太精密,里边组成了数目适当多的晶体管,所以人手是肯定不可能完结的,只能够经过光刻工艺来进行加工的。

这便是为什么一块CPU里边为什么能够数量如此之多的晶体管。晶体管其实便是一个双位的开关:即开和关。假如您回忆起底子核算的年代,那便是一台核算机需求进行作业的悉数。两种挑选,开和关,关于机器来说即0和1。那么您将怎么制造一个CPU呢?在今日的文章中,咱们将一步一步的为您叙述中央处理器从一堆沙子到一个功用强壮的集成电路芯片的全进程。

制造CPU的底子质料

假如问及CPU的质料是什么,咱们都会垂手可得的给出答案—是硅。这是不假,但硅又来自哪里呢?其实便是那些最不起眼的沙子。不可思议吧,价格昂贵,结构杂乱,功用强壮,充溢着神秘感的CPU居然来自那底子一文不值的沙子。当然这中心必定要阅历一个杂乱的制造进程才行。不过不是随意抓一把沙子就能够做质料的,必定要精挑细选,从中提取出最最纯洁的硅质料才行。试想一下,假如用那最最廉价而又储量足够的质料做成CPU,那么制品的质量会怎样,你还能用上像现在这样高功用的处理器吗?

英特尔技能人员在半导体出产工厂内运用主动化丈量东西,根据严厉的质量规范对晶圆的制造进展进行监测。除掉硅之外,制造CPU还需求一种重要的资料便是金属。现在为止,铝现已成为制造处理器内部配件的首要金属资料,而铜则逐步被筛选,这是有一些原因的,在现在的CPU作业电压下,铝的电搬迁特性要显着好于铜。

所谓电搬迁问题,便是指当很多电子流过一段导体时,导体物质原子受电子碰击而脱离原有方位,留下空位,空位过多则会导致导体连线断开,而脱离原位的原子停留在其它方位,会构成其它当地的短路然后影响芯片的逻辑功用,然后导致芯片无法运用。这便是许多Northwood PenTIum 4换上SNDS(北木暴毕综合症)的原因,当本站们第一次给Northwood PenTIum 4超频就急于求成,大幅进步芯片电压时,严峻的电搬迁问题导致了CPU的瘫痪。这便是intel初次测验铜互连技能的阅历,它明显需求一些改善。不过另一方面讲,运用铜互连技能能够减小芯片面积,一起因为铜导体的电阻更低,其上电流经过的速度也更快。

除了这两样首要的资料之外,在芯片的规划进程中还需求一些品种的化学质料,它们起着不同的作用,这儿不再赘述。

CPU制造的预备阶段

在必备原资料的收集作业完毕之后,这些原资料中的一部分需求进行一些预处理作业。而作为最首要的质料,硅的处理作业至关重要。首要,硅质料要进行化学提纯,这一进程使其到达可供半导体工业运用的质料等级。而为了使这些硅质料能够满意集成电路制造的加工需求,还有必要将其整形,这一步是经过溶化硅质料,然后将液态硅注入大型高温石英容器而完结的。

晶圆上的方块称为“芯片(die)”,每个微处理器都会成为个人核算机体系的“大脑”。

然后,将质料进行高温溶化。中学化学课上咱们学到过,许多固体内部原子是晶体结构,硅也是如此。为了到达高功用处理器的要求,整块硅质料有必要高度纯洁,及单晶硅。然后从高温容器中选用旋转拉伸的办法将硅质料取出,此刻一个圆柱体的硅锭就发生了。

从现在所运用的工艺来看,硅锭圆形横截面的直径为200毫米。不过现在intel和其它一些公司现已开端运用300毫米直径的硅锭了。在保存硅锭的各种特性不变的情况下增加横截面的面积是具有适当的难度的,不过只需企业肯投入大批资金来研讨,仍是能够完结的。intel为研发和出产300毫米硅锭而树立的工厂耗费了大约35亿美元,新技能的成功使得intel能够制造杂乱程度更高,功用更强壮的集成电路芯片。而200毫米硅锭的工厂也耗费了15亿美元。下面就从硅锭的切片开端介绍CPU的制造进程。

清洁的空气源源不断地从天花板和地板中的空地中流入室内。无尘车间中的悉数空气每分钟都会屡次替换。

在制成硅锭并保证其是一个肯定的圆柱体之后,下一个进程便是将这个圆柱体硅锭切片,切片越薄,用料越省,天然能够出产的处理器芯片就更多。切片还要镜面精加工的处理来保证外表肯定润滑,之后查看是否有歪曲或其它问题。这一步的质量检验尤为重要,它直接决议了制品CPU的质量。

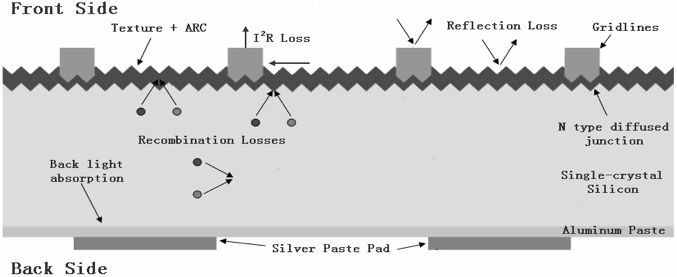

新的切片中要掺入一些物质而使之成为真实的半导体资料,然后在其上刻划代表着各种逻辑功用的晶体管电路。掺入的物质原子进入硅原子之间的空地,彼此之间发生原子力的作用,然后使得硅质料具有半导体的特性。今日的半导体制造多挑选CMOS工艺(互补型金属氧化物半导体)。

其间互补一词表明半导体中N型MOS管和P型MOS管之间的交互作用。而N和P在电子工艺中别离代表负极和正极。大都情况下,切片被掺入化学物质而构成P型衬底,在其上刻划的逻辑电路要遵从nMOS电路的特性来规划,这品种型的晶体管空间利用率更高也愈加节能。一起在大都情况下,有必要尽量约束pMOS型晶体管的呈现,因为在制造进程的后期,需求将N型资料植入P型衬底傍边,而这一进程会导致pMOS管的构成。

在掺入化学物质的作业完结之后,规范的切片就完结了。然后将每一个切片放入高温炉中加热,经过操控加温时刻而使得切片外表生成一层二氧化硅膜。经过亲近监测温度,空气成分和加温时刻,该二氧化硅层的厚度是能够操控的。在intel的90纳米制造工艺中,门氧化物的宽度小到了惊人的5个原子厚度。这一层门电路也是晶体管门电路的一部分,晶体管门电路的作用是操控其间电子的活动,经过对门电压的操控,电子的活动被严厉操控,而不管输入输出端口电压的巨细。

预备作业的终究一道工序是在二氧化硅层上掩盖一个感光层。这一层物质用于同一层中的其它操控运用。这层物质在枯燥时具有很好的感光作用,并且在光刻蚀进程完毕之后,能够经过化学办法将其溶解并除掉。

● 光刻蚀

这是现在的CPU制造进程傍边工艺非常杂乱的一个进程,为什么这么说呢?光刻蚀进程便是运用必定波长的光在感光层中刻出相应的刻痕, 由此改动该处资料的化学特性。这项技能关于所用光的波长要求极为严厉,需求运用短波长的紫外线和大曲率的透镜。刻蚀进程还会遭到晶圆上的污点的影响。每一步刻蚀都是一个杂乱而精密的进程。

规划每一步进程的所需求的数据量都能够用10GB的单位来计量,并且制造每块处理器所需求的刻蚀进程都超越20步(每一步进行一层刻蚀)。并且每一层刻蚀的图纸假如扩大许多倍的话,能够和整个纽约市外加市郊规模的地图比较,乃至还要杂乱,试想一下,把整个纽约地图缩小到实践面积巨细只要100个平方毫米的芯片上,那么这个芯片的结构有多么杂乱,可想而知了吧。

当这些刻蚀作业悉数完结之后,晶圆被翻转过来。短波长光线透过石英模板上镂空的刻痕照射到晶圆的感光层上,然后撤掉光线和模板。经过化学办法除掉露出在外边的感光层物质,而二氧化硅立刻在陋空方位的下方生成。

英特尔技能人员在监测主动湿刻蚀东西中的晶圆,该工艺可铲除晶圆上剩余的操作助剂或许污染物。

● 掺杂

在残留的感光层物质被去除之后,剩余的便是充溢的沟壑的二氧化硅层以及露出出来的在该层下方的硅层。这一步之后,另一个二氧化硅层制造完结。然后,参加另一个带有感光层的多晶硅层。多晶硅是门电路的另一品种型。因为此处运用到了金属质料(因而称作金属氧化物半导体),多晶硅答应在晶体管行列端口电压起作用之前树立门电路。

感光层一起还要被短波长光线透过掩模刻蚀。再经过一部刻蚀,所需的悉数门电路就现已底子成型了。然后,要对露出在外的硅层经过化学办法进行离子轰击,此处的意图是生成N沟道或P沟道。这个掺杂进程创建了悉数的晶体管及彼此间的电路衔接,没个晶体管都有输入端和输出端,两头之间被称作端口。

● 重复这一进程

从这一步起,你将继续增加层级,参加一个二氧化硅层,然后光刻一次。重复这些进程,然后就呈现了一个多层立体架构,这便是你现在运用的处理器的萌发状况了。在每层之间选用金属涂膜的技能进行层间的导电衔接。今日的P4处理器选用了7层金属衔接,而Athlon64运用了9层,所运用的层数取决于开始的地图规划,并不直接代表着终究产品的功用差异。

● 封装测验进程

接下来的几个星期就需求对晶圆进行一关接一关的测验,包含检测晶圆的电学特性,看是否有逻辑过错,假如有,是在哪一层呈现的等等。然后,晶圆上每一个呈现问题的芯片单元将被独自测验来确认该芯片有否特别加工需求。

然后,整片的晶圆被切开成一个个独立的处理器芯片单元。在开始测验中,那些检测不合格的单元将被遗弃。这些被切开下来的芯片单元将被选用某种办法进行封装,这样它就能够顺畅的刺进某种接口规范的主板了。大大都intel和AMD的处理器都会被掩盖一个散热层。

在处理器制品完结之后,还要进行全方位的芯片功用检测。这一部会发生不同等级的产品,一些芯片的运转频率相对较高,所以打上高频率产品的称号和编号,而那些运转频率相对较低的芯片则加以改造,打上其它的低频率类型。这便是不同商场定位的处理器。而还有一些处理器可能在芯片功用上有一些不足之处。比方它在缓存功用上有缺点(这种缺点足以导致绝大大都的CPU瘫痪),那么它们就会被屏蔽掉一些缓存容量,降低了功用,当然也就降低了产品的价格,这便是Celeron和Sempron的由来。

在CPU的包装进程完结之后,许多产品还要再进行一次测验来保证从前的制造进程无一遗漏,且产品彻底遵循规范所述,没有误差。