到目前为止,咱们已经在之前的文章中聊过Zynq SOC内部的 PS和PL,以及在Zynq SoC PS部分的ARM Cortex-A9处理器上运转的操作体系。但是有一个范畴咱们还没有去探究过,那便是在芯片的PL上构建软核处理器。PicoBlaze在赛灵思软核中是一个比较常见的软核。它是一个8位处理器,因为它的高精确性(每条指令需求两个周期),许多依据赛灵思可编程器材的体系规划运用PicoBlaze 软核处理器来替代状态机和其他操控结构。你乃至能够运用PicoBlaze 处理器经过I2C和RS232总线完成串行通讯,使规划愈加精简而且节约规划时刻。

咱们应该做的榜首件事便是从PicoBlaze专区下载最新版别的PicoBlaze处理器。这个最新的PicoBlaze处理器支撑UltraScale 和7系列一切可编程器材(包括Zynq SOC)。

咱们的意图是让其作为一个规范的IP模块,咱们能够打包而且增加到咱们的VIVADO模块图中。但是,在这之前,咱们榜首步是得了解下随PicoBlaze处理器会带来什么东东,以及它的开发流程。在咱们的下载目录中咱们将看到以下文件:

1、KCPSM6.Vhd:这是PicoBlaze 处理器的源代码文件。

2、KCPSM6.exe:这是一个汇编程序用于生成机器代码和文件所需的内存。

3、ROM_Form.vhd: 这是被汇编可履行文件用来生成VHDL文件,该文件包括了咱们树立的方针程序。

4、KCPSM6_design_template.vhd: 这是一个PicoBlaze 处理器的例化模板文件。

5、All_kcpsm6_syntax.psm:该文件界说了一切的汇编指令和语法。

在PL上完成PicoBlaze 的开发流程是:

1、编写程序可履行PicoBlaze程序。在这个比如中,咱们将完成一个简略的流水灯。咱们能够运用all_KCPSM6_syntax.psm 文件作为一个快速参阅,里边有咱们要用到的PicoBlaze 汇编指令,一起在下载的文件中也有很多的用户攻略(PDF)能够让咱们快速上手。

2、写完这个简略的程序,咱们就用KCPSM6.exe汇编器进行编译,它将树立一个用咱们对应的程序名命名的RAM文件。这个文件内包括一些将被PicoBlaze 操控器履行的程序,你必须将这个文件链接到PicoBlaze 处理器来树立功用体系,

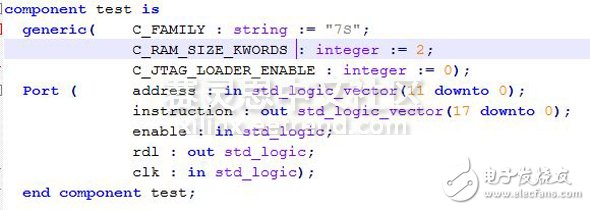

3、修正RAM文件巨细,如下图所示,依据芯片系列将6S改成7S,而且挑选内存巨细为2K:

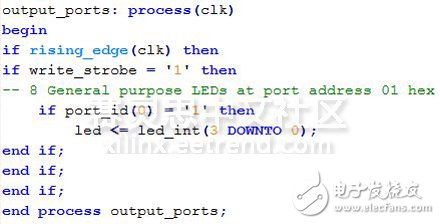

4、在同一个文件夹内,创立一个顶层文件将处理器和RAM 结合PicoBlaze所需的其他代码连接起来 。比如说,当写成如下时便是声明它作为输出端口:

5、运用VIVADO的东西—>“树立和打包IP”选项来新建一个IP,将以上三个文件打包成一个IP。

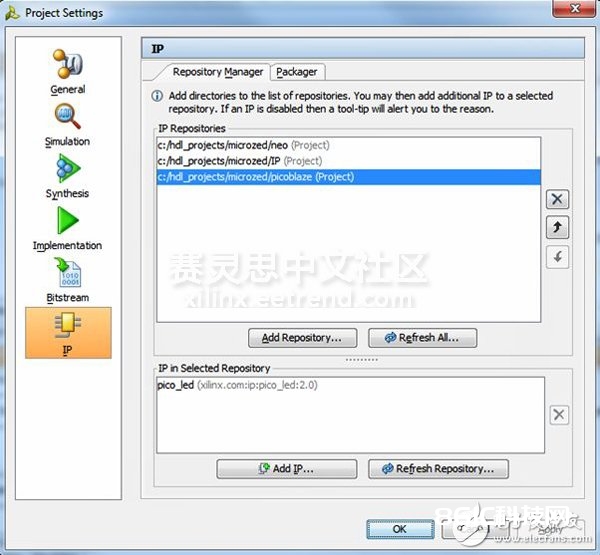

6、在打包这个程序之后,咱们查看承认下是否被包括进来成为一个库房,(假如没有,我将手艺增加)而且将这个IP模块增加到模块图。

7. 将PicoBlaze 模块的时钟链接到FPGA时钟(设置为40MHZ),而且界说三个输出接口连接到MicroZed 的LED对应的IO上。

8. 编译规划而且导出到SDK

当咱们编译完这个规划,假如咱们有一个JTAG连接器,咱们将位流文件烧录到FPGA而且看看LED是否有闪耀,或许咱们能够导出到SDK而且树立一个Boot文件,在上电之后经过Boot文件来运转这个程序。

我将在下次深入探讨咱们刚刚树立的规划。一起,我将这个Demo用到的文件也附加到这个博客中。我供给了PSM文件和顶层文件。假如你下载了PicoBlaze软核,你能够运用PicoBlaze 汇编器来生成一个Test.vhd内存文件。