SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备发动一个与从设备的同步通讯,然后完结数据的交流。SPI 接口由SDI(串行数据输入),SDO(串行数据输出),SCK(串行移位时钟),CS(从使能信号)四种信号构成,CS 决议了仅有的与主设备通讯的从设备,如没有CS 信号,则只能存在一个从设备,主设备通过发生移位时钟来建议通讯。通讯时,数据由SDO 输出,SDI 输入,数据在时钟的上升或下降沿由SDO 输出,在紧接着的下降或上升沿由SDI 读入,这样通过8/16 次时钟的改动,完结8/16 位数据的传输。

SPI通讯

该总线通讯依据主-从装备。它有以下4个信号:

MOSI:主出/从入

MISO:主入/从出

SCK:串行时钟

SS:隶属挑选

芯片上“隶属挑选”(slave-select)的引脚数决议了可连到总线上的器材数量。

数据方向和通讯速度

SPI总线接口及时序

SPI总线包含1根串行同步时钟信号线以及2根数据线。

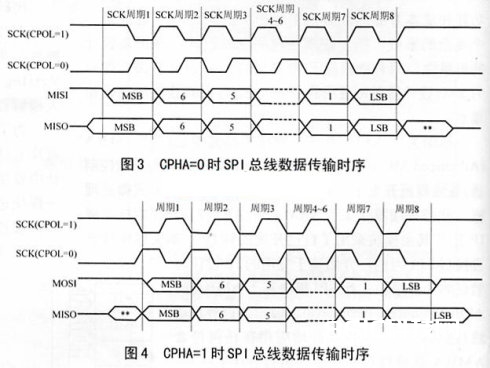

SPI模块为了和外设进行数据交流,依据外设作业要求,其输出串行同步时钟极性和相位能够进行装备,时钟极性(CPOL)对传输协议没有严重的影响。假如CPOL=0,串行同步时钟的闲暇状况为低电平;假如CPOL=1,串行同步时钟的闲暇状况为高电平。时钟相位(CPHA)能够装备用于挑选两种不同的传输协议之一进行数据传输。假如CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;假如CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通讯的外设音时钟相位和极性应该共同。SPI接口时序如图3、图4所示。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的操控下,两个双向移位寄存器进行数据交流。

| 脉冲 | 主机sbuff | 从机sbuff | sdi | sdo |

| 0 | 10101010 | 01010101 | 0 | 0 |

| 1上 | 0101010x | 1010101x | 0 | 1 |

| 1下 | 01010100 | 10101011 | 0 | 1 |

| 2上 | 1010100x | 0101011x | 1 | 0 |

| 2下 | 10101001 | 01010110 | 1 | 0 |

| 3上 | 0101001x | 1010110x | 0 | 1 |

| 3下 | 01010010 | 10101101 | 0 | 1 |

| 4上 | 1010010x | 0101101x | 1 | 0 |

| 4下 | 10100101 | 01011010 | 1 | 0 |

| 5上 | 0100101x | 1011010x | 0 | 1 |

| 5下 | 01001010 | 10110101 | 0 | 1 |

| 6上 | 1001010x | 0110101x | 1 | 0 |

| 6下 | 10010101 | 01101010 | 1 | 0 |

| 7上 | 0010101x | 1101010x | 0 | 1 |

| 7下 | 00101010 | 11010101 | 0 | 1 |

| 8上 | 0101010x | 1010101x | 1 | 0 |

| 8下 | 01010101 | 10101010 | 1 | 0 |

这样就完结了两个寄存器8位的交流,上面的上表明上升沿、下表明下降沿,sdi、sdo相对于主机而言的。其间ss引脚作为主机的时分,从机能够把它拉底被迫选为从机,作为从机的是时分,能够作为片选脚用。依据以上剖析,一个完好的传送周期是16位,即两个字节,由于,首要主机要发送指令曩昔,然后从机依据主机的名预备数据,主机鄙人一个8位时钟周期才把数据读回来

SPI 总线是Motorola公司推出的三线同步接口,同步串行3线方法进行通讯:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU与各种外围器材进行全双工、同步串行通讯。SPI主要特点有:能够一起发出和接纳串行数据;能够当作主机或从机作业;供给频率可编程时钟;发送完毕中止标志;写抵触维护;总线竞赛维护等。图3示出SPI总线作业的四种方法,其间运用的最为广泛的是SPI0和SPI3方法(实线表明):

SPI模块为了和外设进行数据交流,依据外设作业要求,其输出串行同步时钟极性和相位能够进行装备,时钟极性(CPOL)对传输协议没有严重的影响。假如CPOL=0,串行同步时钟的闲暇状况为低电平;假如CPOL=1,串行同步时钟的闲暇状况为高电平。时钟相位(CPHA)能够装备用于挑选两种不同的传输协议之一进行数据传输。假如CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;假如CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通讯的外设音时钟相位和极性应该共同。SPI接口时序如图3、图4所示。

二,.SPI功用模块的规划

依据功用界说及SPI的作业原理,将整个IP Core分为8个子模块:uC接口模块、时钟分频模块、发送数据FIFO模块、接纳数据FIFO模块、状况机模块、发送数据逻辑模块、接纳数据逻辑模块以及中止方式模块。

深入剖析SPI的四种传输协议能够发现,依据一种协议,只要对串行同步时钟进行转化,就能得到其他的三种协议。为了简化规划规则,假如要接连传输多个数据,在两个数据传输之间刺进一个串行时钟的闲暇等候,这样状况机只需两种状况(闲暇和作业)就能正确作业。