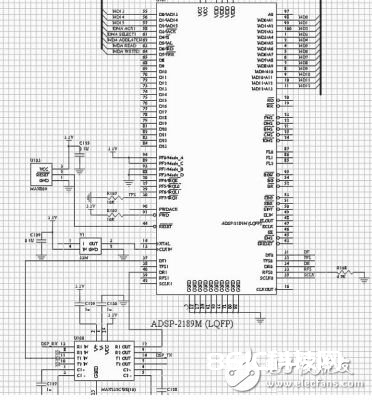

AIS体系是海上移动VHF波段选用TDMA技能交流数据的一种避碰体系,是世界海事安排规则每条船舶有必要装置的设备之一,产品开发依据世界海事安排公布的ITU-R M1371协议。在开发中选用ADSP2189M作为其数据处理渠道,完结各种数据处理,转化,时隙的区分,网络登陆和保护等算法,完结其大部分的主要功用。体系的方法如图1所示。

由电台在161.975MHz和162.025MHz的两个频点上接纳GMSK信号,经GMSK调制解调芯片把模仿数据转化成数字信号,数据流经过上位机完结对正确数据的断定,而且删去数据段的开端、填充和完毕位,把数据经过并行口发往DSP,DSP完结对接纳到数据的处理与剖析,树立整个海域的时隙表,完结TDMA的网络登陆、保护,把相关的数据再以不同格局发送到不同的串口输出,依照ITU-R M.1371协议,以ITDMA(增量时分多址)方法接入网络,以SOTDMA(自控时分多址)方法接连运转,然后到达整个网络的TDMA完整性。因而,信号处理单元在体系中处于重要的方位。

图1 DSP与外部设备接口

ADSP2189M芯片

ADSP2189M芯片是一种定点DSP,其指令周期为13.3ns,运转速度可达75MIPS。处理器包含算术/逻辑单元(ALU),乘法/累加器(MAC)和桶状移位器。存储器选用哈佛结构,有48K的PRAM和32K的DRAM。两个SPORT同步串口,一个守时器以及主机接口能够和主机处理器直接相连。DMA接口包含内部DMA接口(IDMA)和字节DMA接口(BDMA)。

AIS体系中2189M的硬件规划

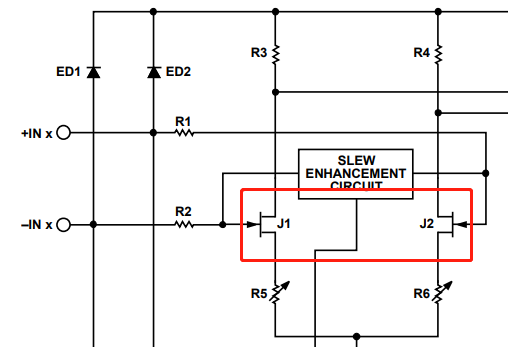

部分电路如图2所示。

·芯片外接33M的晶体,其内部主动倍频到66M;

·一个同步串口SPORT与外部的MCU相连,引脚要接上拉电阻;

·选用IDMA方法与MCU相连,16条并口线衔接,发动方法设置为IDMA方法,其4个MODEA~D设置分别为1,0,1,0;

·完结IDMA引导装载的过程如下;

PWD、EBR、BR、ERSET四个调试引脚有必要外接上拉电阻;

最终写PM(0X0000)的值,程序开端主动履行。

图2 AIS体系的部分电路图

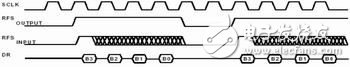

图3 串口接纳时序图

图4 时隙区分图

ADSP2189M接口的软件规划

Sport0的设置

选用同步串口与MCU通讯

DM(0X3FF6)—串口操控寄存器设置如表1所示。

表1中0~3:接纳发送字长,咱们界说为16位字长,设置为1111。6~7:帧同步信号电平,为0,高电平有用。8~9:帧同步信号源,为1,内部产生帧同步信号。

10~11:成帧方法,为1,第二成帧方法。12~13:帧同步,为0,建议通讯有必要要帧同步信号,今后不再考虑帧同步信号。14:SCLK的产生方法,为1,内部产生串行时钟。

DM(0X3FF5)—串口时钟分频系数寄存器dm(sclkdiv)

在ADSP2189芯片中,采样率与分频数之间的联系如下式F(sclk)=f(clkout)/(sclkdiv+1)/2

其间,F(sclk)表明运转时钟,F(clkout)表明外接晶振的输出时钟,sclkdiv表明分频数,即存储器应该赋予的值。

当操控寄存器设置好今后,串口接纳时序如图3所示,接纳到的数据放在接纳缓存区,每接纳完一组数据,写一次接纳标志位,主程序守时检测标志位,当检测到标志位变化时,调用接纳处理子程序。

Sport1和TImer的设置

因为DSP要输出数据到简易显现,经过UART口相衔接,因而把Sport1设置为第二种作业方法(如表2所示)。

DM(0X3FFF)—体系操控寄存器(如表3所示)。

表3中,12:SPORT0的使能,设置为1。11:SPORT1的使能,设置为1。10:SPOER1的功用挑选,设置为0。

用I/O口模仿UART,以9600波特率采样,内部守时中止产生速率为3×9600,在一个电平跳变中产生3次采样,取中心的采样值有用。

DM(0X3FFD)—守时周期寄存器

DM(0X3FFC)—守时计数寄存器

外接33M晶体,寄存器寄存的数值为:

period=frequence×2/(3×9600)-1=2314

芯片以28800波特率产生中止,每次中止程序检测UART的标志位,当标志位有变化时,每3次中止设置一次I/O的输出,直到发送数据完毕。

部分代码设置如下:

ax0 = 2314; //守时器设置

dm(0x3ffc) = ax0;

dm(0x3ffd) = ax0;

ax0 = 0;

dm(0x3ffb) = ax0; //操控寄存器的设置

ax0 = b#0001100000000000;

ax0=b#0111111000001111;

dm(0x3ff6)=ax0; //sport0设置

ax0=0x001f;

dm(0x3ff5)=ax0; //SCLKDIV0

mstat = 0x10; // 乘法器设置

ifc=b#0000000001100001; imask=b#0000100001; //中止敞开

ena TImer;

//敞开守时

主体软件流程

体系选用自主式时分复用,把时刻分红周期性的帧,每一帧再分割成若干时隙(不管帧或时隙都是互不堆叠的),每个时隙便是一个通讯信道,分配给一个用户。体系依据必定的时隙分配原则,使各个移动台在每帧内只能按指定的时隙向对方发射信号(突发信号),在满意守时和同步的条件下,基站能够在各时隙中接纳到各移动台的信号而互不搅扰。

在寄存器中区分两个信道的空间作为海域的时隙表,如图4所示。

网络登陆选用概率继续算法(当发现一个候选时刻段时,台站在0到100之间随机选取一个概率值LME.RTP1,该值与一个0到10的概率LME.RTP2比较,假如LME.RTP1小于或等于LME.RTP2,则挑选这个时刻段,反之,LME.RTP2加上一个概率增量与下一个候选时刻段比较)。在2250个时刻段上随机挑选一个空闲时隙作为网络的接入点,然后以ITDMA方法接入。这种方法是一种先陈述先占用的方法,在当前发射的数据中指明下一个需求发送数据的时隙号,然后到达预先告诉其它台站本身所占用的时隙号,确定在60秒中需求占用的空间。在今后的接连阶段,移动台以SOTDMA方法完结网络的保护和时隙的从头区分。因为协议规则的数据格局中最大只能预知到7分钟的占用状况,所以每隔7分钟,需求在必定范围内从头挑选一个新的空闲时隙发送,以次类推,一向以这种接连的状况运转下去。

当速度产生改动的时分,体系从头以ITDMA的方法完结新的速率下的网络登陆。

结语

本文提出的规划方案,充分利用了DSP的高性能数据处理功用和嵌入式操作体系的实时安稳的特色,选用时分复用的算法,进行一个海域内的网络区分和联接功用。这种DSP信号处理与嵌入式操作体系相结合的方法,能够广泛使用于通讯范畴,具有广泛的使用远景。