为何eFPGA比规范FPGA更高效?主要有如下三大原因。

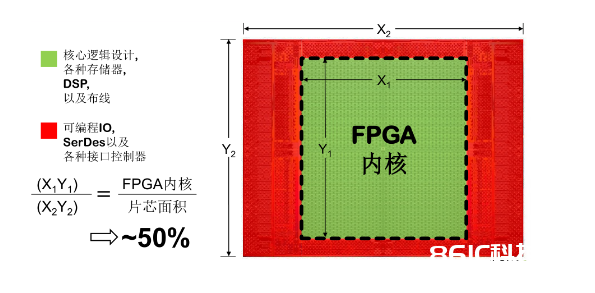

原因1。如下图,传统FPGA构架中,周围的赤色边框放置可编程I/O、高速SerDes及各种接口控制器,这些会占有30%~40%面积。假如做成嵌入式FPGA,这些面积能够省掉。下图公式展现的FPGA和片芯面积的份额。

图:中心电路与边际电路的份额

那么为何Speedcore比规范FPGA更高效?

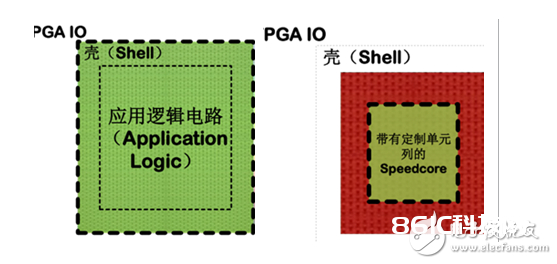

原因2。微软在其有关Catapulit项目(注:某云加快与核算项目)的白皮书中介绍了一种云规划的加快架构。其间增加了一些术语,有shell(壳)和使用。shell是I/O及电路板相关的逻辑电路,使用是在中心逻辑上完成的中心使用。

在此研讨中,这些shell一旦固定到使用中,这些可编程不能被可编程(即固定下来了)。别的,中心使用是会改动的。因而假如拿掉shell,会节约44%的面积。

图:假如去掉shell,会节约近一半的面积(注:左右两图的左上角均为“FPGA IO”)

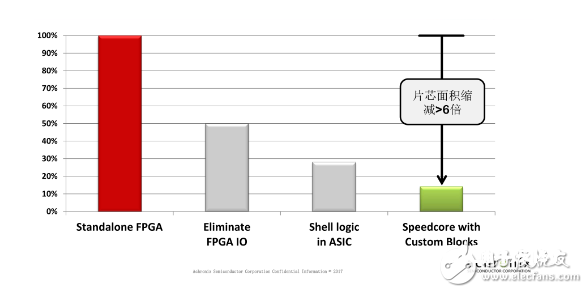

原因3。在把shell剥去的基础上,又增加了自定义的custom block,这是由客户自定义的,散布在speedcore架构之中,有了这种custom block,面积会缩小75%,一起有更低功耗和更高的功用。

根据以上三个原因,即裁剪了FPGA的可编程I/O,shell资源去掉,别的提高了custom block,因而片芯面积大大减缩(如下图)。

图:与独立FPGA比较,把Speedcore的三个优势

Achronix公司不久前推出的定制化的Speedcore custom blocks(定制模块),能够完成最小的片芯面积,供给ASIC级的功用,去构建独立FPGA芯片无法供给的功用。

Achronix作为FPGA的后来者,本年也要跨入1亿美元沙龙。新产品Speedcore 推出一年已占营收1/4,未来三年将占半壁河山。在缝隙中成长,Achronix的商业模式便是不走寻常路。