现在的电子产品商场竞争非常剧烈,厂商都期望能在最短时刻内将新产品推出商场,致使子体系的规划周期越缩越短。在这个开展过程中,FPGA及ASIC的重要性越来越受到重视,例如新体系的许多重要功用往往需求由这些电路履行。关于选用FPGA芯片的体系来说,电源办理是特别需求慎重考虑的关键问题之一。若要为FPGA芯片供给安稳的供电,咱们需求全面审视体系的全体供电需求。这个取态也适用于特别使用集成电路芯片。

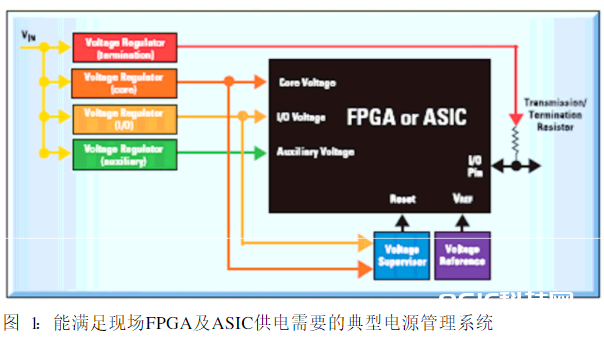

因为体系的开始条件较为杂乱,加上需求考虑的其他要素,例如瞬态行为、开关标准、以及许多其他的要素,因而电源供给体系有必要契合必定的要求,这一点极为重要。若依照有关芯片的使用要求,供电干线有必要绕过芯片或去除与芯片的耦合联系,那么处理旁路或去耦的问题时便需求特别当心。图1所示的是能够满意FPGA芯片供电需求的典型电源办理体系。一般来说,FPGA芯片最低极限需求两个电压为其供给供电。一个是专为“中心”供给供电的电压(1.0伏(V)至2.5伏[典型值]),而另一个是专为输入/输出供给供电的电压(3.3伏[典型值])。许多FPGA芯片更别的需求第三个低噪音、低纹波的电压,以便为辅佐电路供给供电。FPGA芯片所需的典型供电电压是2.5伏或3.3伏,但不同系列的FPGA芯片各有不同的电压需求。

异步降压稳压器

功用:降压(输出电压小于输入电压)

使用条件:一般来说,当输入电压是输出电压的3倍至5倍则输出电流介于0.5A至5A之间特征:若输入电压/输出电压/输出电流的典型值一如以上所供给的数值,规划这款电路便变得非常简略,并且有关规划更可发挥极高的功率

使用规模:一切降压稳压器及控制器同步降压稳压器

功用:降压(输出电压小于输入电压)

使用条件:当有高功率的体系要求输出较高的电流(5A以上),或占空比较低(输入电压比输出电压大5倍以上及/或输出电流不超越0.5A)特征:选用根本的降压稳压器电路布局,其特征是以第二个开关替代二极管,有助削减上述操作状况下的损耗使用规模:任何“同步整流”降压稳压器或控制器线性稳压器

功用:降压(输出电压小于输入电压)

使用条件:一般来说,有关使用的输出电流不能超越1A,压降与噪音也有必要很低

特征:最适用于固定输出电压、低电流及低压降的体系,并且非常简略规划。

使用规模:任何低压降线性稳压器

主张:最合适微功率体系选用

操作时上述电路的每一电压并非输出安稳的电流,事实上电流巨细取决于许多与实践使用有关的要素,例如FPGA芯片的速度及使用率等。操作电流能够低至100mA,也可高至20A。以这些体系来说,输入电压一般比FPGA芯片所取得的任何供电电压都要高,因而需求下降其电压并加以稳压。图2所示的是合适FPGA芯片选用的三款最常用的降压稳压器装备。这三款芯片分别是同步降压稳压器、异步降压稳压器及线性稳压器。为体系选用稳压器时,有必要具体考虑体系的标准要求及稳压器的操作状况,以便作出合作。若要保证体系规划能顺畅运作,咱们也需求同时考虑以下的问题。

输入电压(VIN)FPGA芯片的供电悉数由银盒、底板或中心供电干线供给。输入电压一般介于3伏至15伏之间,部分工业使用体系的输入电压甚至会高达30伏。输入电压或许不会为某一零件供给供电,因为稳压器的输入电压管脚已设定最高的额外供电量,只可为集成电路供给这一数量的供电。

输出电压(VOUT)及输出电流(IOUT)

稳压器的首要作用是安稳电压,换言之,不管输入电压及负载电流怎么动摇,稳压器都可将输出电压安稳在某一水平上。正如从前所说,操作电流能够在低至100mA与高至20A之间的规模内动摇。输入电压、输出电压及输出电流等数值一经确认后,便可知道应该选用什么类型的稳压器。以下是可供工程师参阅的一些前人的经历:

假定功耗不超越1W,应选用线性稳压器

”假定输入/输出电压比小于2:1,而输出电流不超越3A,应选用非同步降压稳压器

假定输入/输出电压比大于2:1,而输出电流又超越5A,应选用同步降压稳压器稳压器将参阅电压与呈现在反应管脚上的极小部分输出电压加以比较,然后依据反应的电压安稳输出电压。参阅电压一般规则输出电压不能超越某一水平。

部分控制器规则发动时刻不能超越某一时限。因为这个时限上的规则,稳压器无法调低太很多的输入电压。控制器的发动时刻最低时限(TONmin.)也为输出电压设定限幅,限制某一频率下的输出电压不能超越某一水平。例如,发动时刻若超越其最低的时限,输出电压便会升越规则的水平。

输入电压(VIN)=12V

输出电压(VOUT)=1.2V

1.2V

D=————-=0.1

12V

示功耗的巨细。但体系规划工程师许多时并不非常理解功率的真实含义。若输入电流无限制或电池寿数的长短不那么重要,功耗和功率也就不再成为最需重视的要素。体系耗散的热能会令体系元件受热,而温度的上升幅度与功耗的巨细有直接的联系。受影响的元件包含集成电路、金属氧化半导体场效应晶体管(MOSFET)、电容器以及电感器。某一面积规模究竟会耗散多少功率?这一点也很重要。一般来说,1W的功率若经过一平方吋的铜质外表耗散掉,加上在没有气流的影响下,温度会因受热而上升40°C。

例如,假定:

输出电压(VOUT)=1.5V

输出电流(IOUT)=15A

功率=90%

功耗=2.5W

这一水平的功率若经过一平方吋的铜质面积耗散掉,会令温度上升100°C。

以下是另一可供参阅的比如:

输出电压(VOUT)=1.5V

输出电流(IOUT)=1.5A

功率=81%

功耗=0.53W

若与前一比如中的90%功率比较,这个功率数字看来不大抱负。但以这个比如来说,一平方吋面积所耗散的功耗只要0.53W,令温度只上升20°C,相比之下,前一比如的温度则上升100°C。以上比如证明功耗比功率显得更为重要。体系规划工程师若理解这个道理,便可为所规划的体系挑选最抱负的功率,以及下降体系的全体本钱。体积体系规划所规则的芯片面积或高度假如缩小,不但会增加体系的本钱,并且功率也会受到影响。例如,小型电感器的有用串联电阻(ESR)一般都比大型电感器高,并且体积细巧的电感器或小型电解电容器一般都较为贵重。选用多层式电路板能够缩小体积,但一般来说会增加全体的本钱。正如上文所说,部分体系规划工程师或许会故意进步开关频率,以便缩小元件体积,但进步开关频率会增加功率损耗。若果没有必要而免强缩小电路板,不但会增加本钱,并且会将功率损耗下降至不必要的低水平。

体系本钱为FPGA芯片供给最具本钱效益的供电一直是体系规划工程师的尽力方向,但将供电本钱尽量下降并不表明要选用最廉价的稳压器。例如,因为内置场效应晶体管的稳压器较为贵重,因而体系规划工程师许多时不加思索便回绝选用这类稳压器,但在某些使用状况下,这类稳压器比设有外置式金属氧化半导体场效应晶体管的稳压器更具本钱效益。此外,设有外置式场效应晶体管的稳压器更易受来自电路板的噪音影响。规划简略而又内置金属氧化半导体场效应晶体管的高集成度开关稳压器便不易受噪音的影响,处理了大部分因为灵敏度过高而发生的噪音问题。此外,咱们也应抛弃选用双通道降压转换器替代两个单通道开关转换器这个想法。因为无需选用多个输入电容器,因而能够大幅节约本钱,并且因为依照规划该两个相位能够异相操作,因而输入电容器的均方根(RMS)纹波电流能够大幅下降。选用双相位控制器能够防止拍频频率的呈现,若选用多个非同步开关稳压器而它们都以略微不同的频率操作,那就必定会发生拍频频率。咱们不要忘掉,真实的本钱是体系物料清单上所开列的本钱,并不是只核算单个元件的本钱。选用FPGA的体系除了要契合这些规则之外,或许还要契合下列任何一项或多项的特别要求:瞬态呼应FPGA芯片的中心电压会发生极高转换率的电流。为此,控制器有必要一方面供给较大的阶梯级负载电流,而另一方面又有必要将输出电压所接受的搅扰减至最低。控制器因应这些负载作出呼应的才能也因而称为瞬态呼应。瞬态呼应、输出电容及其有用串联电阻一旦确认后,会将操作带宽限制在某一规模之内。

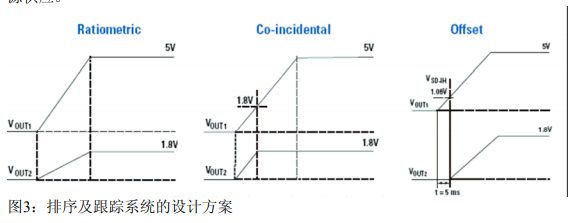

排序及盯梢体系发动时,或许要先发动某一电源供给,然后才连续发动其他的电源供给。若不依照规则的次第发动电源供给,电源供给便会“确定”起来,而FPGA芯片或许会因而而受损或无法履行正常功用。部分FPGA芯片有必要在输入/输出及中心电压之间设有排序及/或盯梢功用。(如欲了解多种不同的排序及盯梢体系规划方案,可参看图3。)若稳压器已设有供电正常(powergood)、答应(enable)、软发动及盯梢等功用,便可容易增加排序及盯梢功用,或许今后能够随时增加这两个功用,令规划更具灵活性。若没有这两个功用,便需加设外接电路以保证能够依照正确次第发动电源供给。

发动的要求咱们若要为FPGA芯片设定电压上升率,能够使用软发动电容器加以设定。此外,发动时的上升电压一般都有必要是单调的,而不是下降的。若电源供给的输出电容较小,发动时的电压会受其影响而跌落。容量够大的%&&&&&%器能够贮存满足的电荷,以便为FPGA芯片供给发动负载瞬态电压。同步操作同步操作功用的作用是保证两个或以上的稳压器能够一起确定在某一频率,避免呈现拍频频率。没有这个同步操作功用的体系都会呈现拍频的现象。

总结

因为不同的体系有不同的要求,加上FPGA芯片或特别使用%&&&&&%各有程度不同的杂乱规划,并且使用率也不尽相同,因而电源供给器的装备有必要因应不同的要求而作出不同的组织。除了输入电压、输出电压及输出电流之外,咱们也要考虑其他的特别要求如排序、盯梢及发动等条件。此外,咱们规划体系时也需求顾及功耗、体积及本钱对体系的影响。