跟着体系对内存容量、带宽、功能等方面的需求进步,体系会接入多个 DRAM Devices。而多个 DRAM Devices 不同的安排方法,会带来不同的作用。本文将对不同的安排方法及其作用进行简略介绍。

1. Single Channel DRAM Controller 安排方法

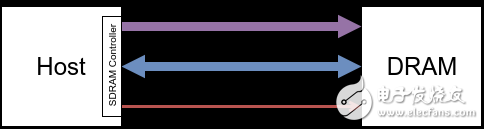

Single Channel 指 DRAM Controller 只要一组操控和数据总线。 在这种场景下,DRAM Controller 与单个或许多个 DRAM Devices 的衔接方法如下所示:

1.1 衔接单个 DRAM Device

Single Channel 衔接单个 DRAM Device 是最常见的一种安排方法。 因为本钱、工艺等方面的要素,单个 DRAM Device 在总线宽度、容量上有所约束,在需求大带宽、大容量的产品中,一般接入多个 DRAM Devices。

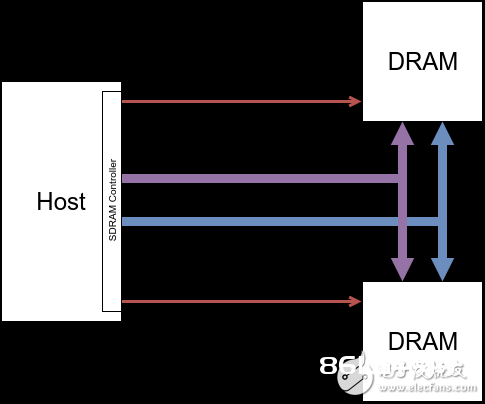

1.2 衔接多个 DRAM Devices

上图中,多个 DRAM Devices 同享操控和数据总线,DRAM Controller 经过 Chip Select 分时独自拜访各个 DRAM Devices。此外,在其中一个 Device 进入刷新周期时,DRAM Controller 能够依照必定的调度算法,优先履行其他 Device 上的拜访恳求,进步体系全体内存拜访功能。

NOTE:CS0 和 CS1 在同一时间,只要一个能够处于使能状况,即同一时间,只要一个 Device 能够被拜访。

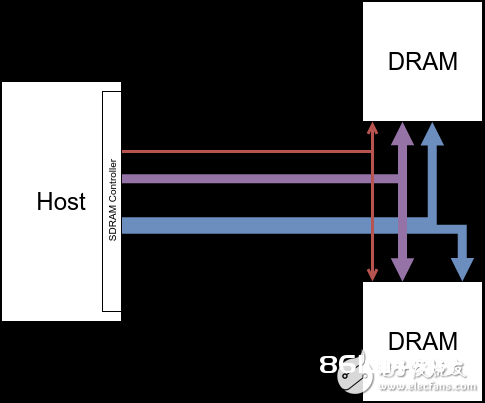

上述的这种安排方法只添加整体容量,不添加带宽。下图中描绘的安排方法则能够既添加整体容量,也添加带宽。

上图中,多个 DRAM Devices 同享操控总线和 Chip Select 信号,DRAM Controller 一同拜访每个 DRAM Devices,各个 Devices 的数据合并到一同,例如 Device 1 的数据输出到数据总线的 DATA[0:7] 信号上,Device 2 的数据输出到数据总线的 DATA[8:15] 上。这样的安排方法下,拜访 16 bits 的数据就只需求一个拜访周期就能够完结,而不需求分解为两个 8 bits 的拜访周期。

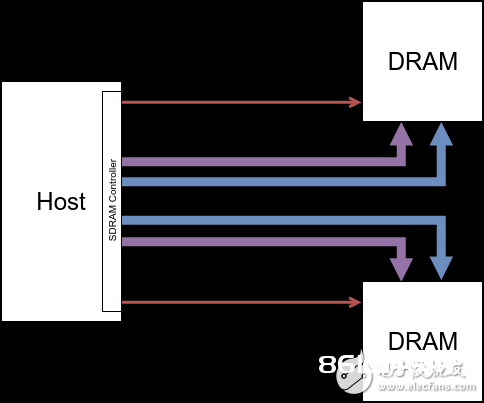

2. MulTI Channel DRAM Controller 安排方法

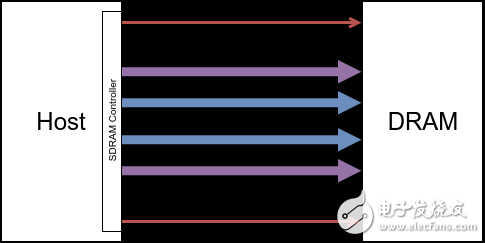

MulTI Channel 指 DRAM Controller 只要多组操控和数据总线,每一组总线能够独立拜访 DRAM Devices。 在这种场景下,DRAM Controller 与 DRAM Devices 的衔接方法如下所示:

2.1 衔接 Single Channel DRAM Devices

这种安排方法的优势在于多个 Devices 能够一同作业,DRAM Controller 能够对不同 Channel 上的 Devices 一同建议读写恳求,进步了读写恳求的吞吐率。

NOTE:CS0 和 CS1 在同一时间,能够一同处于使能状况,即同一时间,两个 Devices 能够一同被拜访。

2.2 衔接 MulTI Channel DRAM Device

在一些 DRAM 产品中,例如 LPDDR3、LPDDR4 等,引入了 MulTI Channel 的规划,即一个 DRAM Devices 中包含多个 Channel。这样就能够在单个 Device 上达到 Multi Channel 一同拜访的作用,终究带来读写恳求吞吐率的提高。