0 导言

航天器在空间中飞行时,一向处在带电粒子构成的辐射环境中。在这种辐射环境中微处理器或许会因为单粒子扰动而中止正常功用然后导致灾难性事端。这首要涉及到2方面的问题,辐射总剂量效应和单粒子效应的问题,单粒子效应又分为单粒子翻转(SEU)和单粒子闭锁(SEL)2个方面。单粒子翻转效应能够导致数字电路的存储单元中的某一位因遭到搅扰而发生翻转,然后引起存储内容的改变,还可在组合逻辑电路的输出上引进一个时刻短的脉冲,单粒子翻转效应是现在导致处理器运转失效的首要原因。星载计算机体系中处理器功用的安稳与牢靠在整个体系的安稳与牢靠性中占有重要位置,因而有必要对电路进行加固,三模冗余技能是一种对单粒子翻转有用的容错技能,能够极大地进步电路的牢靠性。

1 三模冗余介绍

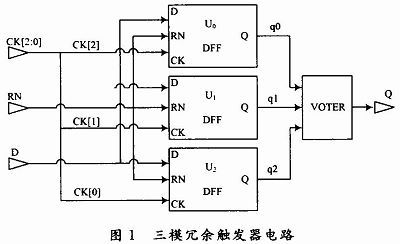

三模冗余(TMR)技能是一种时序电路加固技能,其根本思想是关于待加固模块生成2个相同的模块,再经过大都表决输出,这样即便有一个模块发生毛病电路仍然能够正常作业。三模冗余在结构上又有空间冗余和时刻冗余之分,时刻冗余便是3路时钟信号之间存在必定推迟,推迟值应大于SEU翻转的最大脉宽。时刻冗余的作用是关于时序电路的输入毛刺,最多只要一路时钟会采样到过错值,因而能够有用地避免组合逻辑毛刺所带来的过错。图1是选用一般时空三模冗余加固的触发器的电路图(今后简称TMR触发器),其间VOTER为大都表决器的组合电路。

尽管三模冗余技能能够极大地进步体系的牢靠性,可是价值也是巨大的。由TMR的根本结构不难看出选用TMR技能的2个缺陷:首要因为进行了硬件冗余导致芯片面积增大到本来的3倍多;其次因为三路时钟信号之间的推迟和在输出端参加了表决电路,在要害途径上引进了额定的延时,导致电路的运转速度下降。

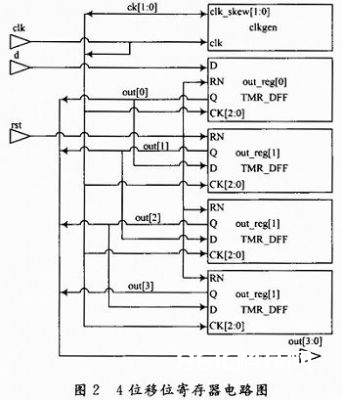

假如规划中2个触发器之间的要害途径推迟太短(比方移位寄存器),图1的三模冗余电路结构在运转中或许会呈现电路输出不定态和电路状况过错的问题,图2是一个选用三模冗余加固的4位移位寄存器的电路图,图中的TMR_DFF模块的电路如图2所示。

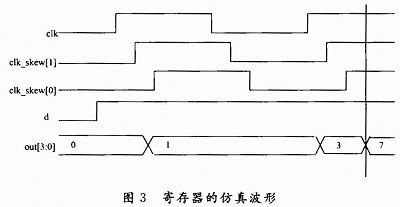

图3为三模冗余加固后的寄存器的顶层模块的仿真波形图,图中标线处电路的状况呈现了过错(由输入d能够看出正确的状况应该是在第3个时钟上升沿后输出才变为7),其原因是因为TMR_DFF是组合逻辑输出,在第1个上升沿的时分,reg0的输入D经clk,clk_skew[1]采样后,out[0]变为1,reg1的输入out[0]经clk_skew[0]采样后,其q2(图1电路中的信号)变为1,电路状况仍为1,在第二个上升沿来的时分,因为reg1的q2现已为1,所以reg2的输入out1经clk采样后,其q0变为1,大都表决后out1变为1,电路状况为3,reg2的输入out1经clk_skew[1],clk_skew[0]采样后,其q1,q2变高,输出out2变高,电路状况变为7,就呈现了状况犯错的状况。

假如减小时钟间的推迟,电路或许会呈现不定态,原因也是因为组合逻辑的提早输出,这儿就不再评论了。

2 三模冗余的完结

2.1 修正网表二次归纳

DC归纳的功用是读取规划的RTL代码而且依据时序束缚,归纳RTL代码到结构级,然后发生一个映射后的门级网表,其间一个重要的进程是指定归纳所运用的归纳库,归纳库一般由流片厂商供给,库中包含了引脚到引脚的时序,面积,引脚类型和功耗等信息,归纳后的门级网表中的单元也便是库中所界说的单元。

三模冗余的加固进程实际上便是为规划中的每个触发器生成2个冗余触发器并加上表决逻辑,而RTL代码中无法反应出这点,因而能够对原规划归纳后的门级网表进行修正,把触发器改为三模冗余触发器,用门级描绘编写三模冗余触发器模块,然后和修正的网表一同再次归纳就可得到三模冗余加固后的网表文件。值得阐明的是DC归纳库里边有多品种型的触发器,比方SDFF,EDFF,SEDFF,JK,DFF,即便在归纳脚本中限制只用DFF触发器,也会有好几种,所以关于不同的单元要编写相应的三模冗余触发器模块(其结构如图1所示)。此外因为有3路时钟信号,所以要编写时钟生成模块,其功用是由clk发生互有推迟的2路时钟信号。

首要在Synopsys的归纳东西DsignCompiler下对原规划的RTL代码进行归纳,得到电路的门级网表。门级网表中的电路实际上便是经过例化归纳库的单元来描绘电路的结构,能够运用方式验证东西Formality来验证RTL代码和归纳后的门级网表在功用上是否共同。

然后修正门级网表,在网表中添加线网类型ck[2:0],而且实例化clkgen模块,再把网表里边的触发器改为三模冗余触发器,并修正其时钟端口为{clk,ck[1:0]},因为归纳库中不含有这两个模块,这时网表中就呈现了两个归纳东西没有处理的模块,时钟生成模块和三模冗余触发器模块,修正后的网表就不是彻底映射后的门级网表。

最终对修正后的网表,时钟生成模块及三模冗余触发器模块进行再次归纳,这次归纳实际上便是对时钟生成模块和三模冗余触发器的归纳,把它们映射为归纳库中的单元,得到的门级网表便是三模冗余加固后规划的门级网表。

2.2 树立三模冗余触发器的库单元

因为三模冗余触发器单元的时钟端口有3位,即便在库中参加三模冗余触发器的单元,归纳器也无法把规划直接映射成该单元,因而能够把时钟生成模块放到TMR_DFF内部,这样三模冗余触发器时钟端口就只要1位,在库文件中把触发器单元用对应的三模冗余触发器单元替换掉,DC就能够把电路中的触发器直接映射成TMR_DFF,一次归纳就能够完结规划了,可是这样一来整个芯片的面积又会增大许多(时钟生成模块不在共用),除此之外也能够凭借上面的办法在原规划归纳后修正网表。前面现已说到库文件里边有许多品种型的触发器,所以应对不同的DFF触发器树立相应的库单元,下面是一种树立库单元的办法,首要分为2步:地图规划和仿真特性提取。

单元库的树立首要要完结单元的地图规划,在确认单元库所包含的单元品种和单元电路后,依据加工厂家的工艺参数,规划规矩等完结单元的地图规划,并导出电路网表,此刻网表中不只有电路结构,还有电阻,%&&&&&%参数。然后就能够进行单元的参数提取作业。

参数提取需求挑选一种用于参数提取的东西,这儿挑选siliconsmart,其非必须确认模仿仿真东西,如HSpice。首要进程包含创立作业目录装备仿真环境,引进参阅库,发生仿真文件,运转仿真特性提取,生成库文件。

创立作业目录是指创立一个用于siliconsmart运转的目录,此刻会主动生成一个名为config.tcl的脚本文件,需求手动对其进行一些要害装备,首要包含模仿东西的挑选(这儿挑选HSpice),模仿模型的指定,环境温度等变量的设置等。引进参阅库是为东西指定一个参阅的库单元,东西将参阅单元的信息摘取出来,并为该单元生成一个操控文件,该文件详细描绘了需求提取的单元的信息。包含单元网表文件,管脚信息,逻辑功用,输入信号的上升/下降时刻,输出管脚负载状况等。假如没有参阅的库文件,则需求手动编写该文件。发生仿真文件是告知东西对单元的哪些方面进行特性提取,比方时序,功耗,CCS模型等。运转仿真提取是对单元进行模仿仿真特性提取作业。生成库文件会发生2个库单元,其间.v是仿真东西用的仿真库,.lib是可读的归纳库,能够在DC顶用read_lib *.lib指令读入.lib文件,然后用write_ lib* *.db指令能够生成.db归纳库(*代表库单元的姓名)。

关于抗辐射加固来说,除了用电路加固外或许还需求挑选愈加牢靠的工艺,SOI工艺就具有很好的抗辐射功用,它消除了闩锁效应,有用地降低了单粒子效应,而此刻就需求树立自己的单元库了,库中的触发器单元就能够直接建成三模冗余触发器的库单元。

3 结语

航天体系中芯片的抗辐射才能是一个重要的目标,关于抗辐射的处理器和存储器来说,辐照试验是测验中的一个重要环节。三模冗余加固技能仅仅众多抗辐照加固技能的一种,比较常用的还有检错纠错码EDAC,SOI工艺加固,其间选用SOI工艺流片的费用比一般工艺更为贵重。标准单元库的树立对AS%&&&&&%规划来说是一项基础性的作业,树立契合规划需求的标准单元库对芯片规划来说是很重要的,对此文章供给了一种一般性的办法。