一般来说,用来驱动如今高分辨率类比/数码转化器的电源都是具有数百欧姆或以上的AC或DC负载。因而,一个具有有高输入阻抗(数百万欧姆)和低输出阻抗的运算放大器便成为ADC驱动器输入的最佳挑选。ADC驱动器可作为缓冲器和低通滤波器之运用,以减低体系的全体杂讯。

跟着信号在电路板的布线和冗长电缆上传送,体系杂讯会积聚在信号里,而一个差动ADC会回绝任何看来像共模电压的信号杂讯。比较起单端的信号,选用差动信号有好几个长处。首要,差动信号可将ADC的动态规模增大一倍。其次,它可供给更佳的谐波失真效能。如今有几个办法可从一个两层运算放大器装备发生出差动信号。其间一种办法是选用单端/差动转化技能,而另一种则需动用差动输入源。为了运用彻底的ADC的动态规模,ADC的输入有必要被驱动至满刻度的输入电压。

本文将会评论三种不同的ADC驱动器架构:单到单、单端到差动和差动到差动。首要意图是希望能扼要地供给全部用ADC介接高效能运算放大器的材料。

信号途径的必要组件

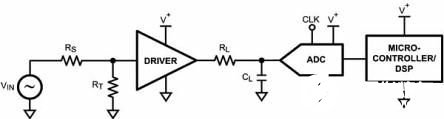

以下会把信号途径中的类比前端规划之几个组成部份一同评论。典型信号途径的类比前端包含有一个用来驱动ADC的运算放大器、一个RC滤波器、ADC和微控制器或数码信号处理器(DSP)。

图1:典型信号途径的类比前端方块图

实践国际中的输入源会带有不抱负的阻抗,因而需依靠一个很低输出阻抗的缓冲放大器来驱动ADC的输入。但是,外置的RL-CL滤波器会作用为一个抗叠频滤波器,以协助减低ADC驱动器的杂讯频宽,以及缓冲由ADC取样和坚持电路所引致的充电瞬时。为了尽量减低输入电压的跌降,外置的并排电容(CL)有必要比ADC的内置输入电容大10倍,而一起外置的串行电容(RL)亦有必要够大以固定发生在运算放大器输出的相位推迟,然后坚持电路的稳定性。关于大部份的运用而言,在运算放大器输出和ADC输入之间用一个串行阻隔电阻来衔接,都能够带来好处,因为这个串行电阻可有助约束运算放大器的输出电流,而为这个串行电阻选定数值是一项非常重要的作业。

一个比较高的电阻值将会添加运算放大器的负载阻抗,然后改进运算放大器的全体谐波失真(THD)效能。但是,ADC一般都较喜爱以一个低阻抗的源来驱动。因而,有必要为这个串行电阻找出最佳的数值,才干一同为运算放大器和ADC带来最佳的THD、SNR和SFDR效能。当把ADC衔接到一个运算放大器时,最重要是了解将会影响到效能的标准。如今的ADC标准,例如是THD、SNR、设置时刻和SFDR等,它们均对滤波、丈量、视频和重现运用很要害。高效能运算放大器的设置时刻、THD和杂讯效能有必要比被驱动的ADC的效能更好,以保证体系的准确度以及将过错减至最低或乃至消除。

在本文中, LMH6611或LMH6618单一运算放大器会被用来驱动单通道的ADC121S101 类比/数码转化器,而另一方面,LMH6612或LMH6619两层运算放大器会被用来驱动差动输入的ADC121S625或ADC121S705类比/数码转化器。这些放大器的运用规模适当广泛,特别适用于要求高速、低供电电流、低杂讯,以及需求驱动杂乱ADC和视频负载的运用。

运算放大器和ADC的重要标准

在实践中,有些体系运用会要求低THD、低SFDR和宽广动态规模(SNR),而另一些则可能要求高SNR,而且可能会献身THD和SFDR的效能来交换更佳的杂讯效能。

关于运算放大器和ADC而言,杂讯都是一项很重要的标准。这里有三个首要影响ADC全体效能的杂讯来历:量化杂讯–是由ADC自身所发生的杂讯(尤其在较高的频率下),以及由运用电路所发生的杂讯。输入源的阻抗可影响运算放大器的杂讯效能。理论上,ADC的信号与杂讯的份额(SNR)可用下列算式计算出来:

![]()

算式中的N是ADC的分辨率。例如依据这条算式,一个12位的ADC便具有74dB的SNR。但是,实践的SNR数值会大约是72dB。为取得更佳的SNR,ADC驱动器杂讯应该愈小愈好。LMH6611/LMH6612/LMH6618/LMH6619的低电压杂讯仅为10 nV/ 。

运算放大器和ADC的全体设置时刻有必要在1 LSB之内,而LMH6618/LMH6619和LMH6611/LMH6612的0.01%设置时刻别离为120ns和100ns。

此外,ADC驱动器的THD有必要低于ADC。LMH6618/LMH6619在2VPP输出和100 KHz输入频率时的SFDR为100dBc,而LMH6611/LMH6612在2VPP输出和1 MHz 输入频率时的SFDR则为90dBc。

信号/杂讯比和失真(SINAD)是一个参数,它结合了SNR和THD这两个标准。SINAD是指输出信号的RMS值与一切其它低于时钟频率一半的光谱成份之RMS值之份额,这包含谐波但不包含DC,以及可凭下列算式从SNR和THR上钩算出来:

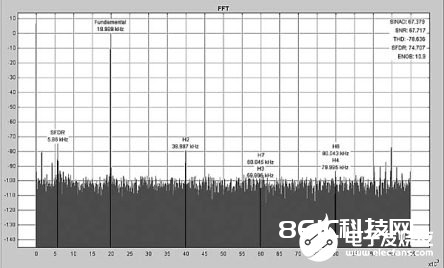

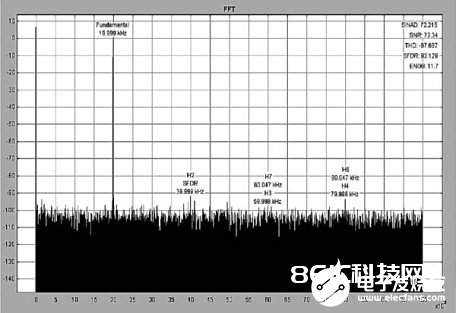

因为SINAD是将输入频率与一切不良频率成份作比较,所以它其实是ADC动态效能的一个全体性丈量。以下的部份将会具体评论三种不同的ADC驱动器架构。

1. 单到单ADC驱动器

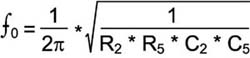

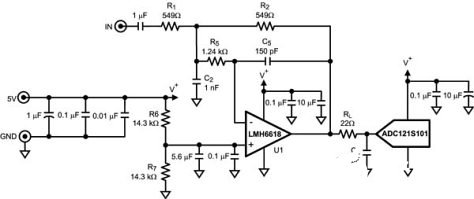

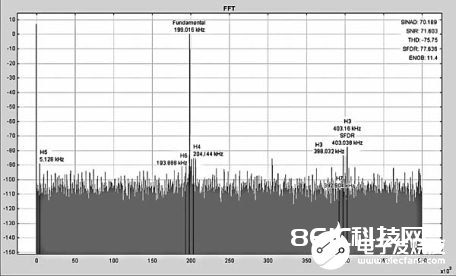

这个架构有一个单端式输入源接驳到运算放大器的输入,然后此运算放大器的单端式输出会再接驳到ADC的单端式输入。只是10 nV/ 的低杂讯和130 MHz的宽广频宽促进LMH6618成为驱动12位ADC121S101 500KSPS至1MSPS 类比/数码转化器的首选,这个ADC具有一个具有内置取样和坚持电路的逐次迫临架构(successive approximation architecture)。图2所示为一个驱动ADC121S101的LMH6618之原理图,所用的是具有有增益-1(反相)的二阶多重反应装备。图中的反相装备比起非反相的为佳,原因是反相装备可供给更多的线性输出回应。表1列出LMH6611或LMH6618与ADC121S101组合后的效能材料。图3表明出在f = 200 KHz时的LMH6611和ADC121S101组合之FET绘图。ADC驱动器的500 KHz截止频率可从下列算式计算出来:

运算放大器的增益由下列算式设定:

![]()

图2:单到单ADC驱动器

图3:单到单ADC驱动器的FET绘图

表1:LMH6611/LMH6618与ADC121S101组合后的效能

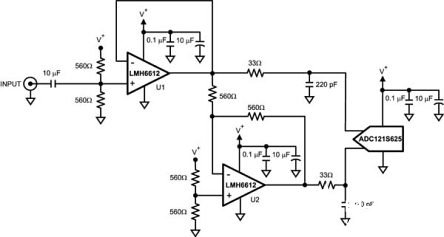

2. 单端到差动ADC驱动器

图4中的单端到差动ADC驱动器选用了LMH6612两层运算放大器来缓冲一个单端源,以便驱动一个具有有差动输入的ADC。其间一个运算放大器会被装备成一个单位增益缓冲器,并担任驱动运算放大器U2的反相(IN-)输入和ADC121S625的非反相(IN+)输入。U2把输入信号倒向并驱动ADC121S625的反相输入。U2的增益装备为+2,因而可在无需献身THD效能下减低杂讯。至于2.5V的共模电压会一起树立在两个运算放大器U1和U2的非反相输入。

当0至VREF的单端输入信号被AC耦合到运算放大器的非反相终端时,以及当每一个运算放大器的非反相终端在中标量2.5V下被偏压时,这种装备便可发生2.5Vpp的差动输出信号。此外,两个输出RC抗叠频滤波器会一起运用在U1和U2的输出与ADC121S625的输入之间,以减轻来自输入源的不良高频杂讯之影响。每一个RC滤波器均具有有约22 MHz.的截止频率。图5表明出在f = 20 KHz时LMH6612和ADC121S625组合的FET绘图。

图4:单端到差动ADC驱动器

图5:单端到差动ADC驱动器的FET绘图

表2:LMH6612/LMH6619与ADC121S625两个组合的效能材料

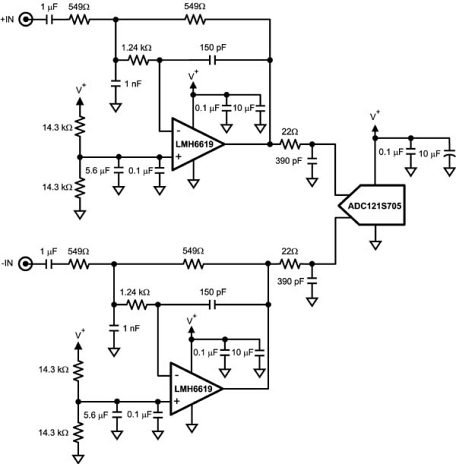

3. 差动到差动ADC驱动器

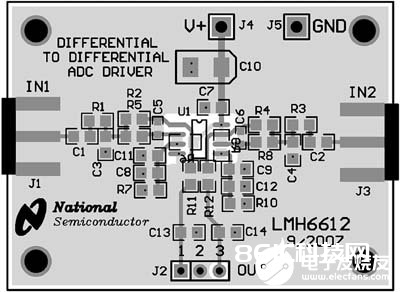

LMH6619两层运算放大器能够被装备成一个差动到差动的ADC驱动器,以便用来将一个差动源缓冲到一个差动输入ADC,正如图6所示。该差动到差动ADC驱动器可用两个单到单ADC驱动器组成。这些驱动器的每一个输出会接驳到差动ADC的单个输入。在这里每一个单到单ADC驱动器都选用相同的组件,而且装备成增益-1(反相)。

图6:差动到差动ADC驱动器

下表别离总结出LMH6612和LMH6619与ADC121S625和ADC121S705这四个组合的效能。表中一起包含有LMH6612和LMH6619别离在2个不同的频率下衔接到两个ADC的材料。为了竭尽ADC的整个动态规模,25VPP的最高输入会施加到ADC的输入。图7表明出在f = 20 KHz时LMH6612和ADC121S625组合的FET绘图。

表3:LMH6612和LMH6619别离衔接到ADC121S625和ADC121S70后的效能

图7:差动到差动 ADC驱动器的FET绘图

接地和电路板布局考虑

将输入源接地衔接到电源接地是非常重要的。关于上述每一个的ADC驱动器装备,当树立电阻器网络以保证差动输出具有相同增益时,有必要一起考虑信号源的阻抗。例如,一个音频准确信号发生器具有22Ω的源阻抗,而电路板则有一个50Ω的终端,因而规划人员有必要调理增益和输入,以便能在运算放大器的输出处获取所需的信号。

为了取得最佳的高频效能,以下是一些电路板布局的主张:

·将ADC和放大器放置得愈挨近愈好

·将供电旁路电容器尽量放近设备(间隔少于1英寸)

·选用外表黏着而非穿孔式组件,以及选用接地和电源层

·尽量削减布线的长度

·为冗长布线选用终端式传输线

图8:差动到差动ADC驱动器的电路板布局

LMH6612/LMH6619只耗费仅6.5mA/2.5Ma的电流,比较起市面上大部份的全差动放大器少了超越20mA。选用LMH6611/LMH6612/LMH6618/LMH6619的首要长处是低功率和低成本。傍边,LMH6611和LMH6612最适合运用在那些在奈奎斯特(Nyquist)频率20 KHz至2 MHz下运转的运用,而LMH6618和LMH6619则最适合运用在那些在奈奎斯特频率20 KHz至500 MHz下运转的运用。

总括而言,本文涵盖了一切重要的考虑要素,包含外置RL-CL网络的挑选以及运算放大器的要害参数:象是THD、设置时刻和杂讯,这些都是在把高效能运算放大器衔接到ADC时一切必要考虑的参数。此外,本文还具体评论了三种不同的ADC驱动器装备,而且在实验室进行了谨慎的测验。最终,本文亦论及接地和电路板布局时需求留意的当地,然后改进体系的效能。

责任编辑:gt