摘要:针对传统CMOS带隙电压基准源电路电源电压较高,基准电压输出规模有限等问题,经过添加发动电路,并选用共源共栅结构的PTAT电流产生电路,规划了一种高精度、低温漂、与电源无关的具有安稳电压输出特性的带隙电压源。根据0.5μm高压BiCMOS工艺对电路进行了仿真,成果表明,在-40%℃~85℃规模内,该带隙基准电路的温度系数为7ppm/℃,室温下的带隙基准电压为1.215 V。

基准电压源广泛应用于A/D、D/A转换器、开关电源以及各种通讯电路,它的电源噪声按捺才干与安稳的温度特性是影响A/D,D/A速度与精度的重要因素,乃至影响整个体系的功能,杰出的基准电压源规划才干满足需求。带隙电压基准(BGR)技能日趋老练,具有较高精度,较低功耗的BGR在电路中被广泛应用。

使用双极型晶体管的基区-发射区电压差△VBE在不同电流密度偏置下具有正温度系数,而其自身的基区-发射区电压VBE具有负温度系数,这两个电压线性叠加,得到较适宜的近似零温度系数的基准电压源。该带隙基准电压源电路添加了发动电路和PTAT电流产生电路,其间PTAT电流产生电路是该基准源的中心,经过对电路的剖析与研讨,给出了根据0.5μm高压BiCMOS工艺下的带隙基准电压源的规划和仿真成果。

1 传统的带隙电压基准源

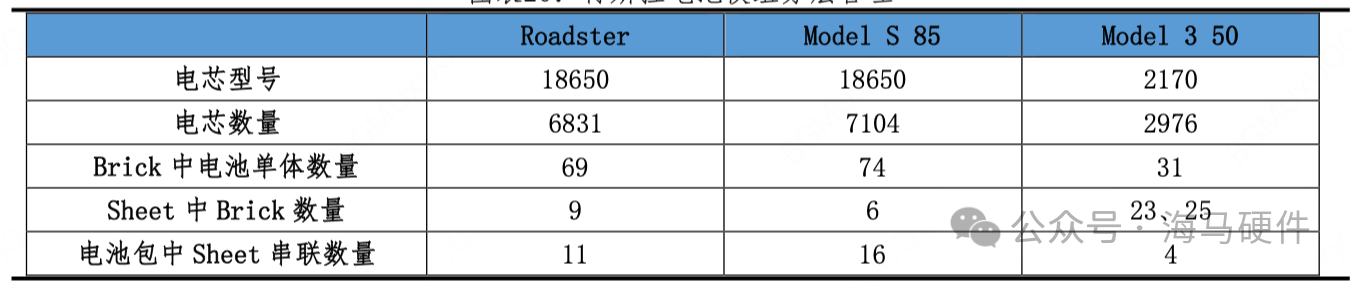

传统的带隙电压基准源原理图与电路结构如图1所示。

图1(a)中,以VBE(on)和VT为基准的偏置源会有相反的TCF,输出电流或许以VBE(on)和VT的某种复合电压作为基准源,假如复合方法妥当,可使输出温度系数为零,该电路输出电压为:

VOUT=VBE(on)+MVT (1)

经过确认VBE(on)的温度系数,使输出电压与温度无关,即然后确认要求的M值。

关于图1(b),已知两个双极晶体管作业在不持平的电流密度下,它们的基极-发射极电压的差值与绝对温度成正比。在图1中,假如MP1,MP2是相同的晶体管(IS1=IS2),且偏置的集电极电流别离为nI0和I0,疏忽它们的基极电流,那么

△VBE=VBE1-VBE2=VTlnIo/Is1-VTlnIo/IS2=VTlnn (3)

双极晶体管的偏置电流实际上是与绝对温度成正比(PTAT)的,假定MP1与MP2为相同的管子,要使ID1=ID2,电路有必要确保VX=VY。所以,ID1=ID2=(VTlnn)/R,成果,使ID3产生相同的特性,并将PTAT电压ID3R2加到基极-发射极电压上,因而输出电压为

只需确保(4)式中两项和是零,VBE3的值以及Q3尺度的挑选都有几分恣意。实际上,由于晶体管之间的不匹配,以及R1的温度系数,ID5的改变会违背抱负的等式,给输出电压Vref带来差错。传统电路还存在电源电压较高,基准电压输出规模有限等问题,因而需求不断的改进与进步。

2 带隙基准电压源电路规划

根据0.5μm高压BiCMOS工艺下的带隙基准电压源电路如图2所示,电路由发动电路和带隙基准电压产生电路两大部分组成。

在与电源无关的偏置电路中,重要的问题是“简并”偏置点的存在,使电路有两种或许的状况:一种是作业状况,另一种是电路中没有电流流过,这是所不期望的状况。添加发动电路,使该电路在电源上电时,能唆使电路脱节简并偏置点,正常发动并安稳作业。图2中左半部分即为该带隙基准电压源的发动电路部分,主要由R1、R2、MP1、HAP1和HAP2构成,其间HAP1与HAP2为高压非对称PMOS管,HAP1与HAP2构成电流镜,由于两者尺度相同,HAP2的漏极电流与HAP1的漏极电流持平。当电路未进入作业状况时,HAP1与HAP2导通处于敞开状况,经过添加VDD端电压,使得R1上压降逐步增大,因而经过R1的电流添加;由于HAP1与HAP2构成的电流镜的效果,经过R2的电流与R1上的电流相同,所以R2上电流也跟着VDD端电压上升而升高,R2两头的电压也随之升高;当VDD添加到必定程度后,R1远离地端的电势将逐步升高到该工艺下高压非对称PMOS管的截止电压,并保持安稳,此刻R1上的电流也趋于安稳,R2上电流也将趋于安稳,在R2远离HAP2端将得到一个较安稳的敞开电压,经核算并仿真测得这个电压为5.92 V。

关于电压产生电路,PTAT电流产生电路是该电路的中心部分,应用了BCD工艺下的PNP管。主要由MP2、MP3、HSP3、HSP4、HSN1、HSN2、MN1、MN2、R3、Q1、Q2构成。其间MP2、MP3、HSP3、HSP4、HSN1、HSN2、MN1、MN2、R3构成与电源无关的偏置,Q1、Q2产生与温度无关的基准。

在偏置电流电路中,IREF经过某种方法由Iout得到,假如Iout终究与VDD无关,那么IREF则不受VDD影响,即与电源无关。当疏忽MOS管沟道长度调制效应时,有Iout=KIREF,由于每个以二极管方法衔接的器材都是由电流源驱动的,所以IREF近似的与电源无关。图2中MP3、HSP4 HSN2、MN2的宽长比别离是MP2、HSP3、HSN1、MN1的二倍,其间MP2、MP3、HSP3、HSP4与HSN1、HSN2、MN1、MN2别离构成共源共栅电流镜,生成与电源无关的电流偏置,影响电流精度的关键因素便是漏-源电压,漏-源电压的改变会严重影响漏极电流的匹配。关于一般电流镜电路,因它们的漏一源电压不同,然后失配与沟道调制效应会形成组成电流镜的两个晶体管的栅-源电压有差异,然后导致输出电流产生很大改变。选用共源共栅电流源结构的电路,长处在于它会有一个很大的输出电阻,这在镜像电流源中非常重要,可以进步输出基准电压的安稳性,此外该结构可以减小沟道调制效应的影响,可以改进电源按捺和初始精度等电路的重要功能。图2中经过MP4,与HSP5最终从HSN3中流出的电流和VT有关,所以电阻R4的压降也与VT有关,在做仿真的过程中,经过对R4的阻值优化,最终挑选适宜的电阻值使VOUT输出带隙电压。