导言

在电工技能范畴内,频率是一个最根本的参数,频率与其他许多电参量的丈量计划、丈量成果都有非常亲近的联系。跟着航天军事科学技能的开展,对时刻及频率的丈量精度有了更高的要求。可是在现有依据单片机、CPLD等的测频设备中,在高频率的作业条件下作业不行安稳,电路板的规划比较困难,丈量精度达不到体系要求的数量级。因而,研讨丈量精度更高的丈量设备具有重大意义。

PSoC(Programmable System on Chip)是Cypress公司推出的一款依据通用IP模块,而且具有真实混合信号处理才能的可编程片上体系芯片。在PSoC芯片的规划中,规划者能够依据不同规划要求调用不同的数字和模仿模块,完结芯片内部的功用规划。运用一块芯片就能够装备成具有多种不同外围元器材的微操控器,以完成从确认体系功用开端,到软硬件区分,并完结规划的整个进程。因而,PSoC能够满意非常复杂的实时操控需求,运用它进行产品开发能够大大进步开发功率,下降体系开发的复杂性和费用,一起增强体系的可靠性和抗干扰才能。因而,PSoC特别适用于各种操控和主动化范畴。

1 丈量原理

频率丈量主要有测频法和测周法两种。测频法就是在确认的闸口时刻Tw内,记载被测信号的改变周期数(或脉冲个数)Nx,则被测信号的频率为fx=Nx/Tw。测周法需求有规范频率的信号fs,在待测信号的一个周期Tx内,记载规范频率信号的周期数Ns,则被测信号的频率为fx=fs/Ns;在多个周期内,记载被测频率的改变周期数(或脉冲个数)Nx,则被测频率为fx=fs×Nx/Ns。这两种办法的计数值会发生±1个脉冲差错,而且测验精度与计数器中记载的数值Nx或Ns有关。

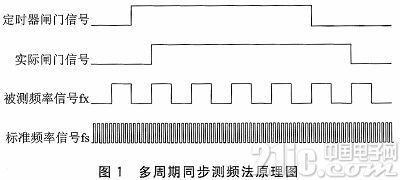

本规划选用多周期同步测频法:首要经过对定时器的设定来预置闸口时刻。将规范频率信号和被测频率信号别离输入两个计数器进行多个周期的同步计数。预置闸口时刻完毕时,两个计数器并不中止计数,而是比及被测频率信号下一个同相位触发沿到来之后才封闭同步门并中止计数。因而,丈量成果的精度仅与闸口时刻和规范频率有关,差错由被测频率的±1个脉冲削减到规范频率信号的±1个脉冲,丈量精度有明显进步。多周期同步测频法原理图如图1所示。

2 体系规划

2.1 硬件规划

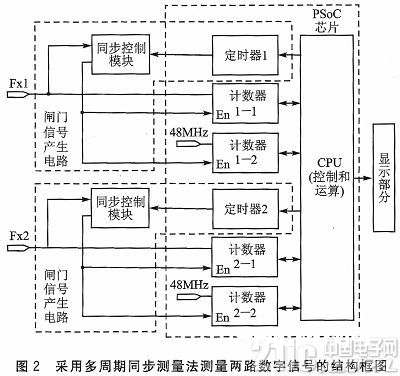

由原理剖析可知,选用多周期同步测频法丈量单路信号频率时,至少需求一个能供给闸口信号的定时器,一个操控实践闸口信号在被测信号上升沿处启停的同步操控模块,以及两个别离对实践闸口内的被测频率信号和规范频率信号进行计数的计数器。由运算器对计数器的成果进行运算,求出被测频率值,终究经过显现模块显现丈量成果。

在两路信号频率丈量中,不同信号的闸口信号发生电路和计数器都是互相独立的,但其操控运算部分都由CPU来完结。依据对PsoC内部资源上的考虑,本规划选用1片PSoC芯片CY8C29666作为频率丈量体系的主体部分,每个PsoC芯片内部至少需求装备2个定时器功用模块和4个计数器功用模块。各计数器的计数成果输入到CPU中进行核算,得到的被测信号频率值并输出到显现部分。

PSoC芯片是整个频率丈量体系的中心,其装备办法的可行性和合理性直接联系到体系功用能否顺利完成。本规划中运用PSoC Designer软件中的器材编辑器对CY8C29666内部的大局资源、用户模块、衔接联系以及芯片引脚进行装备,在此根底上增加外部器材,即可完结体系的硬件渠道的建立。本规划中,两路信号对应的处理部分将体系资源一分为二,即定时器模块均为8位,两个被测频率计数器均为16位,两个规范频率计数器均为32位。

定时器的装备办法是要害的环节。定时器模块是由1个周期寄存器、1个同步递减计数器和1个捕获比较寄存器组成。周期寄存器和捕获比较寄存器中要别离寄存两个值,即Period和CompareValue,这两项值决议着闸口时刻的长短。定时器模块共有两项输出:比较输出和终究计数输出。其间比较输出连到同步操控模块,用于发生同步使能信号;终究计数输出端接到指定的GPIO引脚,用来判别何时读取计数器的计数值及重写计数器的初值。

敞开定时器后,递减计数器由Period值开端递减,一起两个输出端均输出低电平。当计数值等于Compare Value时,鄙人一个体系时钟上升沿,比较输出端输出高电平,直至计数值递减到零时,比较输出跳低——这样就发生了定闸口信号。定闸口信号进入同步操控模块,发生与被测信号上升沿同步的使能信号。两个计数器在使能信号为高时开端递减计数。当使能信号跳低后,计数器暂停计数。读取当时计数值,即可核算出丈量成果。体系结构框图如图2所示。

2.2 软件规划

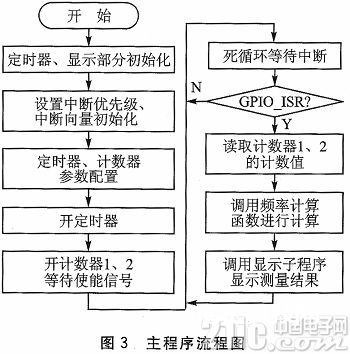

该体系的程序规划主要由主程序、中止服务子程序和显现子程序构成。为了使规划出来的软件功用清晰,便于调试、扩展和移植,选用结构化的程序规划办法。主程序如图3所示。

需求留意的是,定时器终究计数完毕后的下一个体系时钟周期,定时器会主动从头加载计数初值,所以要在此之前读取两计数器的计数值。故运用定时器的终究计数输出功用,在此刻输出一个脉冲触发中止,即可经过编写中止处理程序完成读取计数值,并重置计数器初值的功用。

3 试验成果及差错剖析

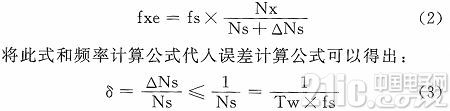

设规范信号的频率为fs,经过装备定时器模块得到的闸口时刻为T,被测信号频率的理论值为fxe,T时刻内计数器对被测频率信号和基准频率信号的计数值别离为Nx和Ns,则被测信号的频率为fx=fs×Nx/Ns。在疏忽基准频率fs差错的状况下,测频或许发生的差错为:

δ=[(fxe-fx)/fxe]×100% (1)

因为丈量中两计数器的计数启停都由fx的上升沿触发,即实践闸口时刻为被测频率信号的整数倍,故对fx计数不存在差错;对fs的计数Ns最多相差一个脉冲的差错,即|△ Ns| ≤1,此刻丈量频率为:

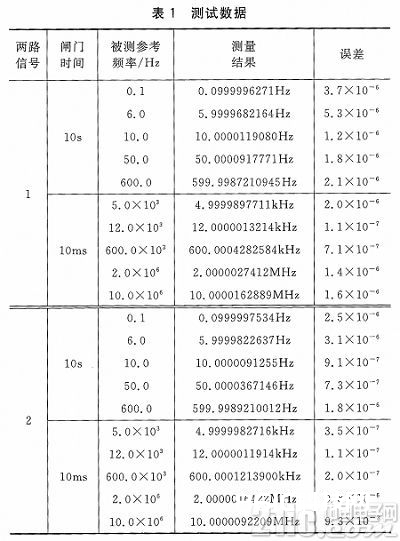

由式(3)能够看出,丈量频率的相对差错与被测信号频率的巨细无关,仅与闸口时刻和基准信号频率有关。闸口时刻越长,规范频率越高,测频的相对差错就越小。这儿选定规范信号频率为48 MHz,闸口时刻别离为10 s和10 ms的状况。经过核算可知:闸口时刻为10 s时,理论差错为2.083×10-9;闸口时刻为10 ms时,理论差错为2.083×10-8。体系电路装置调试成功后,对上述成果进行验证。两路输入信号别离取自绿杨牌YB1631信号发生器以及信达牌XD11BH多用信号发生器。被测信号参阅频率由Keithley 2000数字万用表测得。丈量成果如表1所列。

由表1可知,本规划丈量成果的相对精度在10-6以上,根本到达规划精度要求,可是与理论差错比较还有必定距离。原因有两方面:一方面在现有的试验室条件下,没有频率精度更高的频率计,故以其为规范核算得到的差错只能作为参阅,更高的丈量精度无法验证;另一方面是体系自身存在差错。

结语

本体系以PSoC芯片CY8C29666为中心,以多周期同步测频法为根底,充分利用了PSoC芯片内部集成的功用模块资源,完结了两路信号频率丈量体系的规划。其硬件电路简略,进步了频率丈量的精度,完成了高集成度、高速和高可靠性。一起,因为PSoC器材的体积和功用优势,简化了体系的规划,进一步下降了本钱。