作者 / 陈靖 丁蕾 王立春 上海航天电子技能研讨所(上海 201109)

摘要:芯片叠层封装是一种三维封装技能,不光能够进步封装功率、产品集成度和器材运转速度,且能够将可编程逻辑门阵列器材与处理器、存储芯片、数模转换器材等一同封装,完结器材的多功用化和体系化。以航天小型化核算机为例,剖析了芯片叠层型体系封装规划中存在的典型问题。结合可编程逻辑门阵列器材的I/O可界说和叠层封装结构特色,提出了一种依据氮化铝衬底资料的BCB/Cu薄膜多层转接板完结芯片间高密度互连和电磁屏蔽优化新办法,并完结小型化核算机体系级封装模块研发。

*基金项目:“十二五”国防先进制作项目(编号:51318070109)

陈靖(1984-),男,硕士,研讨方向:体系级封装(SiP)技能和多芯片封装技能。

0 导言

跟着航天小型化核算机向小型化、高功用、高牢靠等方向开展,迫切要求对体系进行集成。一般来说,在产品外形尺度相同的前提下,使产品具有更强壮的功用,可借助于芯片叠层封装技能[1-2]。可是在进行封装规划时,典型的芯片叠层结构(金字塔型或悬梁式)并不一定都能够完结。关于规范外形尺度或空间有限的航天电子产品而言,往往会导致其实践封装规划缺少工艺可行性。文中以航天小型化核算机为方针,提出了一种依据高导热氮化铝(AlN)衬底资料的BCB/Cu薄膜多层转接板完结芯片间高密度互连和电磁屏蔽优化新办法,与现在TSV(Through Silicon Vias)硅转接板比较,选用TCV(Through Ceramic Vias)技能制备转接板,不只能够完结2.5D微体系高牢靠集成,而且具有陶瓷介电常数高、绝缘性好、热导率高,而且低成本、制作工艺简略等优势。

1 芯片叠层型体系级封装互连首要问题

国产小型化核算机SiP产品中首要有FPGA、 DSP、CPU、SRAM、FLASH、AD、DA等芯片,产品进行封装集成时,常常面对包含封装内逻辑联系杂乱、互连密度过高和引线键合才干约束等要素导致了叠层封装难以完结或直接影响产品功用。

1.1 逻辑联系杂乱

比较贮存类产品,航天核算机产品的对外接口多、功用多样,触及多种类型的芯片进行封装集成,使得电路规划更为杂乱。在实践封装规划时,需求依据芯片物理尺度树立芯片叠层模型,这些芯片间的逻辑联系往往是比较杂乱的。为了完结这些互连联系,一般需求将芯片的电极互连到基板上,然后在基板内进行多层布线,完结电气衔接。而抱负的封装规划方针是芯片与芯片之间进行直接互连(Die To Die),这样才干更大极限地削减信号传输的推迟和削减各种寄生参数[3~4]。而往往这种方针并不简单完结,芯片间直接互连会遭到芯片的电极散布方位和功用界说的约束。

1.2 互连密度过高

所用到的集成电路芯片规划和集成度成倍进步。例如,前期的FPGA规划只要几千门,近几年多家单位推出500万门以上FPGA,芯片电极(I/O)的间隔随特征尺度缩小而微缩。从集成电路250 nm节点的72 μm电极间隔缩小至45 nm节点的48 μm电极间隔,这些均对封装互连工艺和牢靠性带来应战。当FPGA与CPU或DSP芯片等超大规划集成电路进行叠层时,上基层的芯片均为细间隔的电极散布,导致芯片在同方向上的引线键合密度过高。现在,细间隔引线键合技能和金丝资料制作工艺日益老练,使得封装内多层引线布线才干和互连密度大幅进步。可是过高的互连密度,易呈现引线短路(特别在随机振动条件下),下降产品的牢靠性。

1.3 引线键合才干约束

传统的引线键合技能在小型化、三维封装开展趋势的推进下,呈现了低弧度键合、叠层键合、引线上芯片键合、外悬芯片键合、双面键合等新技能[5-6]。可是,这些键合技能一起的难点是无法进行长间隔的键合,即遭到跨距的约束。在叠层计划规划中,往往呈现底层芯片相关于上层芯片(如FLASH芯片)的外形尺度差异过大,致使从上层芯片的电极键合到基板或基层芯片焊盘上的引线过长。引线跨距增大不只会使引线拉力强度下降,还可能会发生引线摇摆(Wire Sway)、陷落(Wire Sagging)等缺点。

1.4 三维混合芯片近场耦合

航天小型化核算机归于数模混合信号体系,数字电路快速开关引起的瞬态开关噪声可经过封装基板或互连引线影响灵敏电路正常作业,一起噪声源芯片和灵敏芯片之间因为三维堆叠而构成近场空间耦合[7~8]。关于混合信号体系,特别是高灵敏度产品的体系集成,噪声源和灵敏源间隔比2D封装更近,封装体内部的近场耦合会严重影响信道的传输质量,引起高速集成电路信号失真、作业失效。除了混合体系封装,高速数字电路体系的速率越来越高,叠层芯片间的空间电磁耦合对数字途径高频重量影响也会越来越大,例如高速AD/DA芯片与FPGA芯片的叠层。

2 芯片叠层型体系级封装互连优化

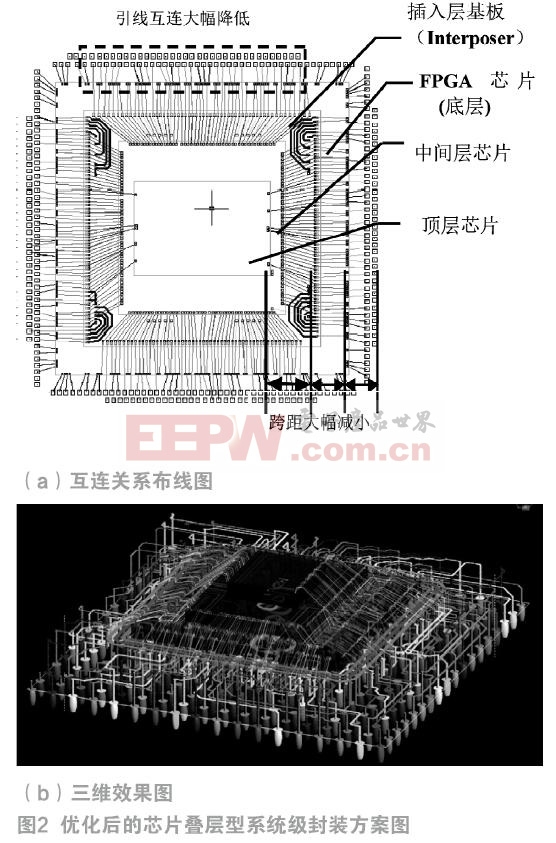

为处理芯片叠层中封装规划与施行难点,可从以下三方面进行封装互连计划的优化,典型的带多层转接板的芯片叠层优化结构如图1所示。

1) 原理图-封装互连协同规划。运用FPGA芯片可编程I/O特色,优先考虑FPGA与其它功用芯片的互连方位(就近互连准则),封装规划完结后在原理图中进行逆向规划(反标);

2) 选用苯并环丁烯(BCB)作为转接板高功用的高频介质资料具有更好的平整化才干、更低的吸水率、更小的介电常数和介质损耗。转接板顶层导体构成RDL(Redistribution Layer)再散布层,完结转接板之上的芯片与其他芯片或基板互连,减小了芯片引线长度,下降了信号链路的寄生电感;

3) 选用TCV陶瓷穿孔技能,将转接板中间层与底层导体互连,构成特别电磁场带(Electromagnetic Band Gap, EBG)以及接地屏蔽结构,构成灵敏芯片的电磁维护。

优化后芯片叠层间的互连计划如图2(a)所示,因为FPGA的可修改I/O未作详细界说,图中封装内的互连网络杂乱程度大大下降。这种状况下,芯片与芯片之间的直接互连成为可能;转接板上运用BCB/Cu薄膜多层互连工艺。经过RDL层,不光可完结焊盘方位的再散布,大幅下降了封装内的引线互连密度和互连杂乱程度,处理了引线互连跨距的约束,并可对灵敏芯片构成电磁维护,然后进步封装功率和集成度。终究完结的叠层封装三维作用如图2(b)所示。

3 芯片叠层结构应力评价

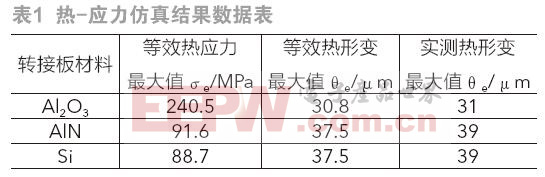

在芯片叠层封装规划中,芯片与转接板之间膨胀系数(CTE)存在差异,热一应力会构成芯片外表钝化层损害,直接影响叠层结构的牢靠性。一起,挑选较高导热的资料会有助于叠层结构的导热功用。表1为220 ℃环境下得到典型芯片叠层的等效热应力和等效热形变仿真和测验成果。

剖析可知,跟着转接板与芯片的膨胀系数差异增大,芯片层间的等效应力和等效形变随之添加。选用Akrometrix公司TherMoire设备的Shadow Morie法丈量转接板变形状况,运用AlN资料作为转接板的等效热形变最大值为39 μm,等效热应力最大值为91.6 MPa,资料热功用与Si相似。挑选挨近Si资料功用的AlN衬底能够满意芯片叠层结构的热牢靠性。

依据芯片叠层体系级封装规划优化办法,研发的一款航天小型化核算机什物如下图4。该模块包含了CPU、DSP、FPGA、 SRAM×4、FLASH、AD和DA等多芯片器材,用于完结核算与操控一体化集成。终究的模块尺度仅为40 mm×40 mm×9 mm,并经过GJB2438 H级的挑选查核要求。

4 定论

本文结合FPGA芯片可编程I/O的功用和叠层封装结构的特色,提出了一种依据高导热氮化铝(AlN)衬底资料的BCB/Cu薄膜多层转接板完结芯片间高密度互连和电磁屏蔽优化新办法,并成功应用于某款航天小型化核算机研发中。该优化办法有用处理芯片叠层封装中引线互连密度过大、长间隔引线键合、电极散布不规则、数模芯片的电磁屏蔽等问题,有用地进步了芯片叠层封装的牢靠性。一起,该办法处理了现在体系级封装(SiP)中芯片往往并非依据封装而定制的不匹配问题,该办法不只适用于FPGA芯片的叠层封装,关于其它超大规划%&&&&&%芯片如AS%&&&&&%、SoC等相同有参阅含义。

参阅文献:

[1]Rao R.Tummala, Madhavan Swaminathan, et al. Iintroduction to system-on-package(SOP) Miniaturization of the Entire System[M].McGraw-Hill Education, 2014,9-13.

[2]哈珀.电子封装与互连手册[M].北京:电子工业出版社,2009.

[3]CARSON F P, KIM Y C, YOON I S. 3D stacked package technology and trends [J].Proc of the IEEE, 2009, 97(1):31-38.

[4]E. Beyne, "3D system integration technologies," in VLSI Technology, Systems, and Applications [J], 2006 International Symposium on, 2006, 1-9.

[5]Leonard W. Schaper, 3D-SiP: the Latest Miniaturization Technology [J], IEEE, 2008.

[6]GOH K S, ZHONG Z W. Investigation of ultrasonic vibrations of wire-bonding capillaries [J]. Microelec-tronics, 2006, 37(2): 107-113.

[7]Package and Chip-Level EMI/EMC Structure Design, Modeling and Simulation. E. Diaz-Alvarez,J.P. Krusius[C]. 1999 Electronic Components and Technology Conference .1999.

[8]Lap Wai Leung et al. Stacked multi-chip package with EMI shielding[P]. US 20080067656A1

本文来源于《电子产品世界》2018年第4期第38页,欢迎您写论文时引证,并注明出处。