根据机器视觉的智能方针检测体系使用十分广泛,尤其在航天军工等领域中,常常触及高速方针的实时检测和操控,对方针检测的智能性和实时性提出了更严厉的要求。在这种使用中,视觉体系相对雷达、声纳具有信息量大、抗干扰能力强、软件处理灵敏、体积重量小、本钱低一级特色,但缺陷是传输和处理需求的时刻更多,因而很难满意图画信息传输和处理的实时性要求。

高速相机一般经过GigE、CameraLink、USB3.0等接口将图画收集后传输到图画处理器上,这种办法把许多时刻耗费到信息传输通道。为了处理这个问题,最好的办法是直接在近端对传感器芯片收集的图画进行处理。FPGA凭仗其硬件并行运算的优势,越来越多地使用于高速相机以及高速运动检测体系中,极大地进步了图画处理速度,确保了体系的高速、实时性与精确性。经过FPGA对图画传感器进行近端处理,能够做到收集图画与智能处理同步进行。其最需求处理的问题是优化智能算法,使得运算愈加简略高效,并占用更少的资源。

现在许多学者正致力于高速视觉方针检测体系的研讨。GUQY等人规划了2000f/s的高速智能相机,能够对方针进行智能实时监测。后又规划了高帧频视频拼接体系,该体系运用了改善的根据特征的视频拼接算法,能够实时组成全景图画,帧率可达500f/s。麻省理工大学的CHENJG等人经过高速摄像机(5000f/s)对悬臂梁上的方针物体进行位移丈量试验,经过PC对数据进行离线剖析,得到了与激光测振仪和加速度计丈量相共同的振荡曲线。而且经过FFT算法对三组数据进行频域剖析,得出了各个共振频率重量。

本文以高帧频与实时性作为研讨的切入点,规划了一种根据ZYNQ7000的高速相机渠道,充分利用芯片上的FPGA资源及其硬件并行的优势,进行方针提取及质心检测算法的完结。本文优化了方针检测的FPGA算法,去掉中心缓存环节,以流水线结构对图画数据进行实时流水处理,进步了方针检测算法的处理功率,能够在每帧图画收集后的有限个时钟周期内完结方位检测运算,做到同步检测。试验成果表明,该体系能够完结560×480分辨率、1100f/s、3像素精度的实时方针检测。

1硬件体系规划

1.1体系组成

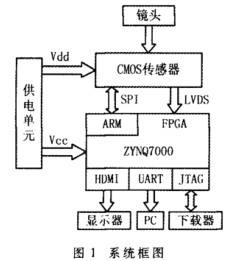

为了到达高速实时的要求,本体系选用FPGA直接驱动高速CMOS传感器的办法,完结近端处理。该检测体系首要由FPGA主控单元、CMOS图画收集单元、多电源轨供电单元、对外接口单元和光学成像单元几部分构成,如图1所示。

FPGA主控单元选用ZYNQ7020芯片,片上集成ARM硬核和FPGA资源,ARM担任对CMOS传感器进行装备,FPGA对获取图画进行数据处理、方针检测算法完结、输出图画及方位信息。

CMOS图画收集单元选用Python300型灰度CMOS传感器,该传感器分辨率为640×480,能够到达815f/s的全分辨率输出,并可经过开窗(ROI)操作进一步进步帧频。

对外接口单元包含HDMI显现接口、串口、JTAG接口等电路,完结图画显现、方位坐标传输和调试下载等功用。

1.2硬件规划

该体系硬件电路规划为两部分:FPGA主控板和高速底板,二者经过规范化的高速连接器进行互联和信号传输。主控板选用制品高速FPGA中心板,底板则选用4层PCB板规划,整合了CMOS电路、HDMI显现电路、电源电路、串口电路等。

底板规划首要是对上述各部分电路进行合理布局布线。其间,因为CMOS传感器输出的是低压差分信号(LowVoltageDifferenTIalSignal,LVDS),每路数据速率能够到达720Mb/s,规划时有必要考虑信号完好性。

布线时对该信号进行了特别的处理,严厉遵从高速差分线的规矩:每对差分线平行布线,尽可能坚持相同的最小间隔,且小于线宽;削减过孔次数;布线角落大于90°;差分阻抗操控在100Ω,与差分信号接纳端的100Ω端接电阻相匹配,削减信号的反射;每组差分线布线长度尽可能坚持共同;各组差分线之间坚持较大间隔。

经过以上办法,确保高速差分信号的信号完好性,以及各组信号较小的推迟差。

2软件体系规划

软件规划首要完结使能操控和寄存器装备两种功用。使能操控经过ARM处理器的IO操作操控CMOS的时钟、供电;寄存器装备是ARM经过SPI总线IP核与CMOS传感器进行通讯,对一些必要的寄存器进行装备,首要包含窗口巨细、图画深度、运转形式、图画数据输出等。

经过装备CMOS内部寄存器,使CMOS传感器输出8bit深度、560×480分辨率、大于1000f/s的高速视频流图画,经LVDS接口传输至FPGA进行数据处理及算法完结。

3信号处理及检测算法FPGA完结

3.1方针检测原理

3.1.1方针提取

进行方针检测,首要需求将图画中的方针与布景区别并提取出来。结合使用场景,本体系选用布景差分法加阈值切割的办法对方针进行提取。

首要获取明晰安稳的布景图画,然后将当时帧图画与布景图画对应像素值做差,完结差分运算。接着将差值与设定阈值进行比较,若大于阈值,则判定为1,即运动远景;反之为0,即布景,生成二值化图画。

3.1.2质心检测

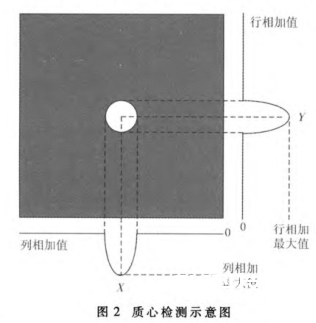

本体系所要检测的方针为一球体,进行阈值切割之后的二值化图画中,方针表现为一个圆形亮斑。考虑到方针的特别性,一起合作FPGA流水线结构的特色,本文经过圆直径检测的办法,找出X方向和Y方向上直径地点直线的交叉点,然后确认圆心地点方位。

具体办法如图2所示:将二值化图画每行的像素灰度值相加,相加之和两两比较,在直径地点的行上将会发生一个最大值,该最大值所对应的行数即视为圆心的Y坐标。列方向进步行相同操作也可得到X坐标。

圆直径检测核算圆心的办法合作FPGA流水线结构,在读取图画的一起进行处理宽和算,能够最大程度削减检测推迟,进步实时性。

3.2FPGA逻辑规划

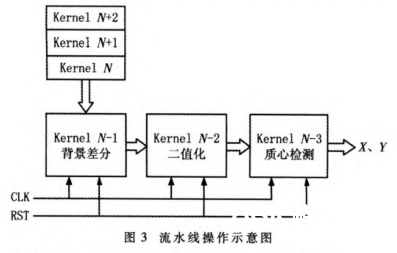

CMOS传感器图画数据的传输依照自左向右、自下而上逐行进行,每8个像素为一组,称为一个kernel。因为方针帧频》1000f/s,每帧图画更新的周期《1ms,而其间大部分时刻用来获取图画,无法在当时帧周期内完结图画缓存和处理进程。

本体系充分利用FPGA并行运算的特色,逻辑规划上选用三级流水线结构,如图3所示,并去除中心缓存环节,在读取图画的一起将每组数据直接送入流水线逐级进行处理。该流水线能够一起处理三组数据,且每组中8个像素的操作也是一起的。如此,图画读取和处理的进程同步进行,确保了数据处理的高效性与实时性。

三级流水线结构对应了方针检测的3个进程,逻辑规划如下:

(1)布景差分

在获取当时kernel值的一起,读取布景帧中对应地址的布景kernel值,将8个像素值一起对应做差,求得各像素方位的差值,存入差值寄存器,输入到下一级流水中。随后当即处理下一个kernel的像素,直到读完好幅图画。

(2)阈值切割

差值寄存器更新后,将8个像素差值与设定的阈值进行比照,大于阈值则二值化寄存器对应方位像素赋值为最大值,反之则赋值为0,成果输入到下一级流水。随后进行下一个kernel的切割。

(3)质心检测

质心检测逻辑分为两个分支,别离核算方针质心的X坐标和Y坐标。

核算X坐标的逻辑中,设置560个列相加寄存器,每逢二值化寄存器更新,则将8个二值化像素值参加对应列的列相加寄存器中。在读取完好帧图画时,比较各个列相加寄存器的值,得到最大值及对应列数,即为X坐标。

核算Y坐标的逻辑中,设置两个寄存器,一个存储当时行像素值的和值,另一个存储行像素和值的最大值。完结一行的读取后,将和值寄存器值与最大和值寄存器的值作比较,若大于最大和值,则将最大和值更新为该行和值,并记载此刻的行数;反之则坚持最大和值及对应行数不变。当读取完一帧图画后,最大和值对应的行数即为质心的Y坐标。

4体系测验与成果剖析

4.1测验环境

经过光学平板固定相机,坚持相机安稳;以白色A4纸作为布景,检测方针为一黑色碳球;镜头为焦距6mm的工业镜头,镜头与方针间隔20cm,测验时经过平板LED灯进行补光。测验首要分为精度测验、速度测验。

4.2精度测验

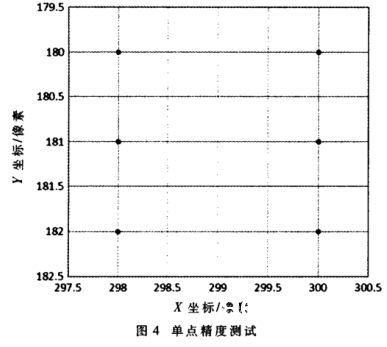

相机敞开后,首要收集500帧图画作为布景帧。后将方针固定于布景纸上,接连采样10000次,测验单点收集精度,并经过串口输出方针方位,制作图画。试验重复10次,测验成果如图4所示,测验的单点精度典型值为3×3(像素)。

4.3速度测验

4.3.1帧率测验

当相机运转在8bit深度、560×480分辨率下,其帧率理论值为1164f/s。帧率巨细经过以下办法进行测验:将体系置于运转形式,翻开串口东西接纳坐标数据,一起进行计时,经过必定时刻内接纳的坐标个数核算帧率。

试验成果如下:体系运转10s,共接纳11871个坐标数据,得到帧率丈量值为1187f/s。考虑到计时差错的要素,能够得出,丈量帧率与理论帧率根本共同,满意体系规划要求。

4.3.2运动测验

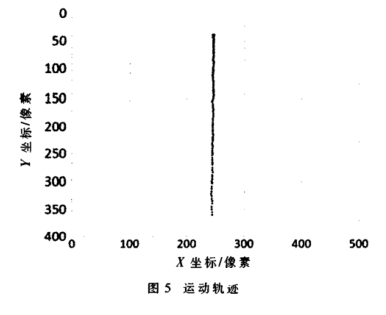

经过对方针物体自在落体进程进行检测,来进行体系运动测验。方针由停止状况自在落下,体系捕捉整个进程并将实时方位发送到串口。经过对接纳的方位坐标进行剖析,得到图5所示的运动轨道图以及图6所示的Y轴方向位移-时刻联系图。

由图6能够看出,位移曲线与理论曲线趋势根本共同,且略小于理论值。测验进程中,方针实践下落间隔为60mm,理论下落时刻应为0.11s。而实践丈量中,体系收集了140帧图画,实践下落时刻为0.12s,比理论时刻长0.01s。

剖析测验成果:首要应当考虑空气阻力的要素对自在落体运动发生影响,导致加速度的值小于重力加速度,进而使位移量小于理论值。别的,由图5能够看出,下落方向与Y坐标方向并非彻底重合,存在X方向的位移,所以Y方向的位移小于估计值。考虑到以上两个要素的影响,能够以为相机精确检测到了物体的高速运动进程。

5定论

本文研发了一套高帧频视觉实时方针检测体系,从硬件规划、软件装备、FPGA算法完结别离进行了介绍。选用了FPGA近端直接进行智能处理的战略,规划了流水线处理的结构,极大地处理了高速智能视觉检测体系的实时性问题。最终对体系进行了测验,成果表明,体系完结了560×480分辨率、1100f/s高速视频流的实时方针检测,精度到达3个像素。该体系能够使用到各种高速检测的场景中,例如位移速度丈量、振荡剖析、高速方针监测与操控等,后续作业将完善优化算法,进步检测的精度,并从圆形方针推行到不规矩方针,进步布景变化时检测的鲁棒性。

责任编辑:gt