直接数字频率组成(Direct Digital Frequency Synthesis)是从相位概念动身直接组成所需波形的一种新的频率组成技能。现在各大芯片制造厂商都相继推出选用先进的CMOS工艺出产的高功能和多功能的DDS芯片(其间使用较为广泛的是AD公司的AD985X系列),为电路规划者供给了多种挑选。然而在某些场合,专用的DDS芯片在操控方法、置频速率等方面与体系的要求距离很大,这时假如用高功能的FPGA器材规划契合自己需求的DDS电路便是一个很好的解决方法。

1 DDS电路作业原理

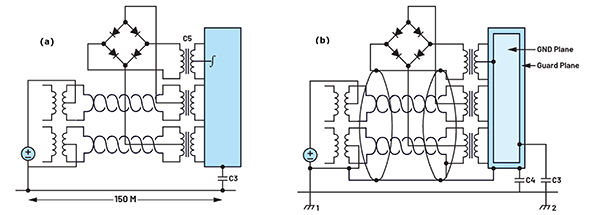

图1是DDS电路的基本原理框图。DDS的作业原理是以数控振动的方法发生频率、相位可控的正弦波。电路一般包含基准时钟、频率累加器、相位累加器、起伏/相位转化电路、D/A转化器(DAC)和低通滤波器(LPF)。

具体作业进程如下:每来一个时钟脉冲fc,N位累加器将频率操控数据M与相位寄存器输出的累加相位数据相加,把相加后的成果送至相位寄存器的输入端。相位寄存器一方面将在上一时钟周期效果后所发生的新的相位数据反应到累加器的输入端,以使累加器鄙人一时钟的效果下持续与频率操控数据相加;另一方面将这个值作为取样地址值送入起伏/相位转化电路(图1中的正弦查找表),起伏/相位转化电路依据这个地址值输出相应的波形数据。最终经D/A转化器和低通滤波器将波形数据转化成所需求的模仿波形。

DDS输出信号的频率为:![]() 可见,经过设定相位累加器位数、频率操控字和基准时钟的值,就能够发生任一频率的输出。DDS的频率分辨率为:

可见,经过设定相位累加器位数、频率操控字和基准时钟的值,就能够发生任一频率的输出。DDS的频率分辨率为: ![]() 因为基准时钟一般固定,因而相位累加器的位数就决议了频率分辨率,位数越多,分辨率越高。

因为基准时钟一般固定,因而相位累加器的位数就决议了频率分辨率,位数越多,分辨率越高。

2 使用FPGA规划DDS电路

在FPGA规划DDS电路时,相位累加器是DDS电路的一个要害部分,高效快速的累加器能进步DDS的功能。累加器能够使用FLEX器材的进位链,一起结合流水处理办法得到快速高效的电路结构。

相位/起伏转化电路是DDS电路中的另一个要害部分,该电路一般选用ROM结构,规划中面对的首要问题便是资源的开支。相位累加器的输出是一种数字式锯齿波,经过取它的若干位作为ROM的地址输入,然后经过查表和运算,ROM就能输出所需波形的数据。

在FPGA(Altera器材)中,ROM一般由EAB完成,而且ROM表的尺度跟着地址位数或数据位数的增加成指数递加,因而在满意信号功能的前提下,怎么削减资源的开支便是一个重要的问题。在实践运用中,相位/起伏转化电路的首要问题在于ROM的巨细(正弦波形存储器的字节数决议了相位量化差错,每个单元内的比特数决议了起伏量化差错),因而设计时充分使用信号周期内的对称性和算术联系来削减ROM开支。考虑以下的优化方法:余弦波信号关于![]() 直线成偶对称,基于此能够将ROM表削减至本来的1/2,再使用左半周期内,波形关于

直线成偶对称,基于此能够将ROM表削减至本来的1/2,再使用左半周期内,波形关于![]() 成奇对称,进一步将ROM表减至开始的1/4,因而能够经过一个正弦码表的前1/4周期就能够改换得到正弦和余弦的整个周期码表。这样就节省了3/4的资源。DDS电路的电路结构规划如图2所示。

成奇对称,进一步将ROM表减至开始的1/4,因而能够经过一个正弦码表的前1/4周期就能够改换得到正弦和余弦的整个周期码表。这样就节省了3/4的资源。DDS电路的电路结构规划如图2所示。

3 使用FLEX EP10K50完成DDS电路

EP10K50是Altera公司FLEX系列产品,EP10K50芯片的存储单元有10个EBA块组成,每个EBA块的存储容量为2048位,总存储容量到达20480位。因而能够充分使用它的存储容量来装备ROM表,然后完成相位/起伏转化电路。在这里将存储容量装备成两个1024×8的ROM表,一个为正弦表,另一个为余弦表,完成一个累加器为10位的DDS电路,仿真成果如图3。

上图是DDS电路的MAX+PLUSⅡ波形仿真成果。其间累加器字长N=10。频率操控字freq为H010,时钟clk为10MHz,查找表的深度为10位,字宽为8位。out_s和out_c分别为DDS输出的正弦和余弦信号。依据公式,输出的正弦和余弦信号的频率为:

![]()

为了便于调试规划电路,能够使用计算机高档言语将MAX+PLUSⅡ波形仿真成果转化为波形曲线,在这里凭借MAX+PLUSⅡ的表格文件(.tbl¬)。在图3的波形仿真成果中,在FILE菜单中挑选Creat Table Files,主动生成dds.tbl文件。经过编写一段Matlab程序,将clk、out_s和out_c引脚上的数据读出,然后绘出DDS电路的仿真波形曲线,如图4所示。

4 定论

使用FPGA完成DDS电路能够依据体系要求在操控方法、置频速率等方面完成得愈加灵敏。跟着超大规模集成电路技能的飞速发展,DDS电路中要害的相位累加器和相位/起伏转化电路在高功能的FPGA器材中得到解决,使规划者能够规划出契合自己功能需求的DDS电路。

责任编辑:gt