作者 邹志革 唐嘉杰 段富丽(华中科技大学 光学与电子信息学院,湖北 武汉 430074)

摘要:本文规划了电流检测电路,用于检测芯片的作业电流,比方物联网芯片、消费电子这些电路待机时电流能够低到几十微安,咱们将检测精度设置为10

μA。

关键词:电流检测电路;逐次迫临型;模数转化器;精度;

*取得第二届(2018)全国大学生立异创业大赛“紫光展锐杯”特等奖。

咱们选用8位的电荷重分配SAR-ADC进行电流检测。在规划进程中首要从三个目标切入:面积、精度、功耗。其间面积是最重要的要素,为减小面积,咱们尽量减小电路规划,选用合理的地图布局,面积为0.0388

mm2;电流检测规模为1 mA~100 mA,检测精度全体抵达1%,作业电压为1 V 时,全体功耗为19.3254

mW;因为首要的检测对象是低频乃至直流电流,关于检测速度的要求不高,咱们的电流检测频率是22.7

kHz。电流检测电路首要分为以下模块:带隙、分压模块、电容阵列、电压比较器、SAR操控逻辑、开关逻辑、输出寄存器等,选用预检测、准确检测两进程,完结电流的准确测定。

1 电路概述

电路全体结构如图1,主体为8位电荷重分配SAR-ADC结构。检测进程分为预检测和准确检测。预检测时由带隙及分压模块发生Vref0以及Vcm,经过等比电容阵列抵达比较器,比较器的输出经过SAR逐次比较型操控逻辑反应给电容阵列,操控开关的接入。逐位比较之后将每位数据存入寄存器,输出终究量化码。准确比较则是经过操控逻辑高三位数字量输出反应,经过火压模块选取正确的检测档位,然后得到适宜Vref及Vcm,再进行准确检测并输出成果。

1.1 根本模块概述

本节首要对咱们所完结的SAR-ADC根本模块的功用及其优缺点进行了简略的描绘,包括带隙基准模块、采样电路、电容阵列和比较器。

1.1.1 带隙基准模块

传统带隙含有运放,使电路结构规划杂乱,且含有电阻,存在精度及面积问题,功耗也较大。咱们所选用的无电阻无运放的带隙结构,电路结构简略,工艺兼容性好,且功耗较低,温度系数为85

ppm。

1.1.2 采样电路

传统的采样为开关电容或是传输门操控。咱们所选用的是栅压自举开关,有用的进步了开关线性度,减小了采样信号的失真,但这也会使电路杂乱度进步。一起,需求重视的是因为尺度规划问题而导致在线性度及寄生电容之间的折衷。

1.1.3电容阵列

顺次由巨细别离27、26、25、24、23、22、21、20、20倍cmin电容构成。电容中最终一个电容为dmmmy电容,只参加采样进程,转化进程中一直接地。转化进程分为传统的三阶段:采样阶段、坚持阶段、电荷再分配阶段。

1.1.4比较器

比较器电路由前置运放和latch锁存器组成。

运放选用简略的差分共源级输入结构,为了减小噪声选用P管输入。咱们选用负反应电阻负载,选用电流抵消技能,能够进步运放的增益,经过调理负载管的尺度能够得到很大的增益,且还有一个优点是负载管自偏置不需求额定的偏置电路供给偏置。

latch锁存器由两个背靠背的反相器正反应完结两个信号的比较。

1.1.5 输出阵列

输出阵列由8个寄存器组成,下一次采样开端时即将上一次检测成果输出。作用是将本来的逐位输出转化为同步输出,且能继续11个时钟周期,便利读数,进步精度,也能供给操控分压模块的挑选信号。

1.2 特征模块

本节包括分压模块、SAR操控逻辑、开关逻辑三部分,这也是咱们电路的首要立异点,突破了以往ADC的思路。

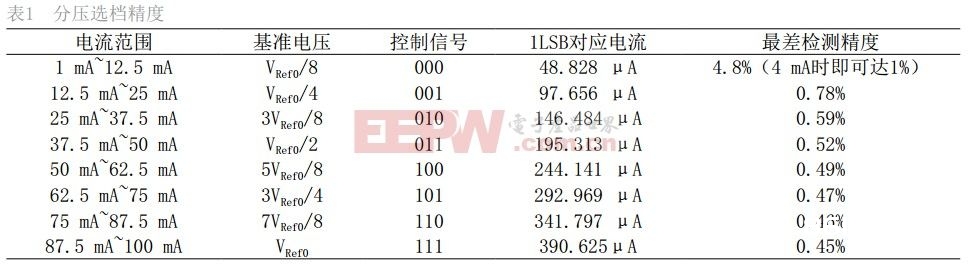

1.2.1 分压模块

以往ADC参阅电压固定,分辨率在整个丈量规模内为定值,而咱们经过火压模块改动ADC参阅电压Vref来抵达不同检测规模下的1%

精度,其它电路无须修正,一起减小了电路面积(8位),无需为完结10 mA的精度而运用更高位数ADC。

预检测时,选用带隙发生的电压即最大电压直接作为ADC的基准电压,便能够得到一组输出。然后用该组输出的高三位的八种不同状况来作为分压模块的反应操控,来选取准确的档位和恰当的基准电压Vref,进入准确检测,可得到准确的检测成果。用预检测进行反应操控,这样做使咱们献身了一部分的速度来完结更好的精度。

表1为分压选档的状况。

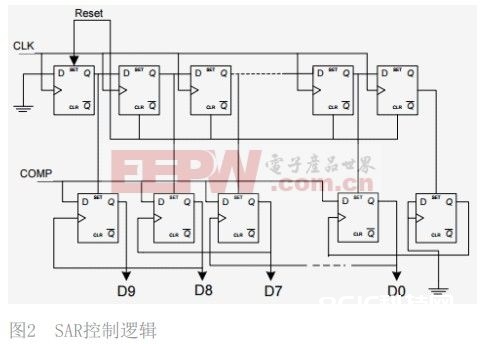

1.2.2 SAR操控逻辑

SAR操控逻辑实则为ADC的一个难点,咱们经过运用包括异步清零和置一的D触发器组成的电路来完结操控逻辑,原理易于了解,电路简略,易于完结。

表2为操控逻辑的有限状况搬运图。

当有Reset信号时,一切触发器复位输出0;无Reset信号,且时钟上升沿到来时,从最高位开端将该位输出先置位1,比较后的出实践D值,确认该位,从左到右一次进行,当九个时钟周期后,确认了输出的数字量,此刻下一个时钟沿来时,数字量一起输出。

1.2.3 开关逻辑

开关逻辑,选用挑选器构成,开关逻辑首要操控电容的负极板,依据reset和SAR逻辑输出的数字量来操控开关在不同阶段接入哪一个信号。

详细操控原理如图3。

2 全体仿真

2.1 输出波形仿真

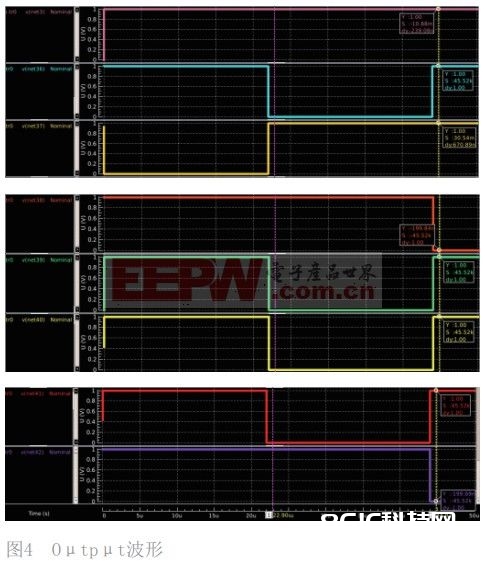

仿真电路图如下,完好的检测进程如下,首先将待检测的电流转化为电压Vin,采样后以Vref0(带隙发生的电压)对Vin进行逐次量化,量化进程已在规划陈述中详细描绘,得到输出成果后运用输出的高三位(即OUT7-OUT5)对分压模块进行操控,挑选恰当的Vref(Vref0分压得到),对Vin进行再一次采样量化,旨在选取恰当的量程,进步精度。

其间,电源电压Vdd=1 V,假定待检测电流转化所得的电压Vin=0.7 V,设此刻的Vref0 =1 V,可知准确的基准Vref=0.75

V,Vcm界说为Vref的一半。分两个阶段,预检测时ADC输出数字量前三位101可确认正确档位为Vref = 0.75

V,准确检测时ADC输出数字量为239,即11101110。CLK信号用脉冲源发生,其周期为2 ms,占空比50%,即频率为500

kHz,因为ADC完结一次完好转化需求22个时钟周期,因而ADC的作业频率为22.7 kHz,reset信号代表采样,其周期为22ms,高电平继续时间为2

ms。

阐明:依据比较器的带宽可知,实践的检测速度还能够更快,但因为本著作的检测对象是频率较低的电流,因而恰当下降了速度,以求更高稳定性。

咱们进行了50 ms时域仿真,所得输出波形如图4。

图中预检测输出10110001,即177,与理论值179有必定差错,但能选定0.75档位,准确检测时,输出成果是11101110,即238,理论值是239,据此测算得到的电压为238/256×0.75 = 0.697 ,与实践值0.7的差错为0.4%,因而电流检测差错符合要求。

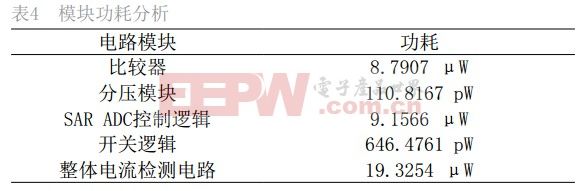

2.2 全体功耗仿真

全体功耗为19.3254 mW(不包括带隙、时钟等外部模块),作业电压为1 V,因而作业电流时19.3254mA。

3 地图

SAR-ADC的全体地图面积为0.0388 mm2。

4 全体功能

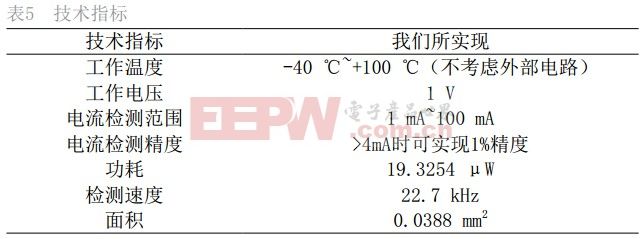

首要技能目标见表5。

5 定论与展望

5.1 电容阵列

考虑根据电容拆分技能的Vcm-based电容开关时序,与咱们现在所规划的单端电容开关时序比较,不只在按捺噪声方面有明显进步,该电容DAC也将面积削减了50%。

5.2 SAR操控逻辑

SAR-ADC在SAR逻辑的操控下完结逐次迫临的进程。为了进一步下降数字电路的功耗,能够选用根据动态逻辑的SAR操控技能,能够很大程度上削减数字电路的杂乱程度,一起因为运用的晶体管数目较少,功耗大大下降并且速度也有较大的进步。

5.3 电容失配

咱们考虑规划选用全定制的三明治结构单位电容,它首要是运用金属层之间的寄生电容来完结所需的电容值,且经过合理的地图布局能完结杰出的匹配。

5.4 精度

咱们现在的电路存在1

mA时只能抵达4%的精度。且完结一次检测,大部分的状况需求22个时钟周期。咱们考虑完结一位的检测就进行参阅电压的调整,不只能够缩短检测周期,还能够抵达每个电流的精度要求。

参阅文献

[1]王岑. 带模仿后台校对的14位低功耗SAR ADC规划[D].电子科技大学,2017.

[2]张琳. 低功耗高精度逐次迫临型模数转化器规划[D].河北科技大学,2018.

[3]刘满雀,姚若河.一种高精度电流检测电路的规划[J].我国集成电路,2009,18(03):53-57.

[4]D. Stack, A. Kelly and T. Conway, "A high accuracy and high bandwidth

current sense circuit for digitally controlled DC-DC buck converters," 2016 IEEE

Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA,

2016, pp. 1670-1674.

[5]朱樟明,杨银堂. 低功耗CMOS逐次迫临型模数转化器[M]. 北京:科学出版社, 2015.07.

[6]李燕霞,龚敏,高博.根据0.18μm的无电阻无运放低功耗带隙基准源规划[J].电子与封装, 2015,15(01):24-27.

[7]杨扬,王军,邓茗诚.一种高线性度CMOS栅压自举采样开关[J].通讯技能,2012,45(11):99-101.

作者简介:

唐嘉杰(1996—),男;段富丽(1997—),女。二人均为本科生,2015级,专业是集成电路规划与集成体系(杰出班)。

本文来源于科技期刊《电子产品世界》2019年第2期第84页,欢迎您写论文时引证,并注明出处