假如你在选用FPGA的电路板规划方面的经历很有限或底子没有,那么在新的项目中运用FPGA的远景就非常堪忧——特别是假如FPGA是一个有1000个引脚的大块头。持续阅览本文将有助于你的FPGA选型和规划进程,并且有助于你躲避许多难题。

选取一家供货商

你面对的第一个问题当然是供货商和器材的挑选。一般供货商决议计划倾向于你曾经触摸最多的那家——假如你是一位FPGA初学者当然另当别论了。或许这个决议计划早已由规划内部逻辑的工程师(或许便是你)依据了解的供货商或第三方IP及其本钱完成了。

供货商的软件东西也会影响到上述决议计划。下载并运用这些软件东西,不需求硬件就能将规划带入仿真阶段。这也是判别需求多大规划的FPGA的一种办法,条件是你的内部逻辑规划根本做完了。

要想知道FPGA的水有多深,需求多逛逛各家供货商的网站。假如你想从这些网站供给的海量(并且并不总是幻想中那么明晰的)信息中有所收成,有必要保证你有一整天闲暇的时刻。Altera和赛灵思公司是在市场份额和前沿技术方面都遥遥领先的两家公司。它们的器材运用内部装备RAM,因而要求运用寄存装备数据的外部ROM来“发动”器材(两家公司也都有些小的非易失性CPLD类产品)。值得考虑的其它供货商还有Microsemi/Actel、莱迪思和赛普拉斯。它们的器材功用包括非常低的静态功耗、用于“即时开机”发动的依据ROM的装备和模仿外设。

好了,至此供货商问题解决了。接下来是选取FPGA的系列和规划。供货商都会将它们的产品细分红多个系列,一般以低端、中端和高端功用(和规划)这样的含糊概念加以区别。片上RAM需求多大?要多少DSP/乘法模块,或千兆位收发器?你或许需求通读一遍数据手册,找出比方最大时钟频率和I/O时延等参数来协助你挑选正确的系列。需求重申的是,具有HDL代码是有很大协助的,因为规划软件能够让你知道合适哪种器材,它们是否能够满意你的功用要求。

你的运用还能够从不改动PCB就能更新器材中获益。一些FPGA系列包括许多引脚兼容的器材,能够在需求时让你切换到更大(或更廉价和更小)的器材。仅仅要保证针对最少数量的引脚输出进行规划。

不要忘了考虑其它一些细节,比方如何为不同的供电电压和I/O规范区分I/O组、PLL要求以及DDR接口要求。

咱们需求更多的功率!

一般很难核算一块电路板要求的最大电流。但FPGA电源规划适当有技巧。FPGA所需电流很大程度上取决于逻辑规划和时钟频率。相同一个器材在一个规划中或许只需0.5W,而在另一个规划中或许高达5W。

开发东西(或一个独立的程序或电子数据表)应该能够为给定规划供给功率预估值,但它们需求从你那儿得到许多附加信息,其间一些或许仅仅有依据的估测。假如有FPGA开发板,就应该有办法丈量各种情况下的供电电流。一些开发板乃至内嵌电流计显示器!仅仅要保证添加满足多的余量来应对规划更改以及特别工艺/温度要求。

下面是“难题”或许会呈现的时分:

● 做热剖析,并在必要时添加散热器。

● FPGA要求按次序加电吗?(你的规划很简单呈现5个或6个电源)

● 至少或许需求一个“安静的”电源,一般用于片上PLL。能够运用LDO加上一些无源滤波器材。千兆位收发器电源也能从低噪声中获益。

● 保证你了解FPGA在上电和初始化时在做什么事。许多器材在这个时分需求抽取很大的电流。

关于引脚及其它

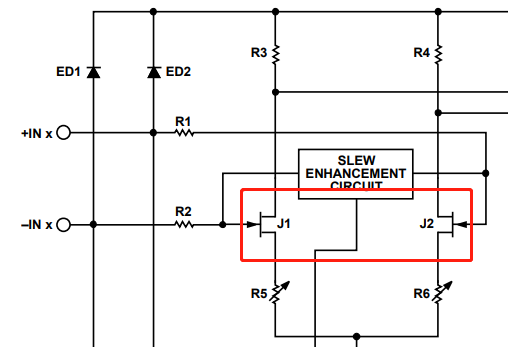

接下来能够仔细考虑引脚分配这件大事了。相同,假如你的逻辑规划现已到达能够被编译的阶段,就让规划软件来供给协助吧,或至少在做电路板之前验证你分配的引脚是可行的。你当然现已处理过显着的资源,比方依据供电电压区分I/O组,保证比方LVDS、SSTL或内部50Ω终端等“特别”引脚设置兼容它们地点的组和供电电压。

但在许多器材中存在更深层次的奇妙联系:在“不要在单端信号的2个IC绑定焊盘内放置差分对”,或“类似于参阅电压的输入有必要间隔时钟信号至少3个焊盘远”等言外之意隐含着杂乱的规矩。这些规矩很简单让人发疯。假如让人不胜忍耐,就让规划软件为你指出违例吧。假如你不这样做,那么这些问题肯定会让你疲惫不胜。

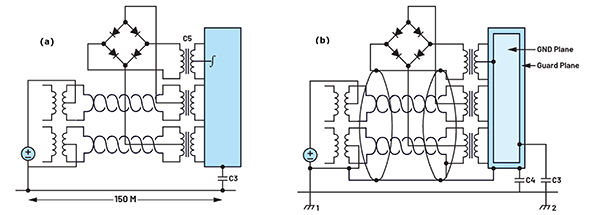

接地反弹或并发开关噪声(SSN)是别的一个考虑要素。因为FPGA的运用办法太多,所以供货商常常为最好的场景规划电源分配计划。假如你的规划要充分发挥I/O功用,比方运用数量许多的快速一起开关输出,那么你或许需求“削减”实践能够运用的引脚数量。尽量减小驱动和压摆率设置一般是一个好主意。规划软件也或许协助进行SSN剖析。我以为减小SSN的一个技巧是将未用引脚衔接到地,然后在规划文件中将它们设置为输出,驱动‘0’。这些引脚将被用作伪地引脚,尽管质量没有真实地好。

交给

现在是将凝聚了你汗水的产品交给给PCB地图规划的时分了。这儿我不想深化评论PCB规划(能够参阅下面给出的一些文章),但会指出针对FPGA规划需求考虑的一些事项。

堆叠规划对任何杂乱的电路板来说都很重要,而在最杂乱的电路板中一般都能找到FPGA的身影。跟着500引脚芯片被以为是“中等规划”以及不断缩小的引脚距离,你或许需求非常留心走线逃逸图画、焊盘中的过孔、引脚区域内的去耦电容以及电源与地平面。必定要有创造性。必要时能够切割电源平面(当然要防止高速走线)。假如满足当心,一些电源衔接(一般是部分的电源,如PLL电源)能够放在信号层上。将一些要害平面和信号放在最靠近FPGA的层。留心一些专门的地图主张,比方针对DRAM的一些主张。