长时刻可靠性的问题,比方电子搬迁(EM)失效机制,向来归于晶圆厂的处理范畴。但随着纳米规划中可靠性完结的更加困难,对规划人员而言,不能再把问题扔给制作甩手不管了。规划范畴也有必要做出尽力以取得更具有鲁棒性的地图。

电流密度过高导致金属原子逐步置换,这时就会发生电子搬迁问题。当很长时刻内涵同一个方向有过多电流流过期,在互连线上会开端构成空泛(Void,原子耗尽时呈现)和小丘(hillock,原子积累时发生)。足够多的原子被置换后,会发生断路或短路。当小丘触及附近的互连线时,短路呈现,然后引起芯片失效。

削减电子搬迁的办法之一是提取互连的寄生阻抗,并把它输入到一个仿真东西中,核算流经每根金属线的电流。运用互连每一部分的宽度信息,就有或许核算电流密度并由低到高进行分类。然后生成一个五颜六色图掩盖在地图上,由此标示出电流密度最高的各个区域。

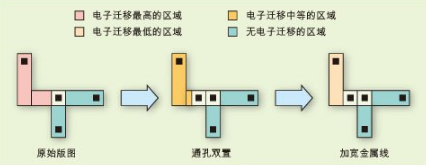

首要处理电流密度最高的区域,能够加宽互连金属线,添加通孔,下降电流密度。

一旦对地图做了批改,规划人员能够再进行一次寄生阻抗提取,从头仿真成果。经过这种办法,应该能够看到形成电子搬迁的电流密度有所下降。

应该:

1.履行EM剖析,承认存在EM问题的金属线。在最终地图上履行寄生阻抗提取,再把寄生阻抗值,以及该部分的宽度和方位等信息输入到一个仿真东西中。仿真生成一个电流密度图,掩盖在开始的地图上。

2.履行寄生阻抗提取时,考虑到金属宽度的改动。许多晶圆厂都供给寄生阻抗提取时的这种改动的建模机制。

3.考虑到提取时的厚度改动。金属厚度的改动会引起寄生阻抗值的改动,故有必要考虑在内。

4.履行仿真,核算整个芯片地图的电流密度。对每一层,确认电流密度阈值,以便取得对运用产品来说可接受的均匀失效时刻。

5.加宽电流密度过高的金属线。

6.在地图上进行通孔双置(VIA doubling)以削减寄生阻抗,然后减小电流密度。

7.从头履行寄生阻抗提取、仿真和可视化,以调查地图批改是否已下降了最严峻区域的电流密度。假如地图批改已把电流密度降至一个可接受的程度,规划就算完结了。

图1:加宽金属线和添加过孔以下降电流密度

不应该:

1.遗失EM剖析的履行。若未经检测,会引起功能下降,今后或许导致芯片失效。

2.把金属填充使命扔给晶圆厂做。金属填充很重要,能够进步规划的平面性,并且,假如正确完结的话,还能够把厚度改动降至最小。

3.履行无厚度和宽度改动的寄生阻抗提取。这会让提取发生过错,导致电流密度核算的过错。

4.在添加金属填料之前就经过厚度核算履行寄生提取。正确的过程是首要刺进金属填料,再改动宽度和厚度来履行提取。

5.不选用通孔双置。因为应力搬迁(Stress migration)或许导致通孔中堆积的金属更少,这会增大不良通孔中的阻抗,使电流密度更高。

6.运用平整仿真引擎(flat simulation engine)。运用分层架构将大幅度改进仿真时刻,削减内存运用。

7.核算电流密度时疏忽晶体管效应。因为流经一个网格的电流量取决于寄生参数及相关元件,故在履行EM剖析时进行晶体管级的仿真是很重要的。