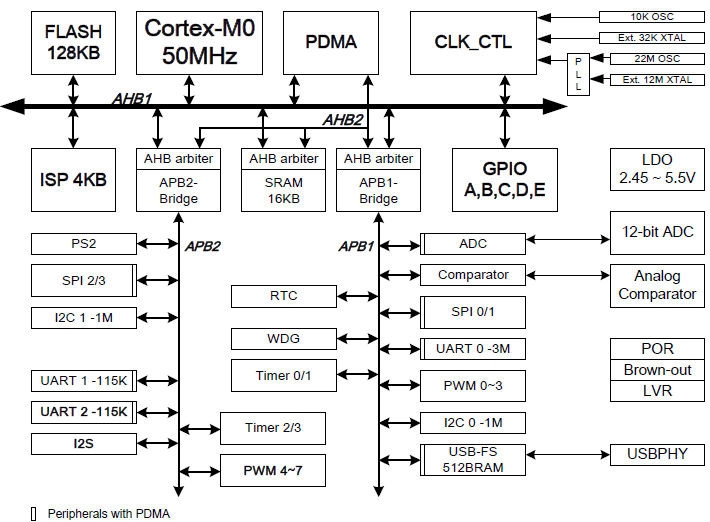

NUC1xx系列是32位的内嵌ARM Cortex-M0核的微操控器 ,适用于工业操控和需求丰厚的通讯接口的运用领域。ARM Cortex-M0 内核最高运转50MHz。宽电压作业规模 由2.5V 至 5.5V。

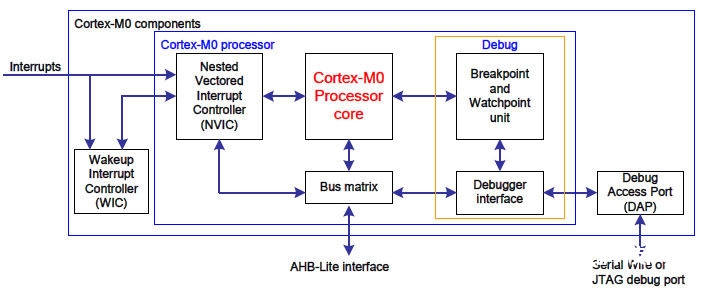

1.ARM Cortex-M0 内核

Cortex-M0处理器是32位多级可装备的RISC处理器。它有AMBA AHB-Lite接口和嵌套向量间断操控器(NV

IC),具有可选的硬件调试功用,能够履行Thumb指令,并与其它Cortex-M系列兼容。支撑两种形式:Thread形式和Handler形式;反常时,体系进入Handler形式,复位时,体系进入Thread形式。

1)根本特性:

特征:体系支撑小端(little-endian)数据拜访,供给单指令32-bit 硬件乘法器。

NV

IC:供给32个外部间断,具有4级间断优先级。有专用的不行屏蔽间断NMI。支撑电平缓脉冲间断触发。间断唤醒操控器W

IC,支撑极

低功耗休眠形式。

调试:供给4个硬件断点,2个调查点,用于非侵入式代码剖析的程序计数采样存放器,单步向量捕获才干。

总线接口:供给简略的集成到一切体系外设和存储器的单一32位AMBA-3 ABH-Lite体系接口;支撑DAP(Debug Access Port)的单一32位的从端口。

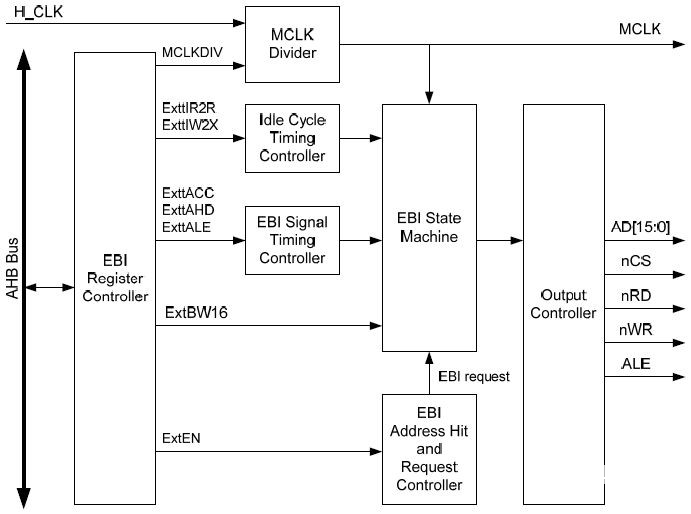

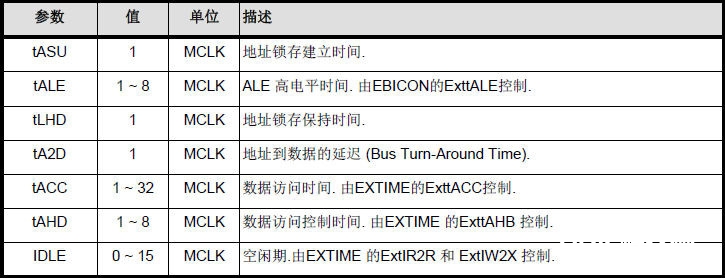

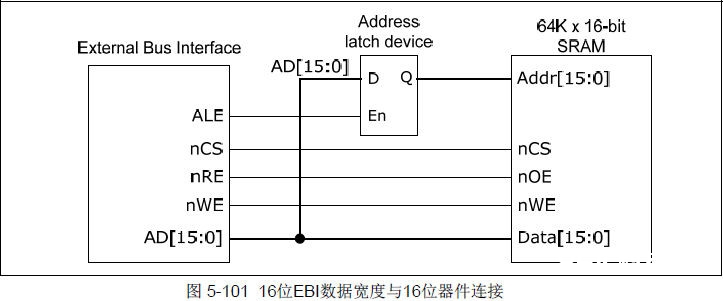

2)外部总线接口EBI

为节约外部设备与芯片的衔接线,EBI支撑地址总线与设备总线多路复用,且地址锁存使能信号ALE支撑地址和数据周期的不同。

支撑最大外部设备64KB(8位数据宽度)/128KB(16位数据宽度),支撑可变的数据拜访时刻(tACC)、地址锁存使能时刻(tALE)和地址坚持时刻(tAHD)。

EBI地址在0x6000 0000至0x6001 FFFF,一共内存空间为128KB,当体系恳求的地址在EBI的内存空间,相应的EBI片选信号有用,EBI状况机作业。

芯片内的一切EBI信号经过MCLK同步,MCLK能够设置EBICON中的MCLKDIVN分频HCLK/32

2.体系办理器

1)体系复位

复位源包含:上电复位、复位脚(/RESET)上有低电平、看门狗复位、低压复位、欠压检测复位、Coretex-M0 单片机复位、体系复位。

体系复位和上电复位使整个芯片复位,包含外设。

2)体系电源

该器材的电源分为3类:a.由AVDD和AVSS供给的模仿电源,为模仿部分作业供给电压;b.由VDD和VSS供给的固定的2.5V的数字电源,用于数字操作和I/O引脚的内部稳压电源;c.VBUS供给给USB的电源,用于USB模块传输操作。

内部电压调节器输出LDO和VDD33,需求在相应的引脚上外接%&&&&&%。

3)体系内存映射

NUC1xx 供给4G字节的寻址空间,NUC1xx系列仅支撑小端数据格局,ROM、SRAM和操控存放器共同编址。

4)体系守时器

Cortex-M0 包含一个24位体系守时器SysTick,使能后,守时器从SysTick 其时存放器(SYST_CVR)的值向下计数到0,下一个时钟边际,从头加载存放器(SYST_RVR) 的值。当计数器减到0时,标志位COUNTFLAG置位,在读数时,清COUNTFLAG标志位。

Cortex-M0 供给间断操控器,用于整体办理反常,NV

IC和处理器内核严密相连。

NV

IC结构支撑32(IRQ[31:0])4级离散间断优先级,当承受任何间断时,ISR的开端地址可从内存的向量表中获得,当开端地址获得时,NV

IC将主动保存处理状况到栈中,包含以下存放器“PC, PSR, LR, R0~R3, R12” 的值. 在ISR完毕时, NV

IC 将从栈中康复相关存放器的值,进行正常操作,因而花费少数时处理间断恳求。向量表的基地址为0x00000000. 向量表包含复位后栈的初始值,一切反常处理器的进口地址. 向量号标明处理反常的先后次第。

6)体系操控存放器

体系操控存放器操控了Cortex?-M0的状况和操作形式,包含CPUID、Cortex?-M0间断优先级和Cortex?-M0电源办理。

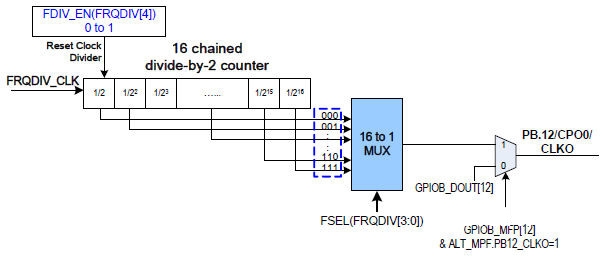

3.时钟操控器

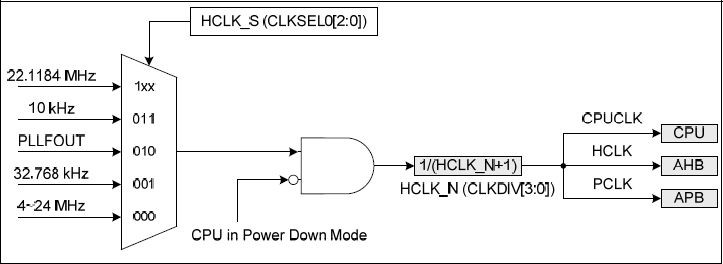

时钟操控器为芯片供给时钟源. 包含AMBA接口模块和一切外围设备时钟,时钟发生器由如下5个时钟源组成:一个外部 32KHz 晶振、一个外部 12MHz 晶振、一个可编程的 PLL FOUT(PLL 由 12M 和 22M组成)、一个内部 22MHz RC 振荡器、一个内部 10KHz 振荡器。

时钟源切换取决于存放器HCLK_S(CLKSEL0[2:0]):

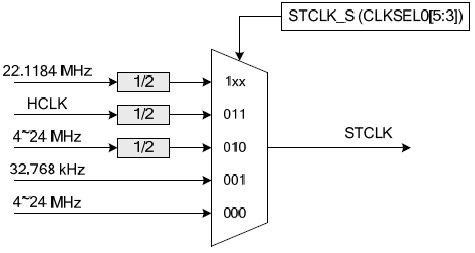

Cortex?-M0内核的SysTick时钟源能够挑选CPU时钟或外部时钟(SYST_CSR[2]),假如运用外部时钟,SysTick时钟(STCLK)有5个时钟源,

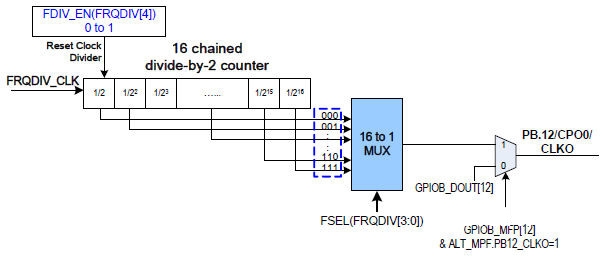

该器材包含分频器,由16级2分频移位存放器组成. 因而有16种分频挑选从 Fin/21 到 Fin/216 ,其间 Fin 为输入到时钟分频器的时钟频率.

4.存储器

1)程序存储器

具有32K/64K/128K字节的片上FLASH ROM,用于存储程序代码(APROM),4kB在体系编程(ISP)加载程序内存(LDROM),用于存储ISP引导代码,用户能够经过ISP/IAP更新FLASH中的程序,用户设置Config0以挑选从AP_ROM或LD_ROM开端。关于64/32K字节的器材,NUC1XX系列为用户供给4k字节的数据FLASH用于存储一些运用所需的数据;关于128k字节的器材,数据flash与128K的程序内存同享,其开端地址是可装备的,由用户在Config1中界说.用户能够依据其运用的需求来界说数据FLASH的巨细。数据FLASH的基地址由DFBADR界说

2)数据存储器

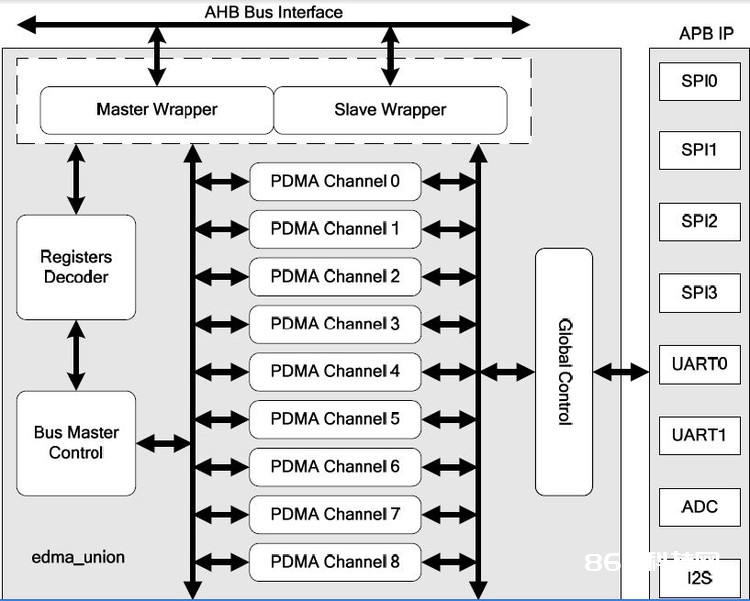

4K/8K/16K字节内建SRAM,支撑9通道PDMA用于SRAM和周边设备的主动数据传输。

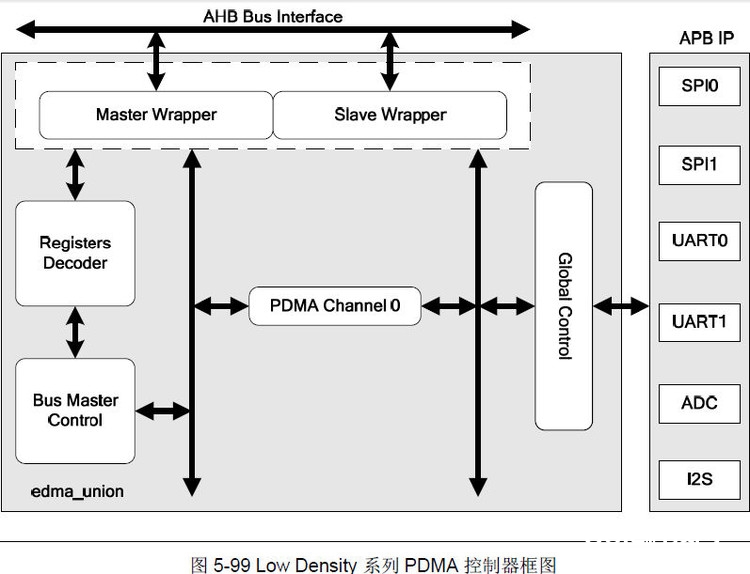

3)PDMA操控器

NUC100/NUC120系列包含直接存储器拜访(PDMA)操控器,用于APB和存储器间的数据交换,具有 9 路DMA (外设-存储器 或存储器 -外设 或存储器-存储器) 通道,每路 PDMA 通道 (PDMA CH0~CH8), 在外设 APB IP和存储器间有一个字的数据缓冲器,每个通道可支撑一个单项传输。

PDMA 运转经过软件轮番检测或接纳到内部PDMA 间断, CPU能够辨认PDMA运作的完结,PDMA 操控器可增加源和意图地址。关于源和意图地址而言,PDMA 操控器具有两种形式:increased和fixed形式。每个PDMA模仿通道没有先设定,因而用户需求经过设定PDMA_PDSSR0和 PDMA_PDSSR1先行装备每路的PDMA 通道。软件需使能DMA通道PDMA[PDMACEN] 而且写有用的源地址到PDMA_SARx存放器、意图地址到PDMA_DSABx存放器、传输核算数到PDMA_BCRx存放器、以及设置DMA_CSRx PDMA[Trig_EN]触发。PDMA将持续传输直到PDMA_CBCRx为0。PDMA (外设-到-存储器、存储器-到-外设) 形式,DMA能够在外设APB IP (ex:UART,SPI,ADC….) 和Memory将传递数据。

硬件通道优先级:DMA通道0有最高优先级,通道n有最低优先级。

Low Density系列仅支撑1个PDMA通道:

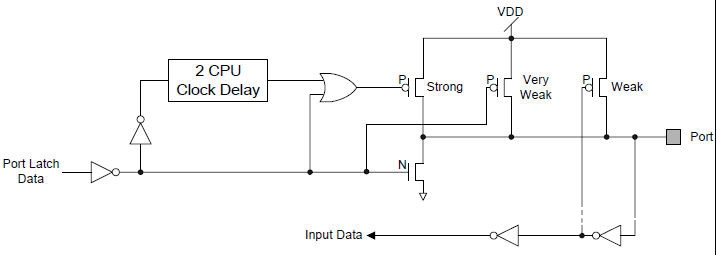

5.通用I/O

有80个通用I/O引脚,能够和其他功用引脚同享。80个引脚分配在GPIOA, GPIOB, GPIOC, GPIOD与GPIOE五个口上,每个口最多16个引脚。每个引脚都是独立的,都有相应的存放器来操控引脚形式与数据。I/O引脚上的I/O类型可由软件独登时装备为输入,输出,开漏或准双端形式.一切的I/O引脚默许处于准双端形式。

可选的TTL/Schmitt触发输入,支撑大电流驱动/灌入I/O形式。

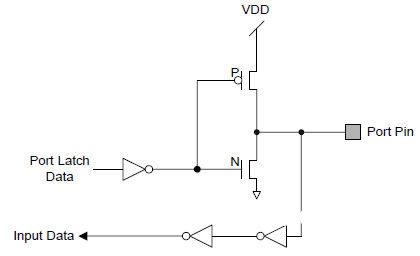

1)输入形式

设置GPIOx_OMD(PMDn[1:0])为00b,GPIOx port[n]为输入形式,I/O引脚为三态(高阻),没有输出驱动才干。GPIOx_PIN的值反映适当端口的状况。

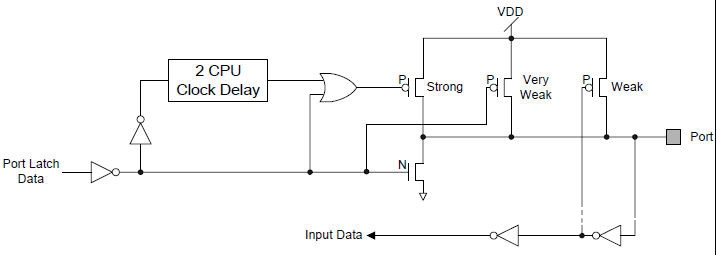

2)推挽输出形式

设置 GPIOx_OMD(PMDn[1:0]) 为 01b,GPIOx port [n] 为输入形式,I/O支撑数字输出功用,有source/sink电流才干. GPIO_DOUT 相应位的值被送到相应引脚上。

3)开漏输出形式

设置 GPIOx_OMD(PMDn[1:0]) 为 10b,GPIOx port [n]为开漏形式,I/O支撑数字输出功用,仅有灌电流才干,需求一个外加上拉电阻驱动到高电平。

4)准双端形式

设置GPIOx_OMD(PMDn[1:0]) 为 11b,GPIOx port [n] 为准双端形式,I/O一起支撑数字输出和输入功用,但source电流仅达数百uA. 要完结数字输入,需求先将GPIOx_DOUT 相应方位1, 准双端输出是80C51及其派生产品所共有的形式。准双端形式的source 电流才干仅有200uA到30uA(相应VDD的电压从5.0V到2.5V)

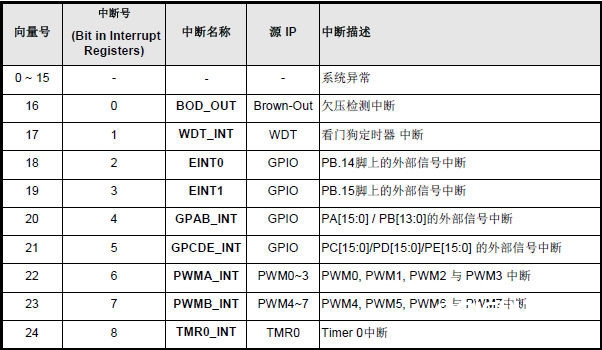

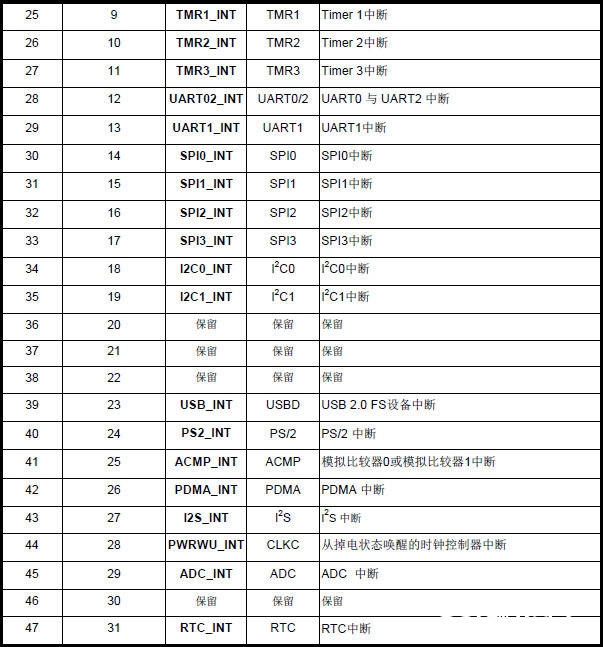

6.间断体系

NUC1xx 系列支撑下表所列的反常形式. 与一切间断相同,软件能够对其间一些间断设置4级优先级. 最高优先级为“0”,最低优先级为“3”,一切用户可装备的优先级的默许值为“0”. 留意:优先级为“0”在整个体系中为第4优先级,排在“Reset”, “NMI” 与“Hard Fault”之后。

呼应间断时,处理器主动从向量表中取出ISR的开端地址,关于ARMv6-M, 向量表的基地址为0x00000000。向量表包含复位后栈的初始值,一切反常处理器的进口地址。

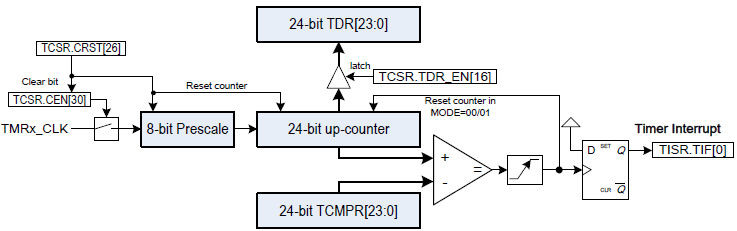

7.守时器

守时器模块包含4组32位守时器(包含一个8位预分频计数器,一个24位向上计数器),TIMER0~TIMER3 (TIMER0, TIMER1坐落 AHB1 ,TIMER2 和 TIMER3 坐落 AHB2);各通道有独立的时钟源,每个通道有5个时钟源选项。经过TDR(守时器数据存放器)可读取内部24位向上计数器值

时刻溢出周期= (守时器时钟周期) * (8位预分频值 + 1) * (24位 TCMP)

守时器操控器供给one-shot(单次触发形式)、period(周期触发形式)、toggle(可编程时钟输出)、持续计数模式和事情计数器形式;

1)单次触发形式

一旦守时器计数器的值抵达TCMPR的值,且IE置1,则

守时器间断方位位,发生间断信号并送到NV

IC告诉CPU,标明守时器发生溢出,守时器计数操作间断,该比较的操作仅进行一次。

2)周期触发形式

一旦守时器计数器的值抵达TCMPR的值,守时器计数器的值回来计数初值并再次计数,假如IE置1,则守时器间断方位位,发生间断信号并送到NV

IC告诉CPU。

3)可编程时钟输出形式

一旦守时器计数器的值与TCMPR匹配,且IE置1,则守时器间断标志方位位,发生间断信号并送到NV

IC告诉CPU,相应toggle输出信号置1,守时器计数器的值回来到计数初值,守时器计数器从头计数,假如间断标志被软件铲除,一旦守时器计数器的值再次与TCMPR匹配,则守时器间断标志为再次置位,发生间断信号并送到NV%&&&&&%告诉CPU,相应toggle输出信号置0;如此往复,发生占空比为50%的信号输出。

4)持续计数形式

发生间断信号的发生取决于TDR==TCMPR。守时器计数器的值与TCMPR匹配后,守时器计数器持续计数,而不回来计数初值,用户能够经过不断改动TCMPR值来完结计数或守时功用。

5)事情计数器

守时器计数器的时钟源TMRx_CLK有必要设置为HCLK,能够经过设置TEXCONx[7]来使能或制止TM0-TM3防颤动功用,以及设置TEXCONx[0]来设定TM0-TM3上升沿或下降沿计数。假如禁用计数防颤动,事情计数源频率频率有必要小于1/3HCLK,假如使能计数防颤动,事情计数源频率有必要小于1/8HCLK,

8.串行口

MCU供给3个UART通道,UART0支撑高速,UART1~2支撑一般速度,别的UART0与UART1支撑流操控,UART0与UART1能够选用DMA操控器。

通用异步收/发器(UART) 在从外设收到数据的时分履行串到并的转化,在从CPU收到数据的时分履行并到串的转化。该串口一起支撑LIN主机形式和 IrDA SIR 功用。有7 种类型的间断:发送FIFO 空间断(Int_THRE)、接纳极限抵达间断(Int_RDA)、线状况间断 (overrun error 或许校验过错或许framing error或许break 间断) (Int_RLS)、超时刻断(Int_Tout)、MODEM 状况间断(Int_Modem) 、唤醒状况间断 (Int_WakeUp)和LIN 接纳间断侦测间断。

UART0 接口操控器一个内嵌64-byte 发送FIFO (TX_FIFO) 和 64-byte 接纳 FIFO (RX_FIFO) 来下降CPU的间断数量;UART1~2内嵌 16-byte 发送FIFO (TX_FIFO) 和16-byte (每个字节加3比特的过错数据) 接纳FIFO (RX_FIFO) 来下降CPU的间断数量,UART包含一个可编程的波特率发生器,它能够将输入晶振除以一个除数来得到收发器需求的时钟. 波特率公式是 Baud Rate = UART_CLK / M * [BRD + 2]. 其间M和BRD在波特率分频存放器UA_BAUD中界说。

UART0与UART1 操控器用 2 种low-level 信号, /CTS (clear-to-send)和 /RTS (request-to-send)支撑主动流程操控功用。

UART 操控器供给 串行 IrDA (SIR, 串行红外) 功用 (用户需置位 UA_FUN_SEL[IrDA_EN] 使能 IrDA 功用),SIR 界说短程红外异步串行传输形式 1 开端位, 8 数据位, 和1 间断位. 最大数据速率 为 115.2 Kbps (半双工). IrDA SIR 包含 IrDA SIR 编码/解码协议。

UART 操控器具有LIN(局域网) 功用. LIN 形式供给设定LIN_EN bit 位 UA_FUN_SEL 存放器. 在LIN 形式, 1 开端位 8 数据位和1 间断位相共同,同规范LIN 相同。

串口特性:可编程为5,6,7,8位的数据位,可编程奇偶校验或无校验,可编程为1,1.5,2位的间断位,

UART支撑RS-485 9位形式功用,设置UA_FUN_SEL挑选RS485形式;操控器能够装备成可寻址的从机形式,RS485发送可经过设置优先级(bit9)为1标志地址特性,关于数据特性,标志优先级为0;设置存放器UA_LCR操控第9位(PBE,EPE和SPE置位,第9位发送0;PBE,SPE置位,EPE清零,第9位发送1)。

RS485主动地址辨认形式:接纳器在检测到地址字节(bit9 =1),而且地址字节数据与UA_RS_485[ADDR_MATCH]的值相匹配之前将疏忽一切数据,地址字节数据将存储在RX_FIFO,一切接纳字节数据将被接纳并存储于RX_FIFO,直到地址字节或数据字节与UA_RS_485[ADDR_MATCH]的值不匹配。

RS485一般多点操作形式:流设置UART_FCR[RS485_RX_DIS]使能UA_RS_485[RS485_NMM],接纳器会疏忽数据,直到检测到地址字节(bit 9=1)而且地址字节数据存储到RX_FIFO;流制止UART_FCR[RS485_RX_DIS],接纳器将接纳任何数据。

RS485编程流程:1)设置存放器UA_FUN_SEL的FUN_SEL位挑选RS485形式;

2)设置存放器UA_FCR中的RX_DIS位使能或制止RS485接纳器;

3)设置RS_485_NMM形式或RS_485_AAD形式;

4)假如挑选RS_485_AAD形式,AADR_MATCH设置成主动地址匹配值;

5)若为主动方向形式,设置R2_485_AUD;

9.实时时钟

时钟源由外部32.768KHz晶振供给,管脚为X32I 及X32O 或许外接32.768KHz 频率的信号源。RTC支撑时刻格局 (秒,分,时)存放器(TLR)以及日历格局(日,月,年)存放器(CLR)。数据格局由BCD格局存取。模块支撑闹钟功用,(TAR)存放器用于指示时刻闹铃,(CAR)用于指示日期闹铃。

RTC 模块支撑时刻记步及闹钟间断,经过设定TTR.TTR[2:0],间断供给8级挑选1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 及1 秒。当 RTC 计数器内的值TLR 和CLR 与TAR和CAR适其时,会引发间断标志 (RIIR.AIF)。

根据RTC时钟与体系时钟选用不同的模块,用户对RTC存放器写入后,有必要等候2个RTC时钟周期(60us)后,存放器内的值才会被更新。存放器AER 位 15~0 作为RTC答应读/写暗码,用于防止掉电时对RTC构成的误写,要拜访RTC的存放器AER,有必要写入0xa965以翻开拜访约束,读写使能后,将会有用512个RTC时钟,之后主动封闭。

10.PWM发生器和捕捉守时器

1)PWM发生器

包含4组PWM发生器,可装备为8个独立的PWM输出,PWM0~PWM7,或4组互补的PWM对,带4个可编程的死区发生器。4组PWM发生器供给8个独立的PWM间断标志,当PWM向下计数周期抵达零时触发间断。PWM发生器能够界说为单触发形式或接连输出PWM波形。

每组PWM发生器带有8位预分频,一个时钟除频供给5级时钟源(1, 1/2, 1/4, 1/8, 1/16),两个PWM守时器包含2个时钟挑选,两个16位PWM向下计数计数器用于PWM period 周期操控,两个16位比较器用于PWM duty 周期操控以及死区发生。

当PCR.DZEN01置位, PWM0 与 PWM1构成互补的PWM周期,这一对PWM的周期、占空比和死区时刻由PWM0守时器和死区发生器0决议;其他PWM互补对相似。

当16位向下计数计数器抵达0时,间断恳求发生。假如PWM守时器被界说为接连形式,当向下计数器抵达0时,会主动从头导入设定值(CNRx)并从新开端运转下一个周期。假如守时器设为单触发形式,向下计数器间断计数,并发生间断恳求。比较器数据用于设定脉宽,计数器操控逻辑在计数器计数到比较值时将PWM输出变高。

PWM period 和duty 操控由向下计数的PWM存放器(CNR)以及PWM比较存放器(CMR)操控。占空比 = (CMR+1)/(CNR+1).

PWM 频率 = PWMxy_CLK/(prescale+1)*(clock divider)/(CNR+1); xy代表01, 23, 45 或 67, 取决于所挑选的PWM通道.

CMR >= 计数值: PWM 输出为高,反之PWM输出低;PWM低脉宽= (CNR-CMR) ; PWM高脉宽=(CMR+1)

PWM守时器具有双缓存功用。存放器预先设定的值,在一个周期完结后,能够主动重载。PWM计数器值写入CNR0~7,并可从PDR0~7内读出;PWM 操控存放器(PCR) 的CH0MOD 位界说PWM0是主动重载形式或是单触发形式。当PWM计数器计到0,MCU主动重载CNR0 值到PWM 计数器。双缓存答应CMR字其时运转时改写,下一个周期内值被导入运转。

PWM死区发生器,用于维护器材电源(这一特性用于在开关设备的断开和另一个开关设备的闭合之间刺进一个时刻缺口,使它们不会处于一起闭合的状况)。该功用发生可编程的推迟时刻到PWM上升沿输出,用户经过编程PPRx.DZI确认死区距离。

2)捕捉守时器

当PWM输出模块的输入捕捉功用使能,可一起用作捕捉功用。捕捉器0和PWM0运用同一个守时器,捕捉器1和PWM1运用另一组守时器,以此类推。在运用捕捉功用之前,有必要预先装备PMW守时器。当输入信号有上升沿改动时,PWM计数器的值将存入CRLRx存放器,当输入信号有下降沿改动时,PWM计数器的值将存入CFLRx存放器。

设定CCR0[1] (上升沿触发间断有用)和CCR0[2](下降沿触发间断有用),能够使捕捉器通道0作为间断源。相同设定CCR0[17] 和CCR0[18],能够设定通道1。最大的捕捉频率由捕捉间断推迟决议,捕捉间断发生时,软件履行以下三步:a.读PIIR获取间断源;b.读CRLRx/CFLRx获取捕捉值和写

1清PIIR,假如间断推迟在T0完结,捕捉信号在(T0)距离内有必要不能改动,此条件下,捕捉频率最大为1/T0。

每逢捕捉操控器触发捕捉间断时,相应的PWM计数器会一起重载CNRx的值,通道低脉宽为(CNR+1-CRLR);通道高脉宽为 (CNR+1-CFLR)。

3)PWM守时器及捕捉装备

PWM守时器敞开过程:

1. 装备时钟挑选 (CSR)

2. 装备预分频(PPR)

3. 装备反向翻开/封闭,死区翻开/封闭,主动重载/单触发形式以及PWM守时器封闭 (PCR)

4. 装备比较器存放器(CMR) 设定PWM 占空比.

5. 装备PWM计数器存放器 (CNR) 设定PWM周期.

6. 装备间断使能存放器 (PIER)

7. 装备PWM输出使能 (POE)

8. 装备相应的管脚GPIO (GPA_MFP)

9. 装备相应的管教到输出形式 (GPIOA_OMD)

10. 使能PWM守时器(PCR)

PWM守时器封闭过程:

方法 1:设定16位向下计数计数器(CNR)为0,并查看PDR状况。当PDR抵达0,封闭PWM守时器 (PCR的CHxEN位). (引荐)

方法2:设定16位向下计数计数器(CNR)为0,当间断条件发生。在间断内封闭PWM守时器(PCR的CHxEN位). (引荐)

方法3:直接封闭PWM守时器(PCR的CHxEN位). (不引荐,由于制止CHxEN会当即间断PWM输出信号,导致PWM占空比改动,或许引起电机的损坏)

捕捉开端过程:

1. 装备时钟挑选(CSR)

2. 装备预分频(PPR)

3. 装备通道使能,上升/下降沿间断使能以及输入信号反向翻开/封闭 (CCR0, CCR1)

4. 装备PWM计数器存放器 (CNR)

5. 装备捕捉输入使能存放器 (CAPENR)

6. 装备相应的GPIO管脚用于PWM功用 (GPA_MFP)

7. 装备相应的GPIO管脚于输入形式S (GPIOA_OMD)

8. 使能PWM守时器(PCR)

11.看门狗守时器WDT

看门狗守时器包含一个18位的主动运转的计数器,可编程其守时溢出距离。设置WTE(WDTCR[7])使能看门狗守时器和WDT计数器开端计数. 当计数器抵达挑选的守时溢出距离,看门狗守时器间断标志WTIF被当即置位,并恳求WDT间断(假如看门狗守时器间断使能位WTIE置位),一起,紧接着会有一个指定周期(1024*Twdt)延时,用户有必要在指定周期内设置WTR(WDTCR[0]) (看门狗守时器复位)为高,重置18位WDT计数器,防止CPU复位,WTR在WDT计数重置后主动由硬件清零。

经过设置WTIS(WDTCR[10:8])挑选8个守时溢出距离(2^4~2^18),假如在特别推迟时刻间断后,假如WDT计数没有被清零,看门狗守时将置位看门狗守时器重置标志(WTRF)为高并使CPU复位. 这个复位将持续63个WDT时钟,然后CPU重启,并从复位向量(0x0000 0000)履行程序,WTRF将不被看门狗复位清零,用户可用软件拉低WTFR。

12.模仿数字转化(ADC)

NUC1XX 系列包含 一个12-bit 8通道逐次迫临式 模仿 – 数字转化器 (SAR A/D converter)。A/D 转化器支撑 三种操作形式: 单一、单周期扫描 和接连扫描形式。开端A/D 转化可软件设定和外部STADC/PB.8 pin敞开。

当改动运转形式或模仿输入通道使能时, 为了防止过错的操作, 软件需清 ADST 位为 0 (ADCR register). A/D 转化将间断 并进入idle 形式.

A/D转化器有3个间断源:A/D 转化完毕时ADF(ADSR存放器)位被置1;当A/D转化成果同ADCMPR0/1存放器设定值相匹配时,CMPF0/1会被置1;当ADF、CMPF0、CMPF1其间一个标志被置1,且其相应的ADIE 位(ADCR 存放器)及CMPIE(ADCMPR0/1存放器)置1时,将发生 ADINT 间断恳求。

1)特征

模仿输入电压: 0~Vref (Max to 5.0V).

12位分辨率和10位精确度确保。

多达 8 路单端模仿输入通道或4路差分输入。

最大 ADC 时钟频率 16MHz/20MHz。ADC时钟频率= (ADC clock source frequency) / (ADC_N+1);

高达600K/1M SPS 转化速率, 转化时刻少于 1us.

转化成果可和指定的值相比较 当转化值和设定值相匹配时,用户设定发生间断恳求.

通道7支撑3输入源:外部模仿电压, 内部基准电压和内部温度传感器输出.

支撑本身校对功用削减转化的差错,用户可写1到CALEN 位(ADCALR 存放器)使能本身校对功用, 当内部校对完结CAL_DONE为高。

2)单触发形式

在单触发形式下, A/D 转化仅仅在指定的单一通道中履行一次,运作流程如下:

1. 当 ADCR 的ADST 置位开端A/D 转化,可经过软件或外部触发输入.

2. 当 A/D 转化完结,转化值将存储在与通道相对应的A/D数据存放器中.

3. A/D 转化完结, ADSR 的ADF 方位位. 若此刻ADIE 方位位, 将发生ADINT 间断恳求.

4. A/D 转化期间,ADST 位坚持为1,A/D 转化完毕,ADST 位主动清 0,A/D 转化器进入idle 形式。ADST清0后,至少要等一个ADC时钟,才干再将ADST方位1,不然A/D 转化器或许无法运作。

3)单周期扫描形式

在单周期形式下,ADC会对一切指定的通道进行一次采样和转化,且从编号最小的通道开端运作,详细流程如下:

1. 软件置位 ADCR 存放器的ADST 位或外部触发输入置位,A/D 转化从最小编号的通道开端。

2. 每路 A/D 转化完结后, A/D 转化数值将装载到相应数据存放器中。

3. 当被挑选的通道数都转化完结后,ADF 位(ADSR 存放器)置位。若此刻 ADIE 置位, 将发生 ADINT 间断恳求。

4. A/D 转化完毕, ADST位主动清0,A/D 转化器进入idle 形式。若在转化过程中ADST被清0,则无法确保存储在数据存放器中的值之正确性。ADST清0后,至少要等一个ADC时钟,才干再将ADST方位1,不然A/D 转化器或许无法运作。

4)接连转化形式

在接连形式下, 可经过设定CHEN 位 ADCHER 存放器 (maximum 8 channels for ADC) 使能 A/D 转化.运作流程如下:

1. 软件置位 ADCR 存放器的 ADST 位或外部触发输入置位,A/D 转化从最小编号的通道开端。

2. 每路 A/D 转化完结后, A/D 转化数值将装载到相应数据存放器中.

3. 当一切被使能的通道数依序完结一次A/D转化后,ADF位(ADSR 存放器)置位。若此刻 ADIE 置位,将发生ADINT间断恳求,当 A/D 转化完结后. 使能的最小编号通道将开端新的转化。

4. 只需ADST坚持 1,就重复过程2 ~ 3。当 ADST 位清 0, A/D 转化将间断,但无法确保最小通道使能通道的转化成果之正确性。

5)比较形式下的A/D转化成果监控

ADC操控器供给2组比较存放器 ADCMPR0和ADCMPR1监控 A/D 转化模块的2路转化成果值。可经过软件设定CMPCH[2:0] 来挑选监控那路通道,而CMPCOND 位被用来查看转化值小于或大于等于CMPD[11:0]指定值,当CMPCH指定的通道转化完结时,比较行为将会被主动的触发一次,当比较成果与设定值匹配,比较计数器将加1,不然比较计数器清0。当计数器的值与(CMPMATCNT+1)匹配,CMPF位将置1,将发生ADINT间断恳求。在扫描形式下软件可运用于监控外部模仿输入pin脚电压改动。

6)外设DMA 恳求

当 A/D 转化完结,成果装载到ADDR 存放器且VALID 置位。假如ACDR存放器PTEN方位位, ADC操控器将发生PDMA恳求(P_nDRQ) ,以便用户将数据传输到用户指定的内存空间,而无需CPU参加。不论挑选哪个通道,PDMA操作的源地址都是ADPDMA。假如ADC作业在单周期或接连扫描形式,当PDMA传输转化成果时,ADC将持续转化挑选的下一通道,用户可经过读ADPDMA监控其时PDMA传输数据。

13.模仿比较器CMP

NUC1XX 系列包含2 路模仿比较器,当正级输入大于负极输入(可挑选内部参阅电压)时,比较器输出为逻辑1,反之为逻辑 0;每一路比较器可装备成:当输入值发生改动时发生间断。软件可 写 0 到 CMP0 位 CMPF1 以间断间断恳求。2路模仿比较器共用同一个间断恳求。

14.USB设备操控器

NUC1xx系列包含一组全速USB 2.0 设备操控器和收发器,契合USB 2.0规范,支撑control/bulk/interrupt/isochronous 传输类型。

在该设备操控器里,包含2个主接口:APB总线和由USB PHY收发器出来的USB总线,CPU经过APB总线编程操控存放器,在该操控器内置有512字节的SRAM作为数据缓存。输入或输出传输,需求经过AHB从接口或SIE向SRAM写数据或从SRAM读数据。用户需求经过BUFSEGx为每个端点缓存设置有用的SRAM地址。在USB功用有用前,用户需求在缓冲段存放器装备每个端点的有用开端地址(地址规模0x4006 0100-0x4006 02ff)。

USB设备操控器具有6个可装备的端点,每个端点可装备为IN或OUT类型。一切的操作包含control,bulk,interrupt,isochronous传输都由断点模块来履行。端点操控模块还能够用来办理数据同步时序,端点状况操控,其时开端地址,其时业务状况和每个端点的数据缓存状况。

该操控器供给1个间断向量、4个不同的间断事情,包含唤醒功用、设备插拔事情、USB事情(如IN ACK,OUT ACK等)和BUS事情(如suspend和resume等),用户需求在间断事情状况存放器(USB_INISTS)查看相关事情标志以得知发生何种间断,然后检测相关USB端点状况存放器(USB_EPSTS)以得知该端点上发生何种事情。总线间断告之用户一些总线事情,如USB复位、间断、暂停、康复,用户能够读特别功用存放器“ATTR”获取总线事情。

USB设备有一个软件禁用功用,用于模仿设备没有跟主机相连的状况。

SIE是设备操控器的前端,处理最多的USB 协议包。处理功用包含:

– 包辨认,处理时序

– SOP, EOP, RESET, RESUME信号检测/发生

– Clock/Data别离

– NRZI 数据编解码与比特填塞(bit-stuffing)

– CRC发生和校验 (for Token and Data)

– Packet ID (PID) 发生和校验/解码

– 串-并/并-串转化

数字锁相环DPLL:USB数据的比特率为12MHz, DPLL选用的48MHz的频率由时钟操控器发生,确认RXDP与RXDM的输入数据,12MHz的比特率时钟也是由DPLL转化来的。

插拔去颤动:USB设备能够进行热插拔操作,为了监测USB设备被拔出的状况,设备操控器供给了硬件去颤动以防止在USB插拔时发生的颤动问题,悬空检测间断发生于USB进行插拔操作的10ms后,用户能够经过读取“FLODET”存放器的值,来应对USB插拔;“FLODET”代表在其时总线上没有经曩昔颤动处理的状况,若用户要经过这个标志来检测USB的状况,则需求增加软件去颤动功用。

当芯片进入掉电形式时,USB 主动封闭PHY省电,此外,在特别环境下,用户能够给特别功用存放器ATTR[4]写入“0”封闭PHY进入省电状况。

与USB外设通讯处理:用户能够选用间断或检测USB_EVF来监测USB通讯,在USB通讯发生时,USB_EVF 由硬件置1,并向CPU发送间断恳求。

USB主机向设备操控器请示数据时,用户需求预备相关的数据给端点缓存. 在缓冲恳求数据后,用户需求写入实践数据长度给MAXPLD存放器。一旦这个存放器被写入数据,内部信号“In_Rdy”会被设置,当收到主机相关的IN token之后,缓冲数据将被马上传送。在传送拟定数据之后,信号 “In_Rdy”会由硬件主动铲除。

USB主机要发送数据到设备操控器的OUT端点,硬件将这些数据存在指定的端点缓存里,通讯完结后,硬件在MAXPLD记载数据长度,并发送“Out_Rdy”信号,这防止硬件在用户没有取走其时数据时接纳下一个数据。一旦用户处理了这个通讯时,由软件写入相关的存放器“MAXPLD”来设置“Out_Rdy” 信号以接纳下一次通讯。

15.I2C 总线操控器 (主机/从机)

I2C 为双线,双向串行总线,I2C 总线上数据的传输速率在规范形式下可达100kbit/s 在快速形式下可达400kbit/s 在高速形式,直至 1.0 Mbit/s 的增强高速形式。

在衔接到总线的器材间传递信息每个器材都有一个仅有的地址辨认。数据在主机和从机间经过SCL时钟线操控在SDA数据线上完结一字节一字节的同步传输,数据由最高位MSB开端传输,每个字节包含8位,每次传输能够发送的字节数量不受约束,每个字节后有必要跟一个呼应位。假如从机要完结一些其他功用后,才干接纳或发送下一个完好的数据。字节能够使时钟线SCL 坚持低电平迫使主机进入等候状况,当从机预备好接纳下一个数据字节并开释时钟线SCL 后,数据传输持续。

片上I2C逻辑供给契合I2C总线规范的串联规范接口,I2C接口主动处理字节传输,将I2CON的ENS1位设置为1,即可使能该端口,I2C H/W接口经过SDA与SCL两个引脚连到I2C总线。用于I2C操作的两个引脚需求上拉电阻,由于这两个引脚为开漏脚,在I/O引脚作为I2C端口运用时,用户有必要预先设置引脚功用为I2C功用。

1)I2C协议

一般规范I2C传输协议包含四个部分:

– 开端信号或重复开端信号

-从机地址传输

-数据传输

-间断信号

2)I2C存放器

NUC1xx共有6个特别功用存放,用于I2C通讯: I2CON(操控存放器 C0H), I2STATUS(状况存放器 BDH), I2DAT(数据存放器 BCH), I2ADDR(包含I2CADDRn和I2CADRMn,地址存放器 C1H), I2CLK(时钟速率存放器 BEH) 和 I2TOC(守时计数存放器 BFH)。存放器的第31位至第8位都是保存的,不具备任何功用。

当ENS1置1,I2C口使能后,内部状况由 I2CON 和 I2C总线上状况操控。当有新的状况发生后,会存储到 I2STATUS, I2C 间断标志(SI) 也会主动置起。若此刻 EI2 被设定为高,I2C间断会被呼应。

3)I2C操作形式

5种操作形式:主机/传输,主机/接纳,从机/传输,从机/接纳和GC 形式。

16.串行外围设备接口(SPI)操控器

SPI接口是作业于全双工形式下的同步串行数据传输接口。共支撑四组双向主/从机形式传输。包含4组SPI操控器,将从外设得到的数据进行串并转化,或将数据进行并串转化,发送到外设。每组SPI操控能够被作为一个主机,驱动最多2个外部从设备,还能够被设置为外围设备的从机。

该主/从机内核包含2组32位输出/输入数据缓存,可支撑突发传输(burst mode)形式,并支撑各种不同长度的变量数据形式,最多可支撑64位数据传输。

该操控器支撑不同串行时钟,支撑1位、2位数据传输形式。支撑MSB 或 LSB 为最早传输形式。支撑2个通道的PDMA恳求,一个用于发送,一个用于接纳。

a.对DIVIDER内写入值,确认传输频率。

b.将主机形式的相应设置写入SSR,设定 ASS = 0, SS_LVL = 0 且SSR[0] 或SSR[1] =1 用以使能模块。

c.将主机形式的相应设置写入存放器SPI_CNTRL。

d.假如SPI主机要发送一个字节的数据到外设,则将所要发送的数据写入存放器SPI_Tx0。

e.假如SPI主机仅仅从外设接纳一个字节的数据,不用管被传输出去的数据是什么,只需向存放器SPI_TX0写入0xff。

f.使能GO_BUSY位(SPI_CNTRL[0]=1),以开端SPI接口的数据传输。

g.比及SPI间断发生,或检测GO_BUSY位直到被硬件主动清0。

h.从存放器SPI_RX0[7:0]读出所接纳到的一个字节的数据。

i.重复过程d,持续其他数据的传输,或设置SSR[0]为0以间断外设。

2)SPI作为从机时

a.设置从机有用电平位SS_LVL(SPI_SSR[2]=1)与从机挑选电平触发位SS_LTRIG(SPI_SSR[4]=1)使从机挑选信号为高电平触发。

b.将从机形式的相应设置写入存放器SPI_CNTRL。

c.假如SPI从机要发送一个字节的数据到SPI主机,则将所要发送的数据写入存放器SPI_Tx0。

d.假如SPI从机仅仅要从外设主机接纳一个字节的数据,不用管被传输的数据是什么,只需向存放器SPI_TX0写入0xff。

e.使能GO_BUSY位(SPI_CNTRL[0]=1),比及外设的从机挑选触发输入和串行时钟输入,以开端SPI接口的数据传输。

f.比及SPI间断发生,或检测GO_BUSY位直到被硬件主动清0。

g.从存放器SPI_RX0[7:0]读出所接纳到的一个字节的数据。

h.重复过程c,持续其他数据的传输,或设置SSR[0]为0以间断外设。

17.I2S 操控器

I2S操控器由IIS协议与外部音频CODEC组成,两个8字的FIFO别离用于读与写通道,能够处理8~32位字巨细。DMA操控器处理数据在FIFO与内存之间传输,两个DMA恳求,一个用于发送,一个用于接纳。

I2S 可作业于8位主机或从机,支撑单声道和立体声的音频数据.支撑I2S和MSB 校验数据格局.当缓冲超越可编程鸿沟时,发生间断恳求.

18.PS2设备操控器(PS2D)

PS/2 设备操控器为 PS/2通讯供给根本时序操控。在设备和主机之间的通讯CLK 和 DATA pins操控. 不同于 PS/2 键盘和鼠标设备操控器, 接纳/传输代码需求固件进行代码转化成有意义的代码。主机发送到设备的数据是在上升沿读取,设备发送到主机的数据在上升沿之后被改动。可编程1~16 位传输缓冲 以削减CPU 搅扰。支撑双数据缓冲功用。

PS/2 设备具有 双向双向同步串行协议,当总线为 “Idle” 形式而且两条线都为高 (open-collector),该状况为设备答应开端 DATA 传输的仅有条件。主机在总线上有终究的操控权 ,比呢且任何时分都能够经过下拉CLK line制止通讯。设备一向发生CLK信号,假如主机需求发送 DATA, 下拉CLK line 为低,制止从设备进行通讯。主机随后将DATA拉低而且开释CLK,这是”Request-to-Send” 状况,告诉设备开端发送CLK脉冲。一切数据每次传输1字节,每字节包含11-12位:1 开端位(一向为 0);8 数据位(先最低位);1 奇偶位(odd parity);1 间断位(一向为1);1 应对位(主机~设备通讯)。

设备向主机传输,设备运用于接连的 11-位 架构:1 个开端位(一向为 0);8 数据位(最高位最早传输);1奇偶位(odd parity);1间断位(一向为1)。

主机向设备传输:首要,PS/2 设备一向发生 CLK 信号,假如主机期望发送DATA, 首要需设定CLK 和 DATA在 “Request-to-send” 状况:拉低CLK 至少100 us 制止通讯;运用 “Request-to-send” 拉 DATA 为低, 开释CLK。设备在不超越10 ms时刻内需不间断的监控状况,当设备监控到此状况,将开端发生CLK 信号和8位DATA位 1 位间断位。当CLK line为低时,主机改动DATA line,当CLK为高时设备读数据。间断位接纳后,设备宣布应对信号,使DATA line 为低 而且发生CLK 脉冲。

写PS2TXDATA0 存放器将触发设备和主机通讯,在向TX FIFO传输数据前,S/w 需界说TXFIFO 长度。写PS2TXDATA0 存放器后100us,第一个字节的start bit 才会被传送到总线上。

19.局域操控网络总线(CAN Bus)

区域操控器 (CAN) 为串行通讯协议 具有多主机(multi-master) 和高效率实时操控功用,安全功能高 成本低,运用于高速网络,在轿车电子, 车身操控, 传感器, 防滑体系等。CAN 衔接速度可达 1Mbit/s。CAN 2.0B 协议兼容。

总线上信息发送为固定形式.当总线空闲时, 任何的衔接单元可进行数据传递.

1. A DATA FRAME 数据从传输到接纳的运送.

2. A REMOTE DATA FRAME 经过总线单元向传输DATA FRAME IDENTIFIER发送恳求.

3. An ERROR FRAME 传输经过 任何单元侦测总线 error.

4. An OVERLOAD FRAME 运用于供给额定延时 在其时和随后 DATA 或 REMOTE FRAMES 之间.

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/changshang/fabu/275627.html