间断和反常的差异:间断时从外至内的, 反常时由内宣布的

一、存储器格局(字对齐):

Arm体系结构将存储器看做是从零地址开端的字节的线性组合。从零字节到三字节放置第一个存储的字(32位)数据,从第四个字节到第七个字节放置第二个存储的字数据,一次摆放。作为32位的微处理器,arm体系结构所支撑的最大寻址空间为4GB。

存储器格局

1、大端格局:高字节在低地址,低字节在高地址;

2、小端格局:高字节在高地址,低字节在低地址;

指令长度:

Arm微处理器的指令长度是32位的,也可认为16位(thumb状况下)。Arm微处理器中支撑字节(8位),半字(16位),字(32位)三种数据类型,其间,字需求4字节对齐,半字需求2字节对齐。

注:所谓的指令长度是一条完好的指令的长度,而不是单纯的mov这3个字母长度

二、ARM体系的CPU有两种作业状况

1、ARM状况:处理器履行32位的字对齐的ARM指令;

2、Thumb状况:处理器履行16位的、半字对齐的Thumb指令;

在程序运转的过程中,能够在两种状况之间进行相应的转化。处理器作业状况的改动并不影响处理器的作业形式和相应寄存器中的内容。

CPU上电处于ARM状况

三、ARM体系的CPU有以下7种作业形式:

1、用户形式(Usr):用于正常履行程序;

2、快速间断形式(FIQ):用于高速数据传输;

3、外部间断形式(IRQ):用于一般的间断处理;

4、管理形式(svc):操作体系运用的维护形式;

5、数据拜访停止形式(abt):当数据或指令预取停止时进入该形式,可用于虚拟存储以及存储维护;

6、体系形式(sys):运转具有特权的操作体系使命;

7、未定义指令间断形式(und):当未定义的指令履行时进入该形式,可用于支撑硬件;

ARM Context-A*架构的有8中形式

这儿所指的片内寄存器是指CPU内部的寄存器, 而操控GPIO的寄存器归于外设。

参阅:http://infocenter.arm.com/help/index.jsp arm官网对应系列文档

Arm的作业形式切换有两种办法:

被迫切换:在arm运转的时分产生一些反常或许间断来主动进行形式切换

主动切换:经过软件改动,即软件设置寄存器来经行arm的形式切换,应为arm的作业形式都是能够经过相应寄存器的赋值来切换的。

Tips:当处理器运转在用户形式下,某些被维护的体系资源是不能被拜访的。

除用户形式外,其他6种作业形式都归于特权形式;

特权形式中除了体系形式以外的其他5种形式称为反常形式;

大多数程序运转于用户形式;

进入特权形式是为了处理间断、反常、或许拜访被维护的体系资源;

四、寄存器

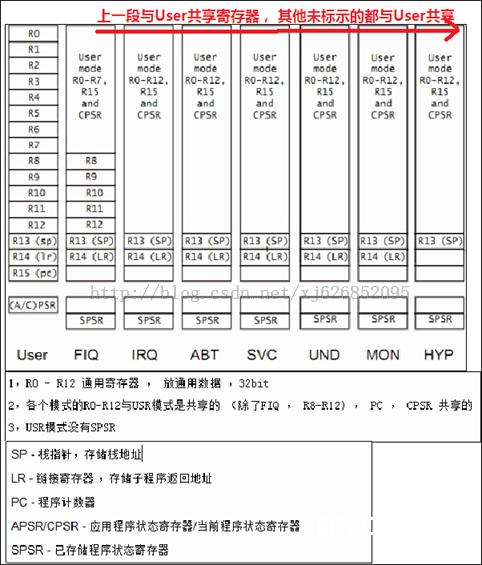

ARM有31个通用的32位寄存器,6个程序状况寄存器,共分为7组,有些寄存器是一切作业形式共用的,还有一些寄存器专归于每一种作业形式;

R13——栈指针寄存器,用于保存仓库指针;

R14——程序衔接寄存器,当履行BL子程序调用指令时,R14中得到R15的备份,而当产生间断或反常时,R14保存R15的回来值;

R15——程序计数器;

快速间断形式有7个备份寄存器R8—R14,这使得进入快速间断形式履行很大部分程序时,乃至不需求保存任何寄存器;

其它特权形式都含有两个独立的寄存器副本R13、R14,这样能够令每个形式都具有自己的仓库指针和衔接寄存器;

五、当时程序状况寄存器(CPSR)

CPSR中各位含义如下:

T位:1——CPU处于Thumb状况, 0——CPU处于ARM状况;

I、F(间断制止位): 1——制止间断, 0——间断使能;

作业形式位:能够改动这些位,进行形式切换;

六、程序状况保存寄存器(SPSR)

当切换进入某一个特权形式时,SPSR保存前一个作业形式的CPSR值,这样,当回来前一个作业形式时,能够将SPSR的值康复到CPSR中;

七、形式切换

当反常产生,CPU进入相应的反常形式时,以下作业是由CPU主动完结的:

1、在反常形式的R14中保存前一作业形式的下一条行将履行的指令地址;

2、将CPSR的值到反常形式的SPSR中;

3、将CPSR的作业形式设为该反常形式对应的作业形式;

4、令PC值等于这个反常形式在反常向量表中的地址,即跳转去履行反常向量表中的相应指令;

从反常作业形式退回到之前的作业形式时,需求由软件来完结以下作业:

1、将反常形式的R14减去一个恰当的值(4或8)后赋给PC寄存器;

2、将反常形式SPSR的值赋给CPSR;

ARM 有七种反常,当反常产生时,ARM core 会主动履行 Vector Table 中的指令。

ARM 的七种反常及在 Vector Table 种的偏移:

|

反常 |

形式 |

向量表偏移 |

|

复位(reset) |

SVC |

+0x00 |

|

未定义指令 |

UND |

+0x04 |

|

软件间断(SWI) |

SVC |

+0x08 |

|

预取指停止 |

ABT |

+0x0c |

|

数据停止 |

ABT |

+0x10 |

|

未分配 |

— |

+0x14 |

|

IRQ |

IRQ |

+0x18 |

|

FIQ |

FIQ |

+0x1c |

ARM V4 以下版别 Vector Table 的地址为 0x00000000,V4 以上版别 Vector Table 地址可在 0x00000000,0xFFFF0000 间进行挑选。

ARM 构架下,间断为反常的一种。以间断为例,当接纳到间断后,ARM core 首先将当时形式下的 CPSR,PC 寄存器别离保存到反常形式下的 SPSR,LR 寄存器,然后将方针形式的 PC 寄存器值设为地址 0x00000018(或0xFFFF0018),最终切换到方针形式—-即 IRQ 形式。切换到方针形式后履行的第一条指令就是地址 0x00000018(或0xFFFF0018)上的指令。此处一般为一个跳转指令,用于跳转履行间断处理函数。其它反常处理方式相似。

S3C6410 中有个 32KBIROM(internel ROM),里边固化了一段程序。其最初就是一个 Vector Table。以 IROM 形式启动时,IROM 被映射到 0x00000000 方位,所以履行的第一条指令就是 Vector Table 中的 Reset 反常跳转指令(ARM core 上电时在 0 地址取第一条指令)。咱们能够使用此 IROM 的反常向量表完成 u-boot 下的间断处理。

刚上电,初始化间断,使S3C6410 能接纳并处理间断。间断产生后,先履行 0x00000018 中的反常跳转,转去履行 IROM 中的间断处理函数。此处理函数很简单:将 0x0C001FF8 (落于 SRAM 地址规模)处的值赋给 PC。所以,咱们可将咱们自己的间断处理函数的进口地址存于 0x0C001FF8 处,当间断产生后,便会主动调用咱们的间断处理函数。其它反常的完成办法相似,仅仅 0x0C001FF8 要改成其他值。详细为何值,需剖析 IROM 中的代码。

S3C6410 IROM 的反汇编代码,能够在网上查找到。或许也能够自己提取进行反汇编。