1 导言

自发生到现在,现场可编程门阵列(FPGA)以其共同的长处被成功运用在工业操控、数据通讯、计算机硬件等范畴,也成功运用在保密通讯和多种先进的武器体系中。我国在FPGA的开发方面起步较晚,开发具有自主知识产权的FPGA具有重要意义。各种运用条件要求FPGA能够快速进行很多数据传输与处理,一起,不断进步的工艺水平已将CMOS电路速度进步到了一个新的层次,这要求FPGA的时钟信号有更高的速度与精度。时钟分配网络决议了时钟的速度与精度,决议着数据的安稳与牢靠。本文结合FPGA的特色,在优化时钟网络功耗与面积基础上研讨FPGA内嵌时钟锁相电路,从全体上给出了一种FPGA时钟分配网络规划计划。

2 FPGA的时钟布线结构

高功用的FPGA可用于完结一个完好的体系,体系有不同组成部分,每一部分需求不同的时钟,这就需求多个时钟组成时钟网络。许多FPGA答应运用通用逻辑布线资源进行时钟布线,但其时钟差错较大,一般规划中需独自设计时钟网络。别的,时钟网络的功耗占了FPGA的很大一部分,规划时要先考虑功耗、面积,严厉规划以给FPGA中的每个模块供给低功耗、高速、差错小的时钟信号。一般FPGA均将时钟信号分为大局和部分两种,把芯片分为四个象限区域,布线时将时钟信号分层次布到每个区域。部分时钟只散布在FPGA的一个区域,可连到区域中的每一个触发器。大局时钟散布于整个芯片,但不一定要连到每一个逻辑单元中的触发器。Altera 公司的Stratix Ⅱ系列供给了16个大局时钟信号,可连到FPGA的每一个触发器,一起在每个象限区域供给8个时钟信号。相同,Xilinx的Virtex Ⅱ Pro也供给了16个大局时钟,给每个象限区域供给8个部分时钟,但其大局时钟不直接驱动触发器,而只驱动到每个象限的部分时钟网。

依据现有的FPGA的时钟网络,可提出一个有用的时钟模型。 模型将时钟网络分为三级,榜首级是从芯片外围的时钟源届时钟区域中心的可编程衔接,包括大局和部分两个平行的时钟网络;第二级是从区域中心时钟信号到此区域中逻辑块间的可编程衔接,每个区域都有这样的网络;第三级(图3)是从逻辑块时钟到其间逻辑单元的可编程衔接。

图1示范性的将FPGA芯片分成了9个区域,时钟源置于芯片四周,芯片的每一边布有四分之一的时钟源,大局时钟从每一边的时钟源引到FPGA中心,再经过H树连到每个区域的中心。部分网络从与本区域最附近时的芯片两头挑选部分时钟源,将其连到区域中心。每个区域的逻辑块经过SRAM操控的多路挑选器能够灵敏的挑选运用大局或是部分时钟(见图2)。此方法中,FPGA可支撑多个置于芯片周围的时钟源,一起经过约束芯片中每一区域能一起运用的时钟数,有用减少了整个时钟分配网络的杂乱性,而对功用影响较小。

运用这个模型可将时钟网络的组成单元如时钟源数,大局和部分时钟数,时钟区域数等参数化,然后研讨参数改变对芯片面积及功耗的影响,由此能够得出一个功耗与面积优化的时钟网络结构[3]。

3 运用锁相环的时钟分配结构

一般在速度不高,芯片的杂乱度不是很高的情况下,经过挑选适宜的时钟分配网络就可得到满足要求的FPGA时钟。跟着杂乱度与速度的进步,因温度、工艺参数或电源电压改变所引起的时钟差错严重影响FPGA的作业。此刻需在FPGA时钟网络结构中规划锁相环将时钟信号确定在安稳的参阅频率上,消除分配网络的时钟差错,使芯片中的触发器能精确地同步作业。一起,运用锁相环的频率组成功用,FPGA芯片内部可作业在一个较高的频率上,而外部接口作业于较低频率,这样进步了芯片的数据处理才能又不添加板级接口的完结难度。

在FPGA中,时钟沿在各个寄存器的相对抵达时刻决议了芯片能否精确作业,而时钟沿到寄存器的肯定延时时刻则对体系功用影响不大。规划时一般关怀时钟分配途径的相对延时,坚持时钟沿在同一时刻抵达寄存器。这种特色使得锁相环在时钟分配网络中得以运用,锁相环使得时钟延时为一个周期的整数倍,确保了不同寄存器处的时钟能同步。

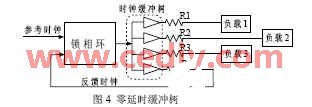

在时钟分配中运用锁相环的技能称为零延时缓冲(Zero-Delay Buffer)技能。其原理如图4所示[4]。图中将时钟缓冲树(clock tree)结构中的一个时钟信号回馈到锁相环与参阅时钟进行相位比较,依据差错调理相位将负载时钟与参阅时钟对齐,完结了时钟信号到负载的零延时。图中R1-R4为接近缓冲树端的电阻用于匹配负载连线的特征阻抗,确保了信号完好性。规划时在工艺上坚持负载连线与反应连线长度共同可减小时钟差错。

4 锁相环的完结

在FPGA中一般可用模仿锁相环(PLL)或数字推迟锁相环(DLL)来完结时钟信号的组成。PLL运用相位差错操控可发生时钟的压控振荡器(VCO),使其输出时钟信号与参阅时钟信号的相位对齐。而DLL没有VCO,不发生时钟,它是经过可控的延时单元来调整延时时刻,完结相位对齐。

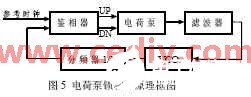

模仿锁相环可用电荷泵锁相环(CPPLL)来完结,实质上它归于混合信号锁相环[5](Mixed Signal PLL)。其由鉴相器发生相位差错电压,运用电荷泵累积差错电压,滤波后操控压控振荡器发生与外部时钟同步的信号。其原理框图如图5所示。

图中分频器用来完结时钟信号频率组成,能够使时钟作业在N倍的参阅频率上。文 [6]给出了此类锁相环的具体完结进程。

一般情况下PLL需求高阶滤波器,其安稳性规划较杂乱,一般在特殊要求的场合运用。而DLL一般只需求一阶滤波,且体系的阶数便是滤波器的阶数,规划相对简略。另一方面, FPGA中晶体管的切换使得芯片内部存在很大的电源噪声,传统的PLL运用的压控震动器(VCO)对噪声与颤动有堆集效果,易受搅扰; DLL不运用VCO,对噪声无累积效果,可按捺噪声,且在工艺、电压和温度(PVT)改变时作业较安稳[9]。因而,FPGA中更倾向于用纯数字构成的DLL调整时钟差错,市场上Xilinx 的Spantan Ⅱ和Virtex系列均运用数字DLL[10]。

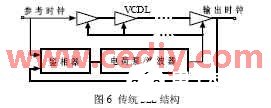

传统的DLL原理如图6所示。电路包括压控推迟线(VCDL),鉴相器,电荷泵,滤波 器。VCDL由参阅时钟驱动,它只运用末级输出时钟与参阅时钟进行相位比较,发生输出差错电压,再由电荷泵累加、滤波器滤波后发生VCDL的操控电压,由此调整延时,将输出时钟与参阅时钟相位对齐。正确锁守时VCDL的总延时为参阅时钟的一个周期。

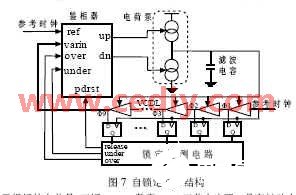

实践工程规划中,可将VCDL中每一级延时单元的输出信号均作为反应信号,完结杂乱的操控,增强DLL环路功用。图7是在传统结构了添加了确定检测电路的DLL,图中的VCDL用了9级延时缓冲,每一级的输出在参阅时钟上升沿被锁存,确定检测电路依据锁存的信号发生相应于延时过长(过延时)、延时过短(欠延时)以及延时正常的信号,鉴相器依据确定检测电路的这些信号开释操控或许操控电荷泵充放电。具体来说,图中确定检测电路对VCDL末级的延时进行判别,如其大于1.5个参阅时钟周期,则发生过延时(over)信号;小于0.75个参阅时钟周期,则发生欠延时(under)信号;末级延时到达1.25个参阅时钟周期时发生代表延时正常的release信号。鉴相器一旦检测到 over或许under信号,它立行将操控交给确定检测电路,由over或under信号直接操控电荷泵的充放电。当release信号被检测届时,鉴相器复位over与under信号,比较参阅时钟与VCDL末级输出的相位,依据相位差错操控电荷泵的充放电。运用此原理构成的DLL电路能够避免环路确定到2倍以上的参阅时钟周期,环路的捕捉规模更大,响应速度更快,一起发生的颤动更小[7]。别的,在此结构上添加一些逻辑电路便可进行频率组成,最大频率可达9倍的参阅时钟频率[7]。

这种DLL已很好的在单晶-三铝-0.5um数字CMOS工艺中完结,具有颤动小,作业安稳,最高频率可达1Ghz.[8]

5 定论

在一个可优化功耗与面积的布线结构模型基础上,将数字推迟锁相环引进时钟分配网络,有用处理了网络的时钟差错。一起按捺了噪声,使FPGA作业安稳,颤动小。

本文作者立异点:在时钟网络布线结构中引进自确定数字推迟锁相环减小时钟差错,给出了一个有用的时钟网络规划计划。

责任编辑:gt