近年来,跟着信息化技能以及物联网的开展,关于视频监控设备的要求不断的在进步,将高动态规模(High Dynamic Range,HDR)摄像机替代传统摄像机以进步监控质量成为了监控设备的开展趋势。TI公司达芬奇视频处理技能在网络摄像机视频监控方面的成功运用,使得DM36X芯片与其他芯片比较具有低功耗、小尺度、低成本、高性能等特色。但因为高动态摄像机的数据量非常大,一起对图画处理的要求也很高,这就增加了体系的杂乱性。要一起满意高质量的视频图画处理作用和实时传输,单凭DM36X的处理才能已远不行,且DM36X内部的视频处理算法已固定,很多优异的图画处理算法无法及时的增加进去,这也对DM36X图画处理才能的晋级形成了必定的困难。而FPGA芯片处理速度快、灵敏性高,可依据各种优异算法进行较好的规划,所以体系选用FPGA进行前端HDR视频图画增强预处理部分,由此可在较大程度上削减DM36X的作业量,补偿其在高动态视频处理上的缺乏,使DM36X能彻底发挥高速编码和传输效的特色,满意体系实时性要求。将FPGA和DM36X一起运用在网络摄像机渠道中可充分发挥各自的优势。这种规划不只使得体系在日后扩大和再次开发上供给了满足的灵敏性,且有利于整个体系的晋级与保护。

本体系是在TI公司依据达芬奇技能TMD320DM36X处理器的IP Camera计划根底之上建立依据FPGA+DM36X的IP摄像机渠道,选用高动态网络摄像机MT9M034进行图画收集,以FPGA +DM36X作为HDR视频图画增强、编码和传输处理中心,终究完结用户经过长途PC机客户端上观看1 280×720分辨率,每秒30帧的实时视频。

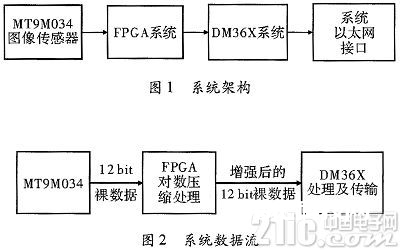

1 总体计划

体系架构如图1所示,MT9M034收集HDR视频信号,FPGA担任对HDR视频图画进行增强处理,DM36X担任对增强后的HDR图画进行编码传输等处理。

体系3部分之间的数据流如图2所示。

图画传感器MT9M034经过装备后输出动态规模为120 dB的HDR图画。图画数据的位宽是20 bit,可选择性的紧缩成12 bit或14 bit。因为DM36X处理才能的约束,在本体系中将传感器输出数据位宽设置为12 bit,这就会形成图画数据的丢失。所以本计划在原IP Camera的根底之上增加了FPGA体系,可依据需求灵敏增加底层的图画处理算法。首要图画传感器输出的视频数据在FPGA上进行捕获和对数紧缩等处理,到达对图画增强的作用。然后再将这12位裸数据传输给DM36X体系,并在DM36X体系中完结颜色空间转化、伽马校对、RGB转YUV、边缘增强等一系列处理。终究将处理过的视频图画数据以H.264规范紧缩后经过以太网接口传送到TCP/IP网络,完结用户经过长途PC机客户端上实时监控视频。

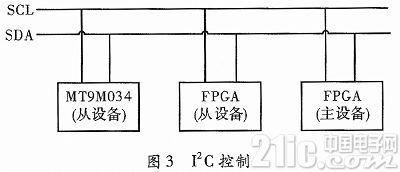

MT9M034(从设备)、FPGA(从设备)、DM36X(主设备)之间经过I2C总线进行通讯。DM36X作为主设备不只可经过I2C总线对MT9M034进行装备,还可对FPGA进行简略操控,如图3所示。

原DM36X IPNC的驱动程序是针对MT9T031传感器规划的。而本体系中选用的图画传感器是MT9M034。MTM034和MT9T031虽均是美光公司推出的图画传感器,寄存器位宽均为16 bit,但其寄存器编址位宽是有不同的,MT9T031传感器的寄存器编址是8 bit,而MT9M034传感器的寄存器编址是16 bit。为了使DM36X能对MT9M034传感器进行装备,需求对DM36X的驱动进行移植。

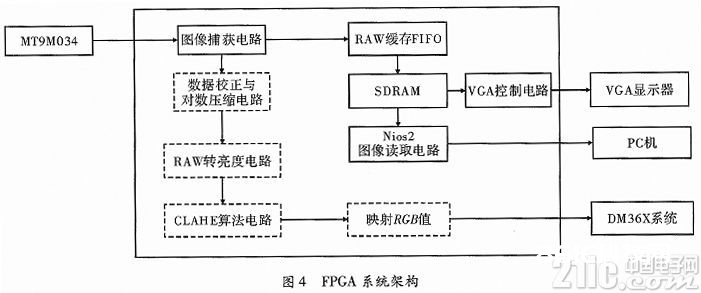

2 FPGA硬件电路规划

如图4所示,在FPGA上需求规划的电路包含图画捕获电路、数据校对电路、RAW转亮度电路、CLAHE色彩映射电路和用于调试图画传感器的VGA显现电路。

DM36X将MT9M034装备好并发动后,图画传感器会输出12 bit的HDR图画数据,这些数据直接进入图画捕获电路模块,此模块首要是对数据进行符号和对行、列、帧等进行核算,为后边的电路规划供给必要的参数。MT9M034图画传感器经过分段性掩盖整个亮度域的3次曝光组成一副20 bit位宽的HDR图画,并将20 bit亮度分三段折线模仿对数紧缩到12 bit输出,增加了传感器的实时性。因为一般的显现器只能显现8 bit数据,所以需求色彩映射算法将HDR图画紧缩成8 bit低动态规模图画(Low Dynamic Range Image,HDRI)这样既可坚持图画全体明暗作用,又可使图画的细节部分很好的表现出来。因为传感器内部的三段线性紧缩和规范的对数紧缩曲线之间具有必定的距离,会使原HDR图画丢失许多的细节信息,若直接进行色彩映射算法的处理的话会影响图画的对比度,所以在进行色彩映射之前需求进行对数据进行校对,最大程度上消除传感器三段线性紧缩形成的差错,然后在进行对数紧缩这样就可将整个图画的亮度紧缩到一个较小的规模内,终究在经过色彩映射算法完结图画作用的增强。因为时刻原因在FPGA中仅完结图画的抓取电路,经过Nios2图画抓取电路向PC机中存入一帧图画用于图画作用的调试,其间抓取的图画每个像素位宽是12 bit裸数据,在Matlab中进行显现,如图5所示。

3 MT9M034驱动移植

3.1 传感器特性

MT9M034传感器是美光公司推出应用于安防范畴的高动态规模图画传感器。该传感器具有大局运动补偿功用,最高可供给每秒45帧下1 280×960分辨率的视频拍照,支撑线性形式和高动态规模形式。传感器具有并行和串行差分两种数据输出接口。并行接口数据速率低,概念简略,便于完结,在本体系中选用并行接口,在后续开发中为了进步速度可考虑选用差分串行接口。

3.2 DM36X的I2C驱动移植

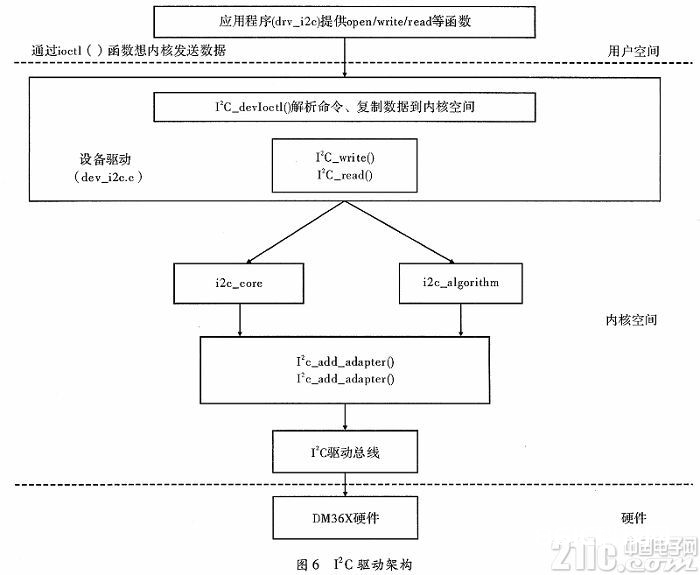

I2C(Inter-Integrated Cireuit)总线是由Philips公司开发的一种同步串行总线协议,其是一种多向操控线,可让多个芯片衔接到同一总线结构上一起施行数据传输。DM36 X的I2C驱动架构如图6所示。

首要应用程序drv_i2c.c依据不同传感器的参数,将寄存器个数、寄存器地址位数寄存器值位数等装备信息存储在I2C_TRansferPrm结构中,其次经过I2C_IOCTL_CMD_MAKE()函数将这些详细的寄存器信息生成相应的指令。这些指令由ioctl()函数传递给内核空间中的设备驱动dev_i2c.c,在设备驱动程序中I2C_dev.Ioctl()函数对将对指令进行解析,依据不同的指令进行不同的操作,这儿较为重要的两个指令是:(1)I2C_CMD_SET_DEV_ADDR,设置设备地址;(2)I2C_CMD_WRITE将用户空间的装备信息复制到内核空间,并存

储在I2C_TransferPrm结构中。终究经过I2C_write()、I2C_read()函数调用I2C_transfer()将数据宣布。在I2C_write()、I2C_read()中都是以I2C_msg作为传输单元的。

struct I2C_msg {

_u16 addr;从设备地址

_u16 flags;标志位,区别读写等

_u16 len;音讯单元长度

_u8 * buf;数据缓存,存储发送数据或许接纳数据。

};

I2C_write()、I2C_read()函数的首要作业便是设置I2C_msg,将寄存器地址(regAddr)和寄存器值(regValue)写入I2C_msg的数据缓存buf中,并调用I2C_transfer进行数据传输,到达对传感器寄存器装备的意图。

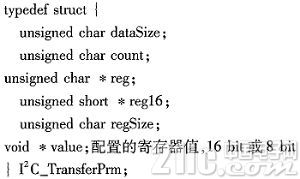

依据以上剖析可知,将I2C驱动移植到MT9M034上,只需修正应用程序drv_i2c.c和设备驱动程序dev_i2c.c即可,I2C_core及以下部分的内容归于内核部分,其接口都是一致针对Davinci渠道下的,故无需进行剖析和修正。因为MT9M034的寄存器是16 bit编址,故需增加16 bit寄存器读写函数DRV_i2cWrite16()、DRV_i2cRead16()。另外在I2C_Tra nsferPrm结构中增加16 bit寄存器地址指针;并且为了便利区别16 bit寄存器和8 bit寄存器,增加寄存器巨细成员regSize。

在drv_i2c.c中增加I2C_write16()、I2C_read16()函数,这两个函数与I2C_write()、I2C_read()类似。只是在I2C_msg的数据缓存中存入regAddr[15:8]、regAddr[7:0]、regValue[15:8]、regValue[7:0],使I2C可读写16位数据。经过以上修正,I2C的驱动程序移植完结。

3.3 DM36X前端的驱动移植

I2C驱动移植完结后仅可使DM36X对图画传感器进行装备作业,为使DM36X成功接纳来自传感器的视频数据,还需求对DM36X的视频处理前端(Video Processing Front End,VPFE)驱动进行相应的修正来增加新的传感器驱动程序。DM36X的DVSDK中已对VPFE驱动做了屡次封装,将与图画传感器相关的代码阻隔到了用户区,这样便利用户对源程序进行修正和移植,并依据不同的需求来增加已知类型的CMOS图画传感器驱动。经过对VPFE源程序的修正完结两个功用,一方面依据视频图画的分辨率和帧率等信息向DM36X驱动供给寄存器的装备信息,另一方面为MT9M034传感器供给以I2C为接口的操控和装备功用。

4 测验成果

保证硬件电路衔接正确并上电后,将编译好的程序下载到DM36X中发动,翻开长途PC机终端敞开网页客户端或许VLC播映器输入用户名和暗码,可显现1 280×720分辨率每秒30帧的视频图画,阐明DM36X的驱动移植正确,并经过I2C总线将传感器装备成功。本体系的测验成果如图7所示,从图中可观察到在室内和室外光照强度相差较大的情况下,室内暗处和室外亮处的景象均可被观察到,具有较高的动态规模,保留了场景中绝大部分的细节,充分表现了本IP Camera的优势。

5 结束语

在安防范畴,关于视频监控设备的要求不断的进步,本文是依据FPGA和DM36X联合硬件渠道开发的一款高动态规模网络监控摄像机,经过对DM36X视频前端驱动的剖析和移植,已完结DM36X对整个渠道的操控作业,并完结1 280×720分辨率每秒30帧的实时播映。较传统的网络摄像机可更好地应对杂乱光照场景,然后拍照出较高动态规模的视频印象,使场景中更多的细节可被观察到,关于进步安防监控才能有着重要的含义。因为图画传感器输出的数据是由20 bit紧缩到12 bit的,形成图画数据有必定的丢失,对比度较低,为了补偿这些缺乏,在体系中增加了FPGA体系,因为时刻联系FPGA部分只完结图画抓取电路的规划,后续的开发中将要点对其他模块进行硬件完结,完善整个图画收集处理体系。