时刻的精确和一致是变电站自动化体系的最基本要求。只要电力体系中的各种自动化设备(如毛病录波器、继电维护设备、RTU微机监控体系等)选用一致的时刻基准,在发生事端时,才干依据毛病录波数据,以及各开关、断路器动作的先后顺序和精确时刻,对事端的原因、进程进行精确剖析。一致精确的时刻是确保电力体系安全运转,进步运转水平的一个重要措施。全球定位体系(GPS)的呈现为完成这些需求供给了或许。

依据GPS的对时办法有3种:1)脉冲对时办法;2)串行口对时办法;3)IRIG-B时刻编码对时办法。脉冲对时和串行口对时各有优缺点,前者精度高可是无法直接供给时刻信息,而后者对时精度比较低。IRIG-B码对时办法统筹了两者的长处,是一种精度很高而且又含有肯定的精确时刻信息的对时办法,选用IRIC-B码对时,就不再需求现场总线的通讯报文对时,也不再需求GPS输出很多脉冲节点信号。国家电网公司发布的技术规范中明确要求新投运的需求授时的变电站自动化体系间隔层设备,原则上应选用IRIG-B码(DC)办法完成对时。

1 继电维护设备对时计划

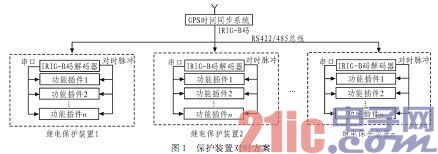

一个变电站内装备一套时刻同步体系,该时刻同步体系可由一面或多面时钟设备屏组成。时问同步体系的结构可选用主从式或主备式结构。时刻同步体系与被授时的继电维护设备之间选用EIA RS-422/485接口规范来传输IRIG-B(DC)码信号。不同厂家的维护设备仅需具有EIA RS422/485接口的IRIG-B码解码器,即可接入变电站一致对时网络。维护设备内嵌IRIG-B码解码模块,选用图1中的对时形式,即由 IRIG-B码解码模块检测出时刻信息和对时脉冲,经过串口将时刻信息直接下发到各个功用插件。各功用插件都直接从对时模块引进对时脉冲。

2 IRIG-B码解码模块的硬件规划

前期的B码解码设备多选用TTL%&&&&&%与单片机相结合的办法来完成,运用门电路和触发器从编码信号中提取出秒同步信号,而用单片机完成时刻信息的解码。现在该办法仍在运用,但该办法存在器材较多,结构杂乱,牢靠性差、同步精度不高、通用性差、不利于功用扩展等问题。

为了处理上述问题,在本规划中,选用CPLD芯片来完成IRIG-B码的解码,选用的是Altera公司的EPM3256。开发仿真软件选用的是 MAX+PLUSⅡ,它能够进行原理图修改和VHDL言语修改,并支撑这些修改办法的混合规划。在本规划中运用VHDL言语进行底层模块的规划,用原理图进行上层模块的规划。该软件具有门级仿真功用,能够进行功用和时序仿真,而且支撑方针程序在线下载。

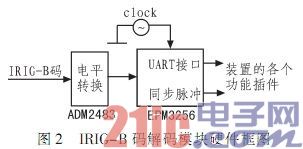

外部接入的IRIG-B编码信号是用 RS485电平传输的差分信号,需变换为TTL信号,转化芯片为AD公司的ADM2483,该芯片是带阻隔的增强型RS485收发器,有失效维护、短路电流约束、热关断和康复等功用。外接的5 MHz信号来源于5 MHz的有源晶振。硬件框图如图2所示。

3 IRIG-B码解码模块的软件规划

3.1 IRIG-B码原理

IRIG(Inter Range Instrumentation Group)码是美国靶场司令委员会拟定的一种时刻规范,共有4种并行二进制时刻码格局和6种串行二进制时刻码格局。其间最常用的是IRIG-B时刻码格局。B码能够分为直流(DC)码和沟通(AC)码,沟通码是1 kHz的正弦波载频对直流码进行起伏调制后构成的;直流码选用脉宽编码办法。每秒1帧,含100个码元,每个码元宽度为10ms。码元有3种,方位标识符的脉宽是8ms(方位标识P0~P9和参阅标志Pr),二进制“1”和“0”的脉宽别离为5 ms和2ms。

每帧从参阅标志Pr开端,也便是接连两个8 ms脉冲中的第2个8 ms脉冲的前沿开端,别离为Pr,第0,1,…,99码元。在Pr和P5之间是BCD字段,传送的是BCD码格局的时刻信息(包含秒、分、时、天4种信息),低位在前,高位在后;个位在前十位在后。在P5和P8之间是CF字段,完成操控功用,可依据实际运用时的协议拟定运用办法,在这里没有用到该字段。在P5和P8之间是SBS字段,是用二进制表明的以秒(s)为单位的时刻信息。IRIG-B码的格局如图3所示。

3.2 IRIG-B码解码计划

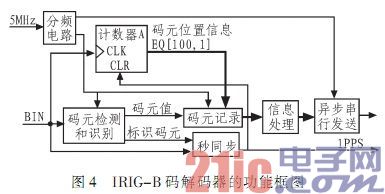

IRIC-B码解码器的功用框图如图4所示。

1)分频电路本模块的功用是将5 MHz的时钟信号进行分频处理,输出1 000 Hz和9 600 Hz的信号,为码元检测和辨认单元、码元记载单元和异步申行发送单元供给时刻基准。为了削减计数器的位数进行了屡次分频。

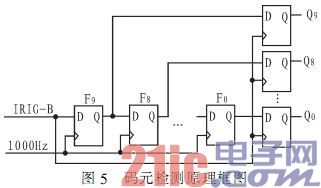

2) 码元检测和辨认单元首要对B码信号进行串并转化。用10个D触发器串联,用1 000Hz的时钟信号作为它们的时钟,这样只要在1 000 Hz的时钟信号的上升沿来的时分才对输入的数据进行输出,其他时分处于坚持本来输出不变。串行触发器的输出别离连到10个并行D触发器,由IRIG-B码的上升沿来操控并行D触发器的输出Q9~Q0。当并行D触发器的输出“Q9Q8Q7Q6Q5Q4Q3Q2Q1Q0”为“0011111111”时,对应的码元信息为标识位;同理,“0000011111”对应码元“1”,而“0000000011”对应码元“0”。码元检测原理框图如图5所示。

3) 秒同步脉冲的发生依据码元辨认成果,假如接连检测到两个标识位,则第2个标识位便是参阅标志Pr,其前沿为秒同步脉冲的起始点。而参阅标志Pr后第1个上升沿对应的是秒同步脉冲经过延时10ms的时刻,所以应该在参阅标志Pr后第1个上升沿对应时刻再延时990ms来发生秒同步脉冲信号,在发生秒脉冲的一起把记载码元方位信息的计数器A清零。

4)码元记载单元码元记载单元依据码元辨认成果和码元方位来组合发生时刻信息,包含7位秒信息、7位分信息和6位时信息。

5)信息处理由于当时解出的时刻是上一秒的时刻信息。信息处理单元要将解码后的时刻加上1 s,一起为便于后续时刻信息的传输和处理,要将时刻信息转化成BCD码格局。

6)异步串行发送异步串行发送模块便是把经过处理后的时刻信息经过异步串口发送出去,速率是9 600 bit/s,8位数据位,无校验位,1位中止位。

4 结束语

IR%&&&&&%-B码对时有利于简化回路规划,而且能够牢靠地供给精确的时刻信息,必将在电力体系中得到日益广泛的使用。

传统的IRIG-B码解码器大多选用单片机来完成,器材较多,结构杂乱,在遭到外界搅扰的情况下还或许呈现死机等毛病。而选用CPLD规划的解码器能够大大削减器材的数量、添加解码器的安稳性和使用的灵活性。依据本计划规划出的解码器模块适用于各种电压等级的维护设备,功能牢靠安稳,时刻信息精确、对时脉冲精度高(差错为几μs)。