视频监控和安全职业正在阅历着一场巨大的革新,正在从传统的模仿闭路电视摄像机向依据逻辑的数字摄像机的方向开展。更高的视频分辨率、图画信号处理、先进的视频剖析、多摄像体系和数字视频紧缩的开展趋势推进了这一改变。其结果是,在视频监控摄像机和数字视频录像机(DVR)规划中呈现了新的应战,包含增加运用 CMOS 传感器、网络 IP 摄像技能、增加体系的集成功用、更小尺度的外形因子、选用先进的编解码器以及增加 DSP 功用。

因为视频监控 / 安全商场的多样性和竞争性,制造商往往很难在他们自己的产品中增加差异化的功用,使其产品有别于竞争对手的产品。因而,类似的摄像机和 DVR 产品十分遍及。可是,上面说到的趋势为视频安全 / 监控原始产品制造商发明晰新的时机,能够完成产品的差异化。

满意这些运用的要求需求额定的处理才能。现在的数码摄像机运用 DSP 芯片、专门的 ASSP 或 ASIC 来供给处理功用,但这些计划存在一些应战。选用 DSP 芯片常常会呈现功用瓶颈,因为这些芯片通常用串行办法处理图画信号处理使命。ASSP 或许供给更多的功用,但往往是以规划的灵敏性为价值。ASIC 有更多的功用优化,但产值不够大,无法验证 ASIC 开发所需的费用和时刻。规划人员需求一种灵敏的办法,针对不同的细分商场供给从低端摄像机 /DVR 到高端运用所需的核算才能。

完成计划的挑选

视频监控体系可分为两大类:摄像体系和 DVR 体系。摄像体系可整合单个摄像机或多个摄像机。有些体系则整合了 DVR 与单个摄像机或多个摄像机。

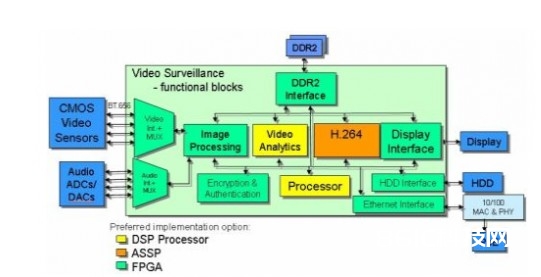

图 1:多摄像机的 DVR 视频监控体系框图。

图 1 是一种通用的多摄像机的 DVR 视频监控体系。视频源来自 CMOS 视频传感器、CCD 视频传感器或模仿视频源。专有的视频接口将输入视频流通换成一般的格局,然后对不同的视频流(以及音频)进行多路复用,在图画信号处理单元进行预处理。视频预处理的意图是下降噪声和消除像素缺点。

视频剖析技能运用于检测在预界说画面中的运动。这个运动检测输出可削减所需的存储容量。在一些视频监控运用中,视频剖析是必需的,如人 / 车计算、轿车的车牌号码辨认和 / 或人脸辨认。

一个典型的具有多个摄像机视频源的视频监控体系总是会生成许多的数据,因而削减所需的存储容量十分重要。MPEG-4、H.264、和 MJPEG 被用来削减所需的存储容量。H.264 是一种针对视频监控运用的盛行紧缩算法,因为它能以适当低的比特率(只要 MPEG-2 或 MPEG-4 第 2 部分一半或更低的比特率 )供给杰出的视频质量的功用。

经过紧缩后的数据经过硬盘驱动器接口存储至视频存储服务器,或经过以太网网络发送。视频数据传送到显示器之前通常是取自硬盘驱动器,并经过了解码以及一些图画后处理,如缩放、颜色空间转化或掩盖运用。通常情况下,存储器接口(如 DDR2)是用来存储视频帧。此外,某些体系要求视频内容的实时加密以确保安全和源 / 用户身份验证。最终,需求用处理器操控和协调 / 排定各种不同的使命。

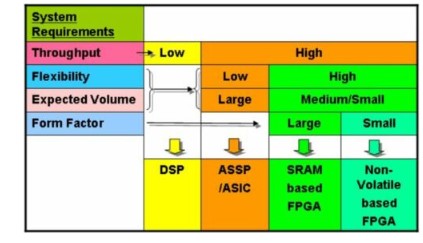

图 2:依据吞吐量、灵敏性、批量和形状因子要求进行挑选的过程。

图 2 说明晰体系的要求,如吞吐量、灵敏性、估计批量和形状因子是怎么推进不同的完成技能和器材的。关于低数据吞吐量的要求,DSP 处理器是最节约本钱的器材。可是,产品寿数期间的估计批量以及硬件的灵敏性会大大响规划者在 ASIC/ASSP 和 FPGA 器材之间作出挑选。假如是硬件灵敏性低的体系要求和估计有大的批量,规划者则喜爱于 ASIC/ASSP 处理计划;而关于硬件灵敏性高的体系要求和较小的预期批量,规划者喜爱 FPGA 处理计划。常见的小型视频监控摄像机有小尺度的要求,规划者喜爱选用非易失性 FPGA ,因为它们不需求额定的外部非易失性装备存储器材。

体系集成组合了不同器材的优势:DSP 处理器有时集成了 ASSP IP 模块,ASSP/ASIC 有时集成了处理器,FPGA 有时集成了硬处理器和硬 IP 核。

关于视频监控体系(图 1),因为这些使命的时序性质,用 DSP 处理器能够有用施行视频剖析功用和处理器块。可是在有些情况下,FPGA 的加快功用有助于进行一些视频剖析功用,如运动检测、面部辨认等。

如图 1 所示的 H.264 编码器是一个要求高吞吐量、硬件灵敏性低、大且杂乱的功用块,通常是用 ASSP 或 ASIC 来完成,以取得小尺度的处理计划。

可是 ASIC 和 ASSP 带来了昂扬的非重复性工程费用本钱,除非批量十分大。假如只要一小部分用户运用特别的功用模块,那么 FPGA 处理计划可供给更好的报答。关于 ASIC 和 ASSP,这些器材有限的功用和固有的不灵敏性,不允许在规划完成后依据商场的要求改善或增加新的功用。FPGA 却能供给广泛的功用和高度的灵敏性。

具有下列要求的视频监控体系模块将获益于 FPGA 的灵敏性:(1)这视频和音频接口以及多路复用器需求硬件的灵敏性,以支撑不同的摄像机和不同数意图摄像机。(2)DDR 接口有必要支撑不同的存储器总线宽度和不同的 DDR 规范。(3)支撑各种图画信号处理算法(二维 FIR 滤波器、二维中值滤波器、缩放、边际检测、伽玛校对、alpha 混合、白平衡、镜头暗影校对、缺点像素校对、去马赛克、逐行扫描,五颜六色空间校对等),在一个特定的视频监控摄像机施行计划中或许需求各种算法的子集。这些算法结构的有用完成取决于吞吐量的要求,而吞吐量的要求又取决于体系中摄像机的数量和视频规范采样率。(4)在视频监控摄像体系中并非总是需求硬盘驱动器接口和以太网接口,但可作为挑选计划。(5)并非总是需求显示器接口,当需求它时,有许多不同的能够完成的显示器接口可供挑选。(6)只在某些体系中需求加密和认证。依据不同视频格局的不同的吞吐量要求,以及在一个特定的监控体系中不同的摄像机数量,最佳加密和认证体系或许需求不同的尺度最优的完成架构。

许多网络 IP 摄像机受到了十分紧凑的外形、功耗和本钱的限制,特别是嵌入式摄像机 /DVR 体系。选用非易失 FPGA 作为一种处理计划能处理这些问题,并取得 FPGA 的传统优势。

运用 FPGA 完成产品差异化

选用 FPGA 完成视频监控体系具有许多长处,包含 FPGA 加快 DSP 处理的功用。非易失性 FPGA 能够使 FPGA 在视频监控摄像体系完成中更具吸引力,特别是对移动 / 交通运输体系中运用的嵌入式摄像机 /DVR 体系来说。这些体系对便携性、功耗和电路板面积有严厉的要求。

这些运用对灵敏性和可扩展性也有很高的要求,但条件是不能下降对功耗、电路板面积和便携性的要求。例如,一些网络 IP 摄像体系有多个摄像机和传感器,即便电路板面积十分有限,也有必要供给多个视频流的通道。其它网络 IP 摄像机往往选用十分小的外壳,电路板挨近 MicroSD 卡的巨细,这种体系的原始设备制造商所面对的应战是竭尽或许少的芯片完成多个体系,一起还能满意功用、外形和低功耗的要求。

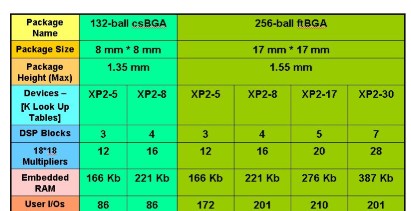

非易失性 FPGA 处理计划,如 LatticeXP2 器材系列把依据 SRAM FPGA 的功用和灵敏性,与非易失 Flash 技能固有的长处结合在一起。LatticeXP2 系列在安全和监控运用方面有许多特色,包含该芯片支撑 DDR/DDR2、针对低本钱显示器的 7:1 LVDS 接口以及 18×18 位乘法的 DSP 模块,这些对在视频监控运用中常常需求的图画信号处理功用特别有用。当 LatTIceXP2-5 和 LatTIceXP2-8 器材与低本钱芯片级封装在一起时, LatTIceXP2 非易失 FPGA 器材系列为原始设备制造商供给许多价值,特别当规划紧凑的网络 IP 摄像机时。

图 3:LatTIceXP2 非易失器材系列具有低本钱的封装。

本文小结

关于许多的各种视频监控摄像机和 DVR 的运用,FPGA 所具有硬件灵敏性、并行处理才能以及零非重复性工程费优势。选用非易失 FPGA 不再需求外部引导芯片 PROM,能够构建一个供给瞬时发动功用的单芯片处理计划。带有片上密钥存储并支撑内置的 AES 128 位加密技能的特性为维护 FPGA 编程位流、避免外部篡改供给了安全保证。许多安全摄像体系处理计划,包含嵌入式摄像机 /DVR 体系,都能从传统的依据 SRAM 的 FPGA 中获益,但当功耗、电路板面积、本钱和集成度特性十分重要时,非易失 FPGA 是一个更具吸引力的代替计划。

责任编辑:pj