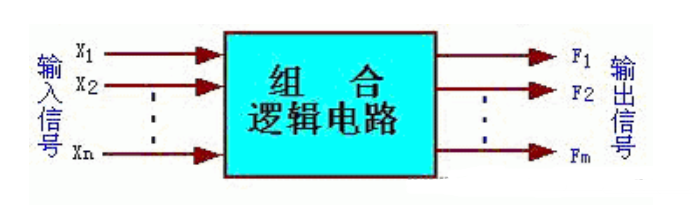

1,什么是组合逻辑电路?

逻辑电路在任何时间发生的安稳的输出信号只是取决于该时间的输入信号,而与曩昔的输入信号无关,即与输入信号效果前的状况无关,这样的电路称为组合逻辑电路。

上图给出了一个典型的数字逻辑电路模型,其间的输入信号为X={X1,。..,Xn},Y={Y1,。..,Yn}为对应的输出信号,输入与输出的联系能够表明为:Y=F(X)。

2,组合逻辑电路有哪些特色?

组合逻辑电路具有两个特色:

(1)。由逻辑门电路组成,不含有任何的回忆元件;

(2)。电路是单向传输的,电路中不存在任何反应回路。

3,怎么描绘组合逻辑电路?

(1)真值表;

(2)逻辑表达式

(3)逻辑门电路图

(4)卡诺图

(详细描绘略)

4,各种描绘之间彼此转化联系?

(1)真值表——逻辑表明

(2)逻辑表达式——逻辑电路图

(3)逻辑电路图——真值表

(详细描绘略)

5,怎么运用verilog描绘组合逻辑电路,及留意事项?

(1)运用assign描绘组合逻辑电路;

在verilog HDL,用assign描绘的部分都是组合逻辑电路,下面临assign做扼要的介绍:

assign:接连赋值句子是Verilog数据流建模的根本句子,用于对线网进行赋值,等价于门级描绘,然而是从更高的笼统层次对电路进行描绘。assign语法表明如下:

continuous_assign ::=assign [drive_stength] [delay] list_of_net_assignments;

list_of_net_assignment :: =net_assignment {, net_assignment}

net_assignment :: +net_lvalue =expression

drive_strength默以为strong1,strong0。

留意接连赋值句子只能对线网进行赋值,即等式左面一定是线网数据类型,右边能够是恣意的数据类型。

(2)运用always描绘组合逻辑电路;

always不只能够用来描绘时序逻辑电路,也能够用来描绘组合逻辑电路,首要差异在于灵敏列表和赋值方法。这儿只介绍always在组合逻辑电路中的运用。

1)在灵敏列表中运用电平灵敏事情,而不必边缘灵敏列表;

2),为变量赋值运用堵塞赋值,而不必非堵塞赋值;

3),在always块内被赋值的变量有必要为寄存器型变量。

(3)运用门级原语描绘组合逻辑。(详细描绘略,可参阅verilog相关书本)