ADAU1472相关信息来自ADI官网,详细参数以官网发布为准,ADAU1472供给信息可在查IC网查找相关供给商。

产品概况

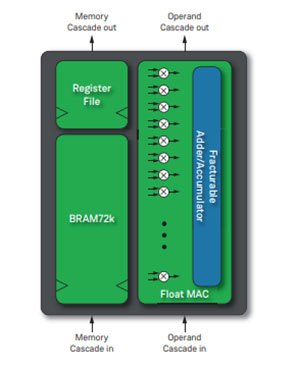

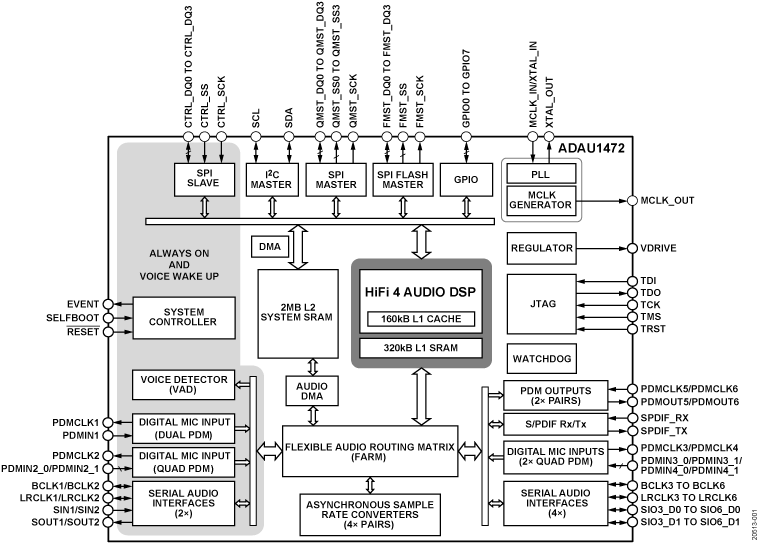

ADAU1472 是一款高质量 SigmaDSP® 数字音频处理器,装备大型内部存储器,能够进行高效音频源别离、远场语音捕获、语音处理、深度学习和高档音频信号处理。该处理器将高度优化的 Cadence® Tensilica® HiFi® 4 音频/语音处理器与 ADI 公司的自定义数学加快指令扩展和灵敏的输入输出架构结合在一起。HiFi 4 处理器支撑每周期四个 32 位 × 32 位乘数累加器 (MAC),装备 72 位累加器、双 64 位存储器负载和本机电气与电子工程师学会 (IEEE) 单精度浮点乘法器。

ADAU1472 处理器具有高达 270.336 MHz 的功能,支撑低推迟逐样本音频处理和并行逐块处理范式。整数锁相环 (PLL) 和灵敏的时钟发生器硬件可一起生成多达 15 个音频采样速率(8 kHz 至 192 kHz)。这些时钟发生器,再加上板载异步采样速率转换器 (ASRC) 和灵敏的硬件音频路由矩阵,可大大简化结构杂乱音频体系的规划。

HiFi 4 数字信号处理器 (DSP) 内核具有以 DSP 内核时钟速率运转的 480 kB L1 存储器,其间包含 256 kB 数据随机存取存储器 (RAM)、64 kB 指令 RAM、128 kB 数据高速缓存和 32 kB 指令高速缓存,别的还有以二分之一的 DSP 内核时钟速率运转的 2 MB L2 体系静态随机存取存储器 (SRAM)。该处理器还支撑 2 GB 的外部闪存,用于存储大型数据表和自引导代码。

双片内电源域可完成低功耗运转,包含以 IOVDD 作为仅有有用电源,经过灵敏的音频路由矩阵路由音频的才能。可装备的语音检测硬件能够在低功耗状态下运转的一起检测人类语音的开端,并能够生成内部 DSP 和外部唤醒信号。

ADAU1472 包含高度可装备的串行端口、Sony/Philips 数字接口格局 (S/PDIF) 接口以及多用途输入/输出引脚,可衔接各种模数转换器 (ADC)、数模转换器 (DAC)、数字音频套件、放大器和操控电路。该套件还可直接与多达 14 个脉冲密度调制 (PDM) 输出麦克风相连,由于它包含专门为此意图规划的集成式抽取滤波器。装备集成式内插滤波器的 PDM 输出能够直接衔接到 PDM 输入 D 类放大器。

该处理器具有两个串行外设接口 (SPI) 总线主操控端口,答应套件与多个 SPI 兼容套件通讯,包含支撑单、双和四输入/输出运转。此外,SPI 闪存端口能够在极低中央处理单元 (CPU) 开支和独立自引导运转的情况下,完成直接存储器映射读取拜访。

ADAU1472 将高功能 DSP 内核、大 RAM 和小外形尺寸组合在一起,适用于代替处理负载相一起功耗更大的大型通用 DSP。

使用

- 远场语音接口套件

- 音频源别离

- 音频嵌入式深度学习

- 商业和专业音频处理

优势和特色

- 270 MHz 32 位 Cadence Tensilica HiFi 4 音频 DSP

- 每周期四通道 32 位 × 32 位 MAC 支撑

- 单一 IEEE 浮点乘法器

- 320 kB L1 SRAM 和 160 kB L1 高速缓存

- 大型 2 MB L2 体系 SRAM

- 加快算术指令扩展

- 可使用完好的开发工具包进行 C/C++ 编程

- 软件与 HiFi DSP 系列兼容

- 低功耗语音检测器一直侦听形式和 DSP 内核唤醒

- 低推迟音频通道

- 4 个立体声异步采样速率转换器

- 用于从晶体生成主时钟的时钟振荡器

- 整数 PLL 和灵敏的时钟发生器

- 用于从 IOVDD 电源发生 1.2 V 电压的片内稳压器

- 6 个具有 32 位数字输入/输出的数字音频输入和输出端口(串行端口),支撑 8 kHz 至 192 kHz 的作业频率

ADAU1472电路图

ADAU1472中文PDF下载地址

ADAU1472下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/ADAU1472.pdf