FPGA现已变得如此本钱效益的,它们越来越多地与微操控器合作运用,以进步整个体系的功率。运用包含添加额定的功用在电路板空间最小,添加功率高效处理的杂乱算法的前端,集合多个外部设备卸载高功用MCU或以习惯现有的规划到新所需的“胶水”逻辑接口要求,FPGA可供给额定的灵活性往往缺少规范的MCU。本文将快速阅读一些最盛行的运用,FPGA和微操控器的“配对”来展现怎么进步体系功率,经过下降功耗,削减电路板空间,进步了处理功用,接口灵活性或许能够明显地进步你的下一个规划。

FPGA成为MCU配套设备

多久的MCU您挑选为您的规划仅仅不太有所有的接口通道,你需求?或许,或许你开端的挑选单片机合适刚刚完美,但一个新的需求来了,因为你最好的客户期望他们的最新规划一些额定的接口。你或许能够运用更杂乱的MCU,而这或许会导致添加明显的电路板空间(因为它只要在高引脚数封装),进步了功率(因为它仅适用于更多的闪存和SRAM比你真实需求的),或许更高的本钱(关于曾经的原因)。

环绕这个难题的一种办法是经过添加一个FPGA周围的MCU规划需求额定的接口。该FPGA能够方便地供给额定的接口,仅仅你需求的,一同约束添加了电路板空间,本钱和功耗。事实上,相关于运用更杂乱的MCU的挑选,您一般终究会用更少的电路板空间,更低的本钱和更少的功率。

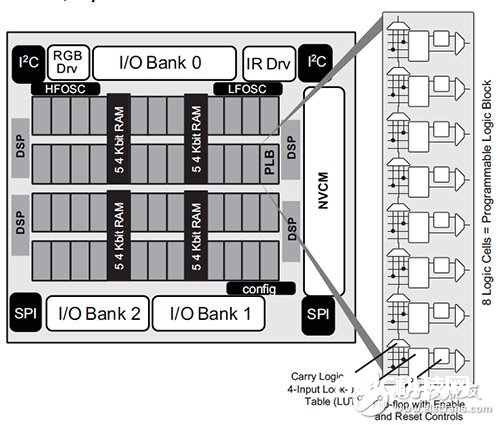

例如,莱迪思的iCE40超低功耗FPGA可供给多达26个信号的IO在一个十分小的2.078毫米由2.078毫米电路板面积,而且因为这些设备经过片上NVM装备,您不需求额定的电路板空间为装备的设备。这些FPGA也有两个专用I2C接口,并用很多的可装备逻辑的两个专用SPI接口的添加为更多的接口,为您的运用程序将需求(直到用完针)。莱迪思ICE5LP1K-SWG36ITR50的框图如图1所示。

莱迪思FPGA iCE5LP的框图

图1:莱迪思FPGA iCE5LP框图。 (莱迪思半导体公司供给)

该设备还具有高达80千位的嵌入式RAM块可用于接口的FIFO缓冲器和因而MCU能够比及整个数据包预备好进行处理。 DSP模块也能够被用来做初级其他数据处理上的原始传感器数据作为先于数据发送到MCU一个预处理进程。当FPGA能够智能地聚合数据中止的MCU之前,极大地下降了MCU电源是或许的。此外,莱迪思的iCE5LP FPGA现已被规划为十分低功率运用仅为71μA中心电源的静态电流。添加更多的接口,简直不需求额定的电路板空间和功耗。看看你最喜欢的微操控器和高引脚数版别之间的当时价格差,然后把它比作莱迪思FPGA iCE5PL1K价格上向Digi-Key的网站,看看有什么本钱节省也或许会供给。

快速呼应FPGA接口的恳求

当运用FPGA伙伴设备能够快速FPGA的服务恳求呼应也可所以重要的。例如,音频接口或许需求具有比传感器数据更高的优先级拜访,因为在音频数据的“失速”有必要防止或用户体会可明显下降。在一般情况下,能够支撑多种中止优先级可协助进步了FPGA的伴侣的实用性,进一步进步体系的全体功用和能效。

有用运用DMA还能够进一步协助卸载MCU和进步工作功率。例如,或许在FPGA能够首要缓冲向上的前处理的原始数据的完好数据分组,以削减需求被存储和发送的音讯的巨细。该FPGA可中止的MCU,并发动DMA传输是将整个邮件到MCU内存。一旦DMA传输完结而且整个音讯预备处理中,CPU能够中止和音讯的高层处理能够开端。

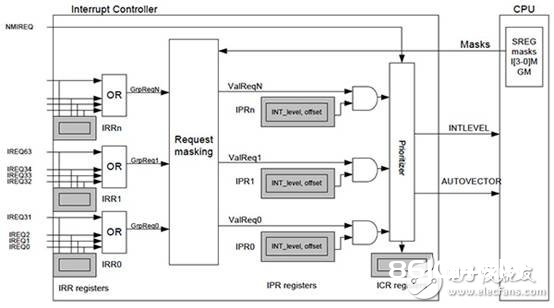

爱特梅尔32位AT32UC3A MCU,例如,具有一个DMA操控器和一个中止操控器,无论是可编程优先级。中止操控器图,对图2的左边所示,具有在右侧一个优先块,在发生中止级别到CPU。优先级块挑选具有最高优先级的中止,如中止优先级寄存器(IPRn)与每个相关联的所界说的中止级字段中止源。因而,较高优先级的源,例如一个实时音频接口,能够被分配的优先级高于低频传感器,或许在I2C端口,用于确保更快的处理。

为爱特梅尔MCU AT32UC3A中止操控器图片

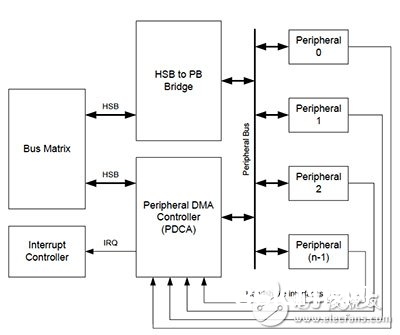

DMA操控器的形象,为爱特梅尔MCU AT32UC3A

图2:中止操控器和DMA操控器框图为爱特梅尔MCU AT32UC3A。 (爱特梅尔供给)

该AT32UC3A MCU的DMA操控器,框图,其间显现在图2右侧的,连接到许多不同的外围设备,在右侧的DMA框图所示。外围DMA操控器优先根据与每个外设相关的DMA通道数的每个外设DMA恳求(外设被分配到一个信道由一个装备寄存器,因而它们是彻底可编程的)与具有较高优先级较低的信道号。这答应DMA传输能够很容易地进行分组,并为最有用的数据传送或许优化。优先级,乃至能够当重新分配算法喜爱一种类型的搬运在另一个的部分。

传感器交融进一步进步体系功率

如前所述,FPGA的可用于经过选用DSP技能来预先处理传感器数据。特别是,FPGA,具有DSP块能够完成许多一同的过滤算法中,例如有限脉冲呼应(FIR)滤波器,无限脉冲呼应(IIR)滤波器和快速傅立叶改换(FFT)。因为这些硬件模块能够操作无论是在串行或并行的方法,你能够构建过滤器根据带宽和功率要求的最佳装备。例如,假如多个传感器输出需求被过滤,在FPGA既能够运用独自的过滤器块,每个传感器(假如带宽要求是足够高),或运用一个单一过滤器块和多个传感器之间多路复用它(假如带宽要求是足够低)。

除了预处理原始传感器数据时,FPGA还能够结合的读数从多个传感器,以智能的方法来进一步卸载的MCU处理要求。传感器“交融”的算法,结合本地多个传感器读数,之前告诉MCU的处理是必需的,能够明显进步体系功率。结合心脏速率,温度,以及排汗读数和比对FPGA内部设置的警报水平的组合,例如,能够供给微操控器与不只仅是原始数据更有价值的信息。

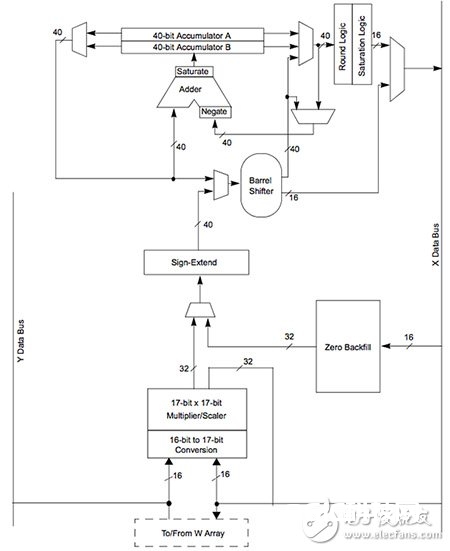

该MCU一般需求做一些数据的处理自己,可是。它不能抛弃一切到FPGA中。走运的是,即便是廉价的微操控器现在DSP的处理才能,而且能够有用地紧缩很多数据。久负盛名的Microchip的PIC MCU系列,例如,具有DSP的家庭成员,如DSPIC 33EP(如DSPIC33EP32MC202),在高达70 MIPS的操作与某些指令履行多达8个操作一次。过滤器的指令能够获益于40位累加器添加定点精度。在DSPIC33EP专用硬件DSP引擎的框图如图3所示。

框图在Microchip的dsPIC33系列MCU

图3:DSP引擎框图在Microchip的dsPIC33系列MCU。 (Microchip的供给)

DSP引擎包含一个17×17乘法器/定标器零回填并签署扩展到创立一个40位的成果。除法运算运用的是19次迭代一个重复循环经过一个独自的硬件除法模块完成的,且是可中止下降最坏情况下的中止推迟。桶式移位器有助于正确地调整数据为40位加法器和双40位累加器。这种丰厚的DSP的处理硬件除了惯例的ALU,供给16位的加,减,和位操作。有了这个广泛的集数据处理硬件,乃至杂乱的操作都能够十分有用地支撑。

的SoC FPGA的硬件加速和根据微操控器的处理

FPGA和微操控器做出这样的好伙伴的FPGA供货商乃至把MCU的伙伴在其设备上。当这些体系级芯片(SoC)的FPGA用作伙伴高端MCU的,更杂乱的功用能够被移动到FPGA。一个常见的比如是用于FPGA来处置许多体系界面,不只与规范外设还与外部存储器。因为的SoC FPGA有明显的片上存储器,微操控器来办理数据缓冲和处理通讯结构和外部存储操控器,你有你需求完成一个完好的通讯信道操控器,桥梁,或聚合碎片。这能够脱离主MCU办理更高水平的功用,例如人机界面(HMI),进程操控,以及服务质量的优化。

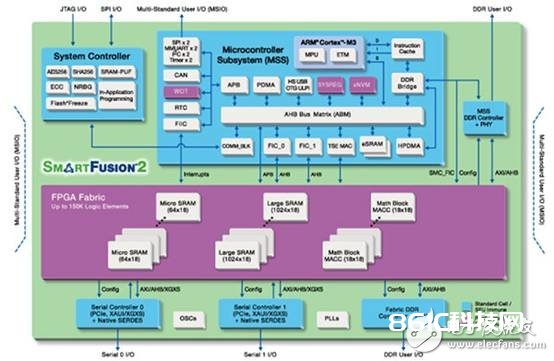

一些的SoC FPGA具有更多的功用,可从主机MCU卸载更是低层次处理。例如,Microsemi的SmartFusion2 SoC的FPGA系列(M2S050-FGG896的框图如图4所示),不只具有完好的ARM Cortex子体系,但其片上闪存NVM和SRAM块明显为MCU的一部分子体系。这些存储器能够与处理器一同运用,作为代码和数据存储,与芯片外的DDR操控器作为大缓冲存储器,并与PCIe和以太网操控器作为先进先出存储。智能DMA操控器能够办理许多数据传输的不中止的处理器。

Microsemi的SmartFusion2 SoC的FPGA的框图

图4:Microsemi的SmartFusion2 SoC的FPGA程序框图。 (Microsemi公司供给)

SmartFusion2的SoC FPGA还具有片上硬件的安全性,可用于维护长途代码更新来自黑客和其他安全要挟。大型片上闪存可用于存储受维护的引导代码,这使得它能够支撑安全发动的操作,即便没有本地安全功用的主机处理器。很多的可编程结构能够从主机操控器供给定制硬件加速,进一步卸载处理。例如,在一个底盘操控体系,可编程织物能够用于DSP的预处理传感器数据,传感器交融组合的电压,电流,和温度读数,马达操控的机箱电扇操控体系的温度,操控台接口,本地确诊监测和操控,或经过PCIe桥接至其他操控平面功用。跟着SoC的FPGA的伙伴实际上或许承当更多的处理比主机,切换一个MCU之间的传统人物作为主角,并仅在非必须辅佐效果的FPGA。

定论

有许多运用,其间的MCU和一个FPGA,配对在一同,能够明显地经由较低功耗,削减电路板空间,进步了处理,或添加的灵活性进步体系功率。了解怎么经过分配这两个设备之间的函数来完成其间的一些改善,或许是在你的下一个规划成功的要害。