导言

现场可编程门阵列(FPGA)的呈现是超大规模集成电路(VLSI)技能和计算机辅助规划(CAD)技能发展的成果。FPGA器材具有集成度高、体积小、能够经过用户编程完结专门运用的特色。这些特色十分合适大学计算机教育中的计算机硬件试验。在计算机硬件试验中,三态电路有着广泛的运用,例如构建一个具有分时同享功用的总线电路就需求用到多个三态电路。传统的试验办法要先画出原理图,然后经过手艺连线各个芯片来树立三态电路。在根据FPGA的硬件试验中,一种办法是运用图形办法,在MAX+PLUSⅡ中画出三态电路图,并编译完结完结三态的功用;另一种办法是直接用VHDL言语编写出三态电路程序,相同需求编译完结完结三态的功用。可是,在MAX+PLUSⅡ环境下,运用三态电路时常会遇到了许多问题,这些问题阻止着用VHDL言语正确运用三态电路的功用。咱们在FPGA运用规划中也发现了类似问题,经过细心的剖析和对多种不同完结办法的测验,最终把握了正确的完结办法,一同也找出了一般办法犯错的原因。

在MAX+PLUSⅡ环境下最常见的三态运用程序及问题

在MAX+PLUSⅡ环境下,由于软件本身供给了三态总线电路的模块,因而能够在VHDL编程时直接调用lpm_bustri模块。下面是一个用VHDL编写的8位单向总线电路的程序片断:

entity tri_bus is

port(a,b: in std_logic_vector(7 downto 0);

aen,ben: in std_logic;

q:out std_logic_vector(7 downto 0));

end tri_bus;

architecture tri_bus_body of tri_bus is

component lpm_bustri

generic(lpm_width:posiTIve);

port (data : in std_logic_vector(lpm_width-1 downto 0);

enabledt: in std_logic:=‘0’;

tridata:inout std_logic_vector(lpm_width-1 downto 0));

end component;

signal temp: std_logic_vector(7 downto 0);

begin

u1:lpm_bustri

generic map(lpm_width=》8)

port map(data=》a,enabledt=》aen,tridata=》temp);

u2:lpm_bustri

generic map(lpm_width=》8)

port map(data=》b,enabledt=》ben,tridata=》temp);

q《=temp;

end tri_bus_body;

以上程序很简略,经过调用lpm中的三态模块,以完结三态输出传输至总线的功用。程序中将两个三态模块的输出衔接在一同,构成一个8位总线,总线输出成果取决于两个三态模块中哪一个的使能信号有用。这段程序理论上不存在问题,可是编译却无法经过!编译器报错,指出信号temp被屡次赋值。

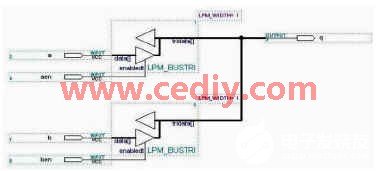

明显,在u1和u2中有两次呈现tridata=》temp,但这关于三态电路来说是答应的,由于三态输出是能够并联的。那么是否由于lpm_bustri模块不能正确完结三态功用呢?咱们首先用图形办法来验证该模块的功用。由于只是验证,这儿只设置了一位的数据输入和输出,如图1,图中a为数据输入端,q为数据输出端,aen为使能端。

图 1

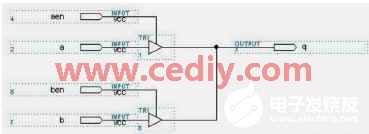

该图形文件成功地经过了编译,并且仿真成果表明,三态功用彻底正确,即便能aen有用,输出为a,使能aen无效,输出为高阻。然后,咱们又用图形办法树立了前面的VHDL程序逻辑,建好的图形文件如图2所示。

图 2

这个图形文件所示逻辑同前面VHDL程序的内容彻底相同。信号q的输出取决于两个使能端中哪一个有用。可是编译仍是犯错,这次指出的过错是两个lpm_bustri的输出tridata衔接在一同了。

从理论上来说,两个三态的输出是能够接在一同的。为了证明这一点咱们不再选用lpm_bustri模块,而是在MAX+PLUSⅡ环境下用图形办法直接画出两个三态元件,然后再将它们的输出衔接在一同,如图3。

图 3

这各图形文件顺畅经过编译!仿真成果也彻底正确,当aen使能有用,q输出为a;当ben使能有用,q输出为b。假如没有两个使能端均无效,输出为三态,假如两个使能端均有用,输出成果为a和b的线与。(由于在实践总线电路中,aen和ben不可能一同有用,所以此种状况并不影响成果的正确性,咱们只需知道这种状况下的输出成果是两个信号的线与就能够了。)

修正后的三态电路运用程序

已然三态电路用图形办法在MAX+PLUSⅡ环境下能够正确完结,那么VHDL程序也应该是能够的。前面编译犯错的程序和电路都是由于用到了lpm_bustri模块,假如不用它程序将怎么修正呢?在这种疑问下咱们改变了思路,修正后的VHDL程序如下:

library ieee;

use ieee.std_logic_1164.all;

enTIty tri_state is

port(a,b :in std_logic_vector(7 downto 0);

aen, ben :in std_logic;

q :out std_logic_vector(7 downto 0));

end tri_state;

architecture tri_state_body of tri_state is

signal control:std_logic_vector(1 downto 0);

begin

control(1)《=aen;

control(0)《=ben;

process(a,b,control)

begin

case control is

when “10”=》q《=a;

when “01”=》q《=b;

when others=》q《=(others=》‘Z’);

end case;

end process;

end tri_state_body;

这段VHDL程序同开始那段VHDL程序表达的功用是相同的,当aen使能有用,输出为a,当ben使能有用,输出则为b,假如不是这两种状况均输出三态。这次经过编译和仿真,功用正确完结了。

剖析不同程序不同成果的原因

为什么开始的VHDL程序和用lpm模块树立的图形会犯错呢?带着这个问题将两个程序进行比照便可找出问题的地点。在修正后的程序中,咱们用了一个control二维数组来操控对输出信号q的赋值,尽管输出信号q也是有两个输入源a和b,可是程序操控了它们赋值的时刻,也便是不可能一同被赋值,所以编译器没有报错。而开始的程序的却呈现temp被屡次赋值,再来看看源程序:

u1:lpm_bustri

generic map(lpm_width=》8)

port map(data=》a,enabledt=》aen,tridata=》temp);

u2:lpm_bustri

generic map(lpm_width=》8)

port map(data=》b,enabledt=》ben,tridata=》temp);

q《=temp;

其间,尽管实践中不可能让三态的两个使能一同有用,可是关于编译器而言,它只能辨认句子的逻辑,在上面那种逻辑下,aen和ben是彻底可能一同有用的(只是是逻辑,只对句子而言)。假如这种状况产生,编译器将无法正确对q赋值,所以报错,提示信号temp被屡次赋值,这彻底是由于编译器谨慎的成果。

在一个编译器中,语法的正确性查看是根据一种规矩和逻辑的,它是适用于一切的言语描绘。尽管三态的输出能够衔接在一同,可是当程序直接将它们衔接在一同的时分(也便是多源赋值的时分),编译器不可能由于程序编的是三态逻辑而经过这种潜在的过错,它的编译原理是根据句子而不是编出来的成果。这样就能够解说为什么简略的元件树立出来的三态输出衔接在一同能够经过编译,而用lpm模块描绘出来的和咱们开始的三态程序描绘出来的三态输出却不能经过编译。由于它们都需求经过编译器的语法查看。而多源赋值又是一种潜在的过错,所以不能经过。那么有些人会不理解,都是图形描绘,为何简略的元件树立能够经过而高档的lpm模块树立却不可?答案是高档的lpm模块也是用言语编写出来的,它也要经过编译器的语法查看。简略的元件树立能够经过是由于在两个使能都树立的状况下,软件能够将输出信号按线与处理,然后避免了抵触和不确定性。那么怎么运用lpm模块完结三态的功用?这就要看怎么运用在详细的运用中了。假如只是需求将两个三态的输出衔接在一同,经过各自的使能端操控输出的话,能够在一个原理图中别离树立两个独自的lpm模块,不要将它们的输出端衔接在一同(不然编译器会报错),然后直接编译,编译经往后能够在装备FPGA的时分将树立的两个lpm模块的输出衔接到同一个管脚上,经过验证,这样在运用中也是能够正常完结三态功用的(由于其避免了在编译前就将输出口衔接在一同而不能经过编译的状况的产生)。

总结

经过以上的剖析和阐明,咱们知道MAX+PLUSⅡ环境下,是能够正确完结三态电路运用的。主要有三种办法:

① 用类似于咱们上面改编出来的程序来完结;

② 用自树立的图形描绘完结;

③ 在装备FPGA时再将不同的三态输出端衔接到同一个管脚上。

需求留意的是在编写程序或许运用软件本身供给的模块树立电路时要了解软件本身或许所调用的模块在编译时是否会引起编译器的抵触。在了解了编译器编译原理后,才干在编写和调试程序时挥洒自如,及时发现和改正问题。

立异观念:本文指出了在MAX+PLUSⅡ环境下运用三态电路常见过错的原因,并指明晰几种正确的完结办法。

责任编辑:gt