看到Intel最近发布了QPI直连FPGA的架构,冬瓜哥回想起几个月前写的一篇文章,现在从头共享给咱们。从中你能够了解为何需求FPGA,FPGA是怎样被衔接到体系里的,怎样被运用的。

闲话少说,今日咱们说一说IBM搞的CAPI,CAPI是OpenPower体系里的一个技能,其意图是让FPGA更好更便利的融入现有的体系。那么现有的FPGA是怎样被运用的呢?不如先说说什么是FPGA,要弄清楚什么是FPGA,就得先说说什么是CPU。可笑,CPU咱们都知道,冬瓜哥这逼格咋降低了?笑而不语。

·通用CPU是怎样运算的?

咱们都知道所谓GPCPU(通用意图CPU),也便是什么都能算,但又什么都算不快的CPU,所以其“通用”,比方Intel x86,AMD x86,Power,PowerPC,MIPS,ARM,DragonSon/GodSon(国产)等。而FPGA便是专门为了某种某类核算而专门优化其内部的逻辑电路的一种专用CPU。GPCPU内部的ALU包括多种运算器比方加减乘除以及逻辑(比方xor,and,or,not)运算以及整数和浮点运算,咱们开始菜单核算器,算加减法,代码指令便会把对应的数据导入到CPU的寄存器,CPU收到之后便会将操作数输入到运算器的输入端,并在下一个时钟周期获取到核算成果并输出到寄存器,然后写回到主存。当然,GPCPU内部花费了很多的资源(逻辑电路)去做优化,包括缓存办理、流水线、多发射、分支猜测、乱序履行等等,一条指令要终究得到履行,都要经过这些关卡的一层层处理,所以,关于那些遵纪守法的代码(比方,顺着来没有任何判别跳转)来讲当时延无疑会添加,可是现在跟着事务越来越杂乱,运用程序的判别条件越来越多,所以这些优化会添加终究功能,尽管时延相对上进步了,可是功能绝对上是添加了,因为假如误判了一个分支,那么整个流水线现已预读入的代码就会被冲刷走从头读入,这个时延反而会更大。

有人问了,我不翻开核算器,就运转个QQ,莫非还要算加减法么?假如没有什么加减乘除运算,CPU运转QQ到底是运转了些什么东西?这问题问得好,问的逼格高,一般人是底子不去想QQ运转时分底层都做了什么的。其实GPCPU大多时分还真没有在算加减乘除,而更多地是做和谐作业了,也便是把内存里某段数据读出来,稍加改动或许底子不动,又写到内存其他地方去。这不闲的么,CPU就干这个?是的。比方QQ要发送一句话给某个老友,其需求调用TCP协议栈顶上的soket API,后者便是一段常驻内存的OS内核代码,那么QQ.exe怎么将这句话传递给这段代码?QQ.exe会让CPU把这句话在当时内存的地址告知socket API代码,其会将这个地址以及其他参数写入到某个CPU寄存器,对应机器指令便是“mov 内存地址寄存器A”相似这种,然后QQ.exe调用socket API,对应机器指令便是“call socket API的内存地址”,CPU就会把QQ.exe当时的地址暂存起来以便后续回来持续履行(这叫压栈),然后再跳转到socket API地址来履行socket代码(从内存中该地址读出socket代码履行),socket代码履行之后,会在CPU寄存器内发现之前传递过来的参数(要发送数据的内容等),然后依照这个参数向下调用TCP协议栈将数据打包,分段,贴上IP标签,终究调用以太网卡驱动程序,调用进程与上述相似,然后发送到网卡。这个进程,在主途径上,加减乘除运算并不是有必要的,可是在辅途径上,比方程序需求记住当时发送了多少内容了,TCP协议栈也要记载当时发送了多少个分段了,这些就需求CPU做加法操作,来计数;别的,在遇到if代码的时分,cpu会比对多个输入条件,对应机器指令是comp(比较)以及jmpz/jmpnz(遇零跳转/非零跳转)等此刻会用到减法器或许比较器,这恐怕是通用场景下用得最多的ALU运算器了。所以,上述这个进程,底子就不是一个大运算量的进程。可是你假如去听mp3,解码RMVB电影,那就需求大运算量了,这些场景也是专用场景。

·专用FPGA又是怎样核算的?

通用CPU做通用场景的代码履行,很强,什么都精干,听着歌聊着QQ做着ppt,再加上个SSD,体会流通的感觉。可是让你算一算分子动力学,某个分子内的原子是怎样运动的?算一算人脸辨认?搞搞查找?那通用CPU就歇菜了。此刻,加减乘除、逻辑、整数、浮点通通一同上,通用场景下运用份额较少的这些ALU,可是专用场景下,这些ALU反而不行用了,一个是数量太少,一个是位宽太低。比方XOR运算器,假如位宽只要64bit,每个时钟周期只能将两个64bit做XOR,假如我要XOR 两份1GB的数据,就需求1GB/64bit=?(自己算)个时钟周期,才干算完。此刻,专用核算就派上用场了,也便是所谓的“硬加快”。整体来讲硬加快有4种完成手法:露点、加宽、并行、直译。露,便是直接把终究的运算单元给露出来,抛掉那些什么分支猜测等流水线过程;宽,便是把运算器位宽直接加大,一个周期多算一些数据;并便是把多种分支直接并行检测,也便是把比较器/减法器直接并行化,成果相OR或许AND,来判别后续途径;直译便是把多种条件直接用译码器做出来,一个周期输出成果。一切这些都需求电路层面的改动,这就产生了FPGA现场可编程门电路阵列。FGPA内部便是一堆的直译表(DRAM,用户自己写好逻辑然后输入进去),再加上一些外围接口,和一些固定的算法器材比方Flash操控器常用的LDPC硬核。NIC、存储IO卡、防火墙、路由器等,内部都运用了应加快,比方网卡收到一个以太网帧,其需求解析帧头,这种作业假如交给GPCPU的话,那就太慢了,来,先从内存读入代码看看要让爷我干点啥?译完了码,来,进流水线等着吧,我顺便去做个分支预判,找一找前史预判数据,下一位!进了流水线后,亲,你先排在后面吧因为你要的资源和他人有抵触。终究操作数抵达ALU,尼玛,就这么点位宽?小爷这吨位最少得1Mbit位宽才放得下!亲,下次再来吧,来之前先进闸刀给你闸成多个64bit,然后每次算64bit吧。。而硬加快直接把这个帧载入寄存器,其间电路直接导向各个译码器,直译出下一步的操作,比方需求比对ALC,那么就多个方针地址/源地址并行比较一个周期输出,这样才干确保速度。

·专用FPGA怎样与体系对接?

现在的FPGA都是运用PCIE与host通讯的,也便是做成一张PCIE卡查到主板PCIE槽上。主程序经过驱动程序,将需求运算的数据指针告知FPGA,然后FPGA从主存DMA读取待核算数据然后核算,算完后DMA回主存并告诉主程序。

·多中心多CPU体系以及PCIE设备

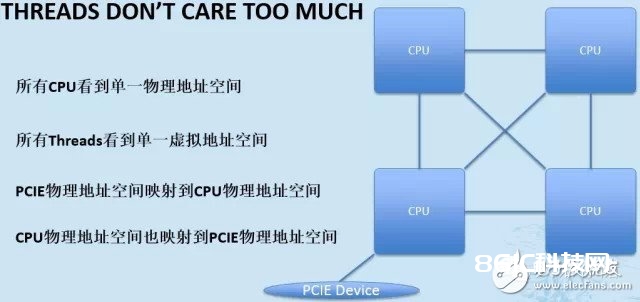

一切CPU看到单一物理地址空间,一切Threads看到单一虚拟地址空间,PCIE物理地址空间映射到CPU物理地址空间,CPU物理地址空间也映射到PCIE物理地址空间。

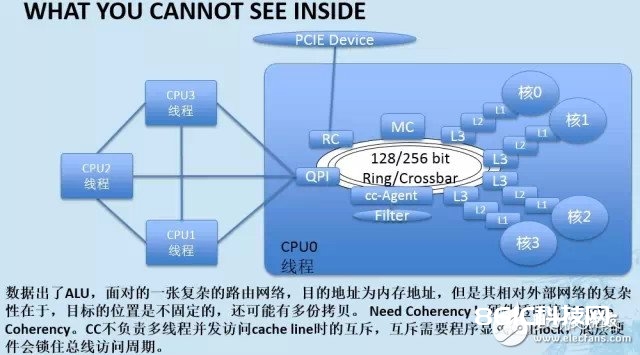

数据出了ALU,面临的一张杂乱的路由网络,意图地址为内存地址,可是其相对外部网络的杂乱性在于,方针的方位是不固定的,还可能有多份复制。Need Coherency!硬件通明搞定Cache Coherency。CC不担任多线程并发拜访cache line时的互斥,互斥需求程序显式宣布lock,底层硬件会锁住总线拜访周期。

·PCIE设备怎么与CPU交互?

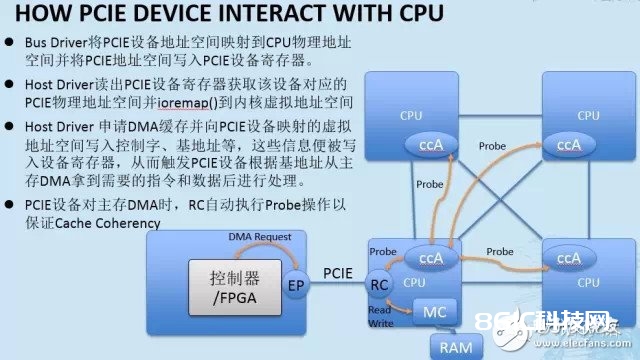

1.BusDriver将PCIE设备地址空间映射到CPU物理地址空间并将PCIE地址空间写入PCIE设备寄存器。

2.HostDriver读出PCIE设备寄存器获取该设备对应的PCIE物理地址空间并ioremap()到内核虚拟地址空间

3.HostDriver 请求DMA缓存并向PCIE设备映射的虚拟地址空间写入操控字、基地址等,这些信息便被写入设备寄存器,然后触发PCIE设备依据基地址从主存DMA拿到需求的指令和数据后进行处理。

4.PCIE设备对主存DMA时,RC自动履行Probe操作以确保CacheCoherency

·当时交互方法存在的缺乏

1.履行途径长并且全软件参加:运用call-》传输协议栈(如有)-》Host驱动-》PCIE设备-》DMAà中止服务-》Host驱动-》传输协议栈(如有)-》运用buffer

2.PCIE设备与CPU看到不同的物理地址空间,RC进行映射和转化。驱动程序请求内存之后得用pci_map_single()映射成PCIE物理地址。

3.用户态程序有必要自动从内核地址空间mmap()才干够直接与PCIE设备DMA互传数据。用户态程序有必要区别不同的地址段。

·CAPI1.0版别怎么处理当时的问题?

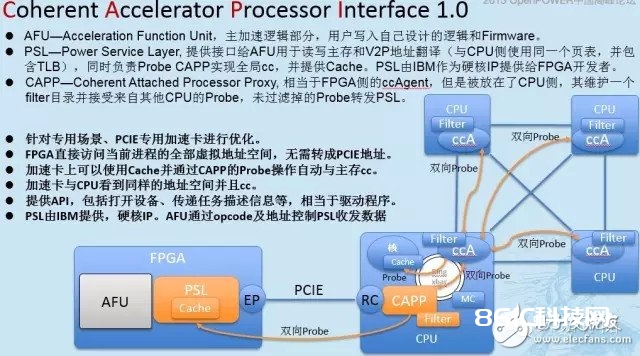

AFU—AcceleraTIon FuncTIon Unit,主加快逻辑部分,用户写入自己规划的逻辑和Firmware。

PSL—Power Service Layer, 供给接口给AFU用于读写主存和V2P地址翻译(与CPU侧运用同一个页表,并包括TLB),一起担任Probe CAPP完成大局cc,并供给Cache。PSL由IBM作为硬核IP供给给FPGA开发者。

CAPP—Coherent Attached Processor Proxy, 相当于FPGA侧的ccAgent,可是被放在了CPU侧,其保护一个filter目录并承受来自其他CPU的Probe,未过滤掉的Probe转发PSL。

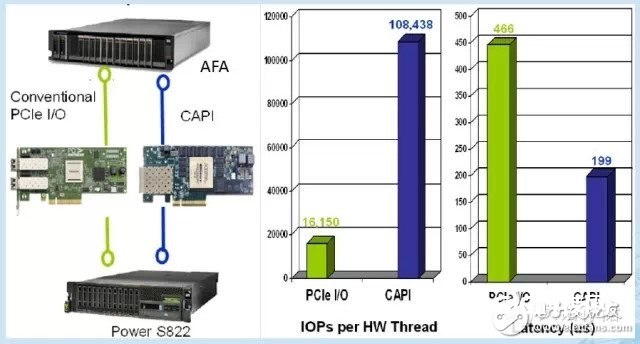

·功能能进步多少?

上图是IBM自己的一个测验,运用CAPI enabled FC HBA(根据FGPA),与传统方法比较照,功能提高非常大,我没有是测过,对其底层的机制有点置疑,FPGA后端相同运用传统的FC操控器以及驱动程序衔接AFA阵列,这与直接把FC卡插在主机上比较,添加了一层CAPI,只会时延更高,可是成果却是时延下降,因为IBM并没有供给更多信息,所以这儿欠好判别。